环境配置

编程方式为原理图输入,目标芯片为cycloneIVE系列的EP4CE11529C7, 基于Quartus13.1的开发环境

实验过程

新建工程以后,在电路图中放置两个输入端、两个输出端以及一个AND2的与门和一个XOR或门,并按上图方式连接

将此电路图保存为“half_adder”(半加器)并编译,编译成功才能使用

选中半加器,在File->Create/Update->Create Symbol Files for Curren Files中将此半加器定义为一个元件符号并存盘,接下来再电路图的工具栏中应该能找到half_adder这一元件

新建一个电路图,依序放置三个输入端、两个半加器、一个CR2的元件、两个输出端,并按图连接好电线

保存此电路图为full_adder(全加器)并编译,编译完成便可进行下一步烧录

将FPGA开发板连接好电源和电脑USB借口,开机以后点击quartus里的烧录按钮,出现以下界面

在Hardware中找到USB-Blaster(如果没有则可能是驱动问题,在计算机->设备管理器->USB-Blaster中手动添加驱动,定位到quartus目录drivers文件夹下的USB-Blaster文件夹)

最后一步进行烧录,按图上顺序操作以后等待右上角进度条到100%便可在开发板上观察到程序演示

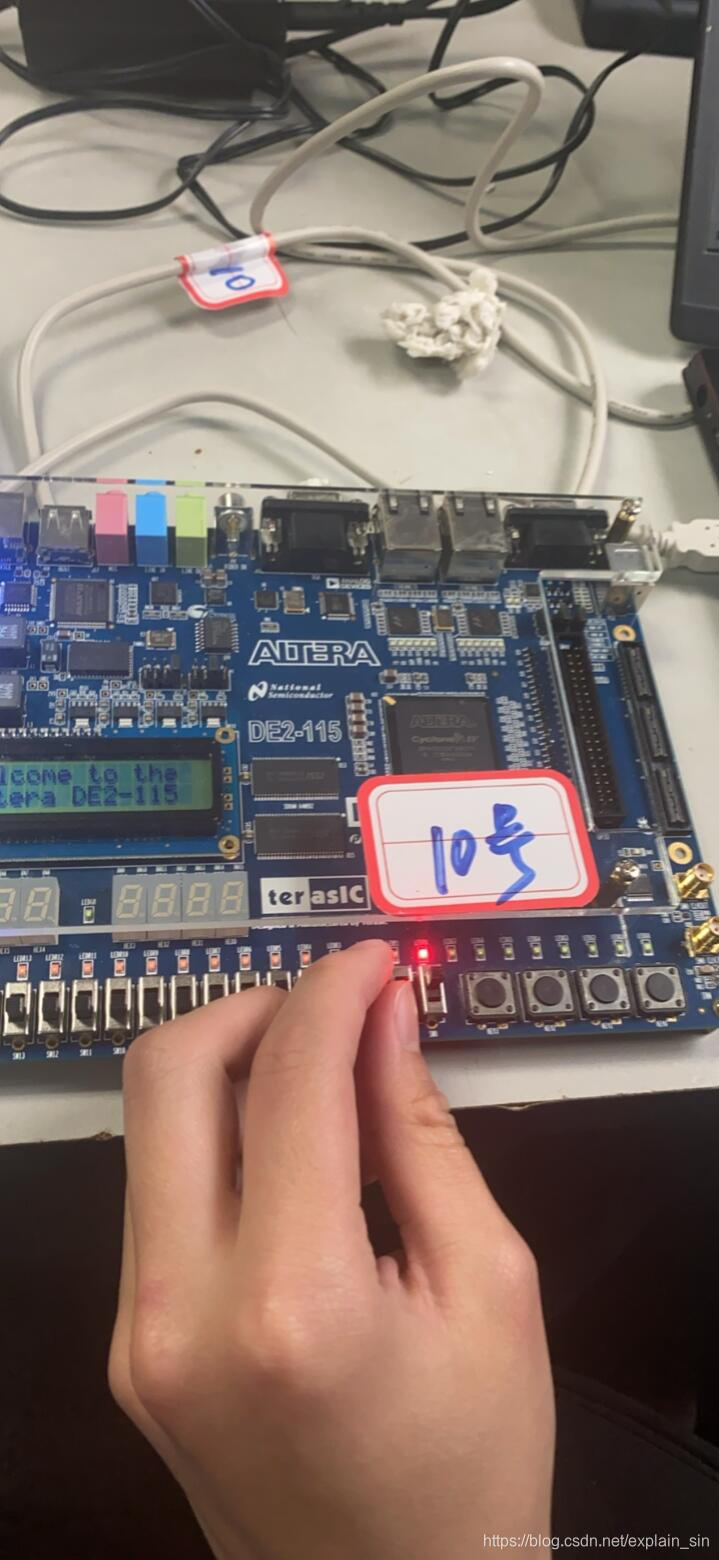

程序演示结果

此全加器功能简单,主要是计数功能,当一个输入端为1时,指示灯亮为01(由于这里的引脚绑定,读数要从左往右看);当两个输入端为1时,指示灯为10;当三个输入端为1时,指示灯11;三个输入端都是0,指示灯00

本文详细介绍了如何在Quartus 13.1环境中,使用CycloneIV EP4CE11529C7芯片设计半加器和全加器。从新建工程、电路设计、元件符号创建,到烧录过程和最终功能演示,为初学者提供了一步到位的开发教程。

本文详细介绍了如何在Quartus 13.1环境中,使用CycloneIV EP4CE11529C7芯片设计半加器和全加器。从新建工程、电路设计、元件符号创建,到烧录过程和最终功能演示,为初学者提供了一步到位的开发教程。

4811

4811

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?