高速先生成员--姜杰

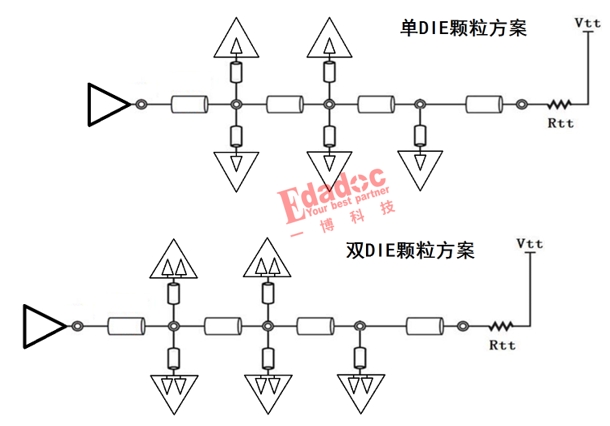

地址信号一驱五的DDR4拓扑很常见,可是,一驱五拓扑还要求单DIE、双DIE颗粒兼容的你有见过吗?

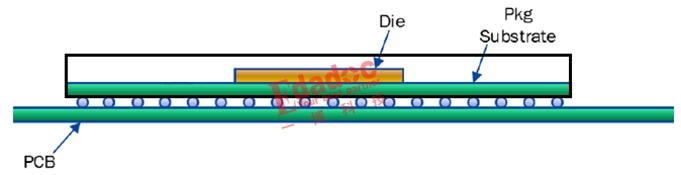

案例开讲之前,先简单介绍下DIE,英语学的好的同学都知道这个词的意思不太吉利,不过,芯片设计领域的DIE(裸晶)是另外一个意思,它通常指的是芯片内部一个单独的晶圆区域,包含了芯片的一个或一组完整功能单元,大致可以理解为去掉了封装和引脚的芯片。芯片根据功能和规模由一个或多个DIE构成。

了解了芯片DIE的概念,相信各位已经能意识到我们这个案例兼容双DIE颗粒的难度了,没错,相比于单DIE方案,双DIE方案相当于接收端数量直接翻番,信号路径更加复杂,负载也更重,信号质量的恶化基本可以预见。

让高速先生略感欣慰的是,客户也认可双DIE颗粒的实现难度,因此,可以在保证单DIE颗粒3200Mbps速率的基础上,再考虑兼容双DIE颗粒。

遇到如此善解人意的客户,高速先生丝毫没有放松,首先对一驱五拓扑的单DIE颗粒方案进行优化。熟悉高速先生文章的同学一定还记得,对于一驱多Clamshell拓扑而言,反射会在靠近主控芯片处的近端颗粒处积累,因此,我们会重点关注信号质量较差的近端颗粒。原始眼图确实不尽如人意,无论是信号质量还是时序,都满足不了协议要求。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?