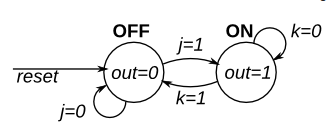

This is a Moore state machine with two states, two inputs, and one output. Implement this state machine.

This exercise is the same as fsm2, but using synchronous reset.

module top_module(

input clk,

input reset, // Synchronous reset to OFF

input j,

input k,

output out); //

parameter OFF=0, ON=1;

reg state, next_state;

always @(*) begin

// State transition logic

state <= next_state;

end

always @(posedge clk) begin

// State flip-flops with synchronous reset

if(reset == 1)

next_state <= OFF;

else case (next_state)

OFF: if(j == 1)

next_state <= ON;

else

next_state <= OFF;

ON: if(k == 1)

next_state <= OFF;

else

next_state <= ON;

default: next_state <= OFF;

endcase

end

// Output logic

// assign out = (state == ...);

assign out = state == ON ? 1'b1 : 1'b0;

endmodule

博客围绕一个具有两个状态、两个输入和一个输出的摩尔状态机展开,要求实现该状态机,且此次练习与fsm2相同,但采用同步复位方式。

博客围绕一个具有两个状态、两个输入和一个输出的摩尔状态机展开,要求实现该状态机,且此次练习与fsm2相同,但采用同步复位方式。

239

239

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?