首先要明白的是:序列检测器的作用就是将一个指定的序列从一个数字码流中提取出来,这篇博客要检测的是一个‘11001101’序列。

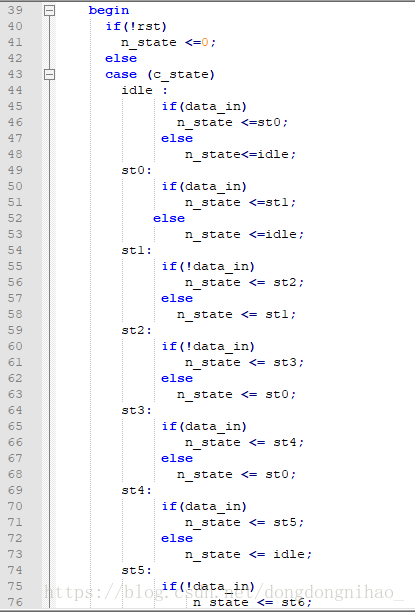

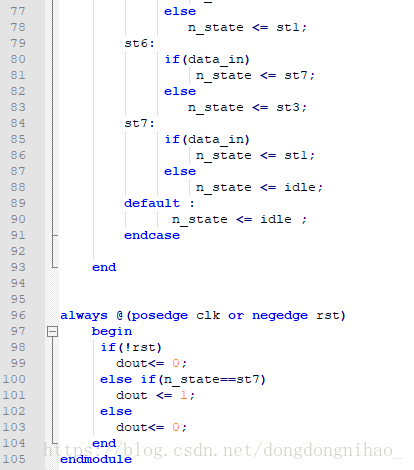

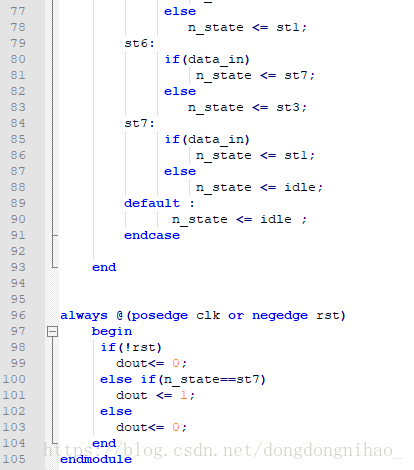

程序中的data_in数据流输入,当状态为st7的时候认为检测到了‘11001101’序列。输出为1,否则为0。

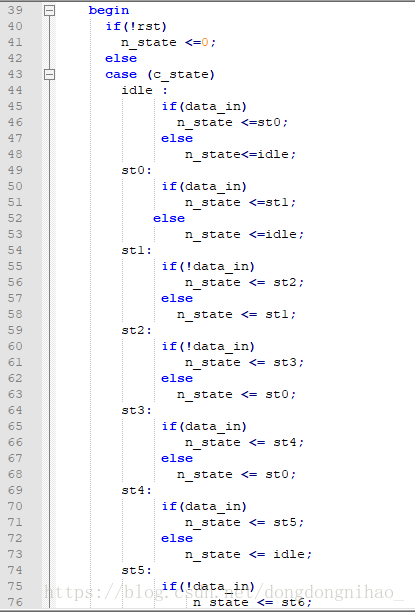

序列检测采用三段式状态机设计,三段式状态机将时序逻辑和组合逻辑分开,把状态和输出单独列开,方便检查和维护。

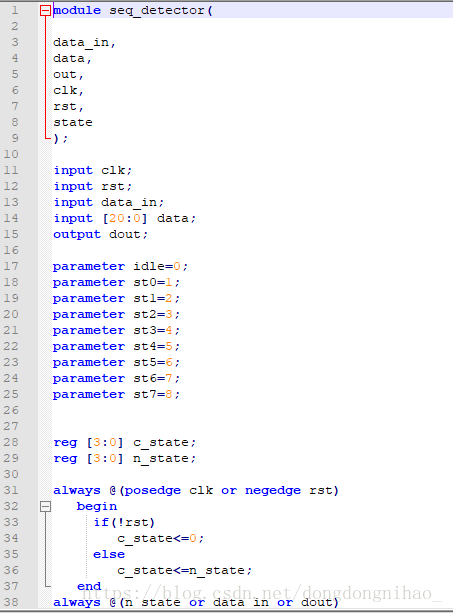

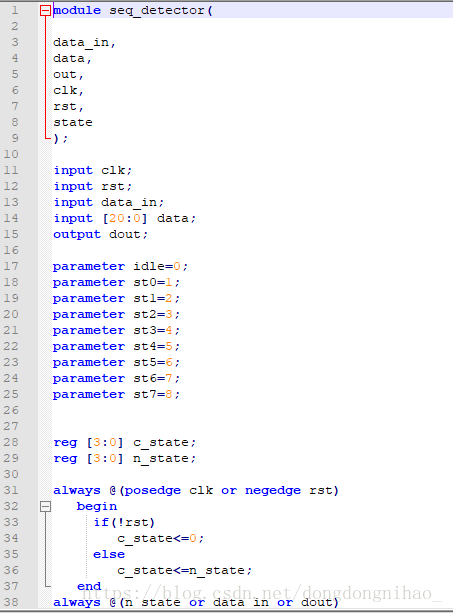

序列检测代码:

首先要明白的是:序列检测器的作用就是将一个指定的序列从一个数字码流中提取出来,这篇博客要检测的是一个‘11001101’序列。

程序中的data_in数据流输入,当状态为st7的时候认为检测到了‘11001101’序列。输出为1,否则为0。

序列检测采用三段式状态机设计,三段式状态机将时序逻辑和组合逻辑分开,把状态和输出单独列开,方便检查和维护。

序列检测代码:

524

524

4053

4053

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?