名称:可配置输入端口数和数据位宽的多路选择器设计Verilog代码VIVADO仿真(文末获取)

软件:VIVADO

语言:Verilog

代码功能:

可配置输入端口数和数据位宽的多路选择器设计。使用Verilog VHDL语言设计数据位数在1-32之间变化、输入端口数在2/4/8/16四个数中变化的多路选择器 muxnto1。利用仿真验证设计。

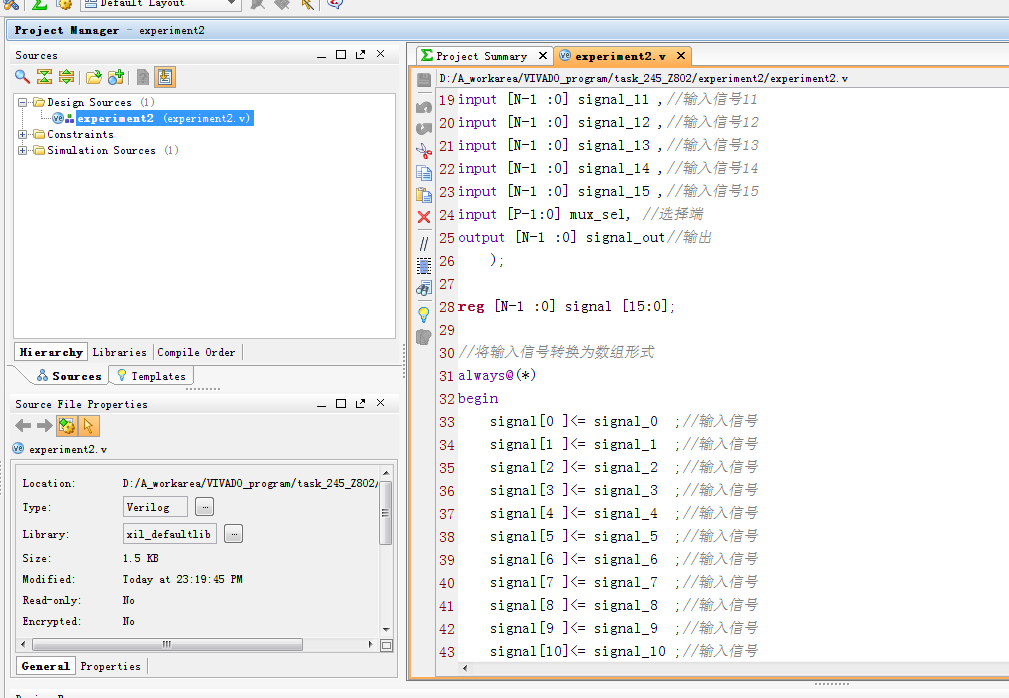

实验2

代码

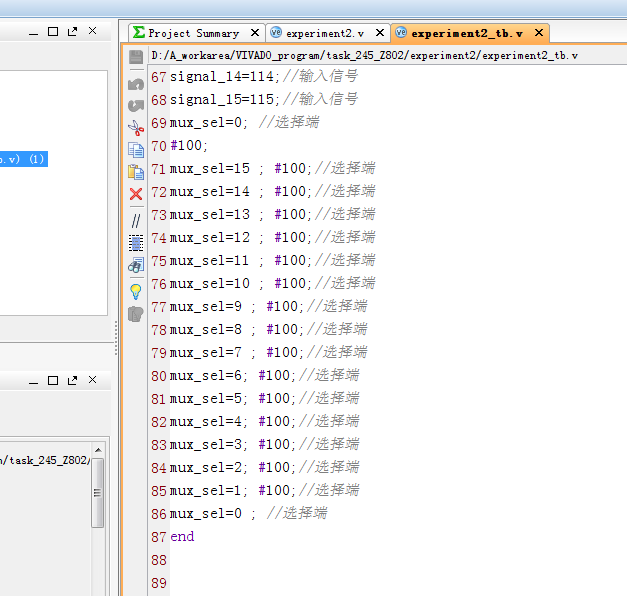

仿真代码

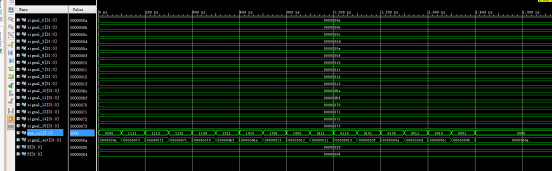

仿真图

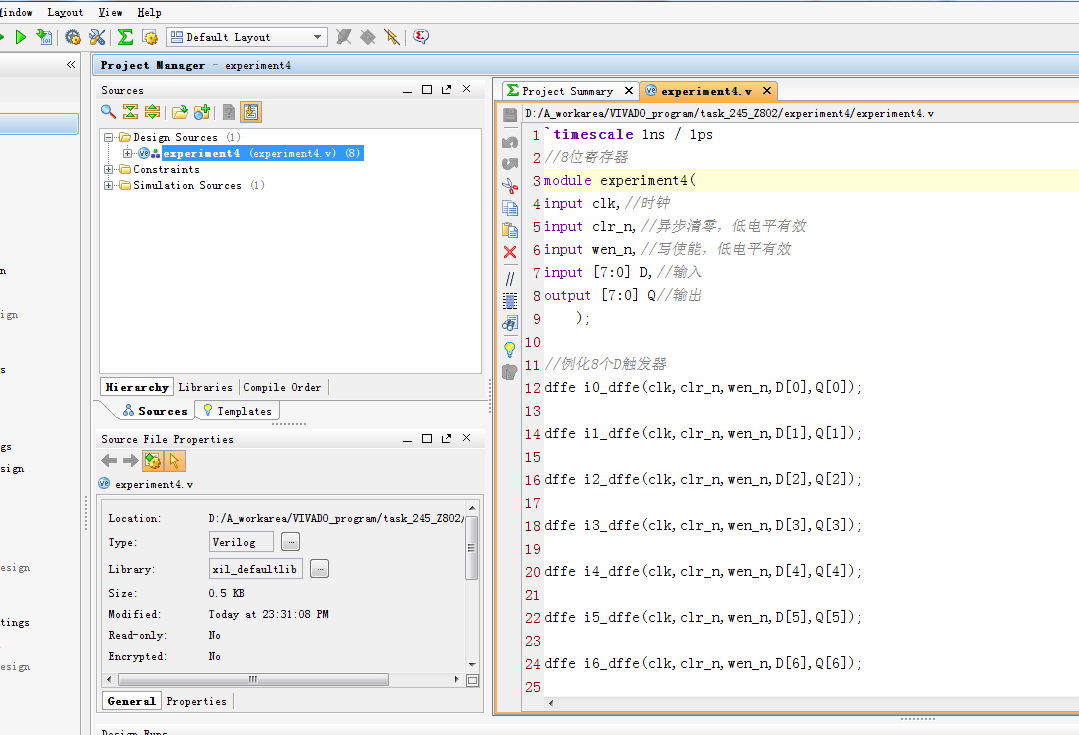

实验4

代码

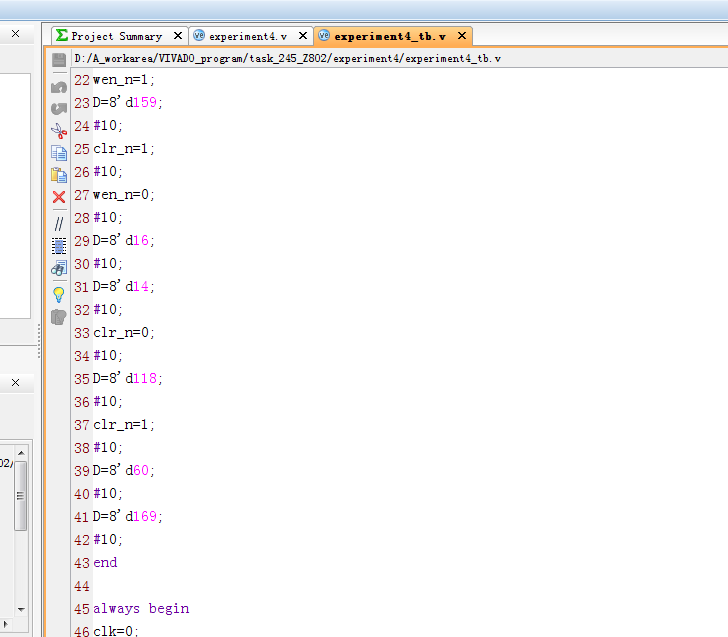

仿真代码

仿真图

实验5

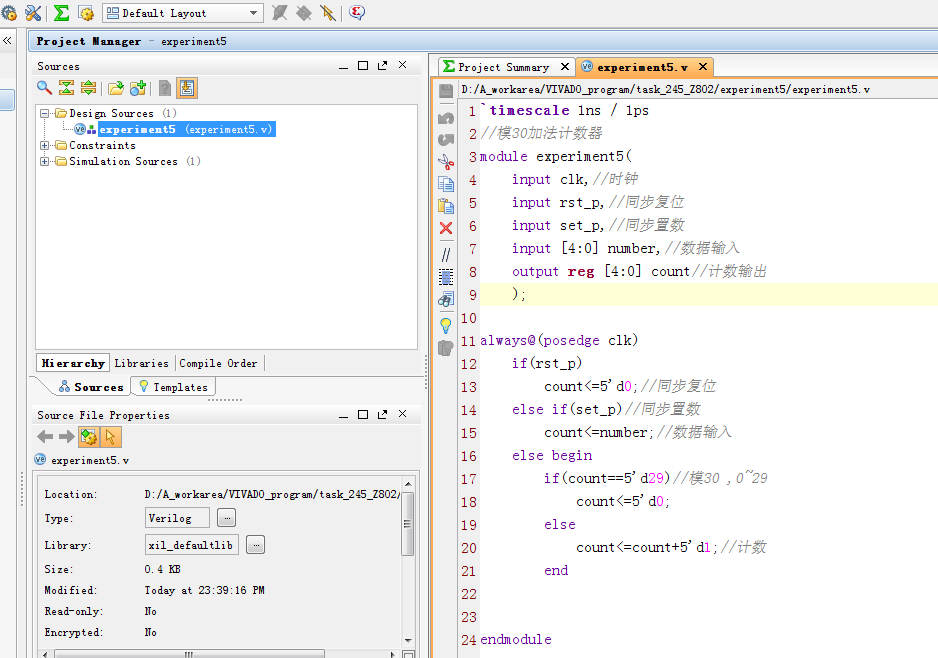

代码

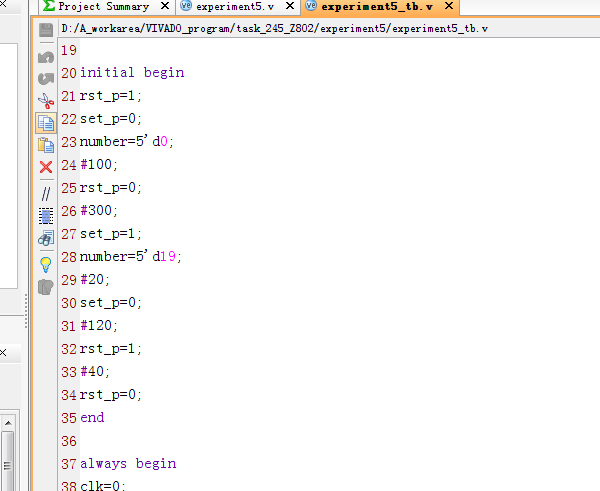

仿真代码

仿真图

部分代码展示:

`timescale 1ns / 1ps module experiment2 #( parameter N = 32, //数据位宽,可配置 parameter P = 4 //端口数=2^P,输入端口数,可配置,4表示端口数为16 ) ( input [N-1 :0] signal_0 ,//输入信号0 input [N-1 :0] signal_1 ,//输入信号1 input [N-1 :0] signal_2 ,//输入信号2 input [N-1 :0] signal_3 ,//输入信号3 input [N-1 :0] signal_4 ,//输入信号4 input [N-1 :0] signal_5 ,//输入信号5 input [N-1 :0] signal_6 ,//输入信号6 input [N-1 :0] signal_7 ,//输入信号7 input [N-1 :0] signal_8 ,//输入信号8 input [N-1 :0] signal_9 ,//输入信号9 input [N-1 :0] signal_10 ,//输入信号10 input [N-1 :0] signal_11 ,//输入信号11 input [N-1 :0] signal_12 ,//输入信号12 input [N-1 :0] signal_13 ,//输入信号13 input [N-1 :0] signal_14 ,//输入信号14 input [N-1 :0] signal_15 ,//输入信号15 input [P-1:0] mux_sel, //选择端 output [N-1 :0] signal_out//输出 ); reg [N-1 :0] signal [15:0]; //将输入信号转换为数组形式 always@(*) begin signal[0 ]<= signal_0 ;//输入信号 signal[1 ]<= signal_1 ;//输入信号 signal[2 ]<= signal_2 ;//输入信号 signal[3 ]<= signal_3 ;//输入信号

源代码

点击下方的公众号卡片获取

731

731

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?