正文

在Aurora片间接口的调试中,一共需要用到两片FPGA,为达到速率的要求,所以Aurora需要采用主从双核,双通道绑定的工作模式,一共需要四个GTX(一个GTX 支持4Gbps的速率,一个Aurora核使用两个GTX,所以本例程中一个Aurora核最高支持8Gbps的速率)来完成片间数据的传输工作。

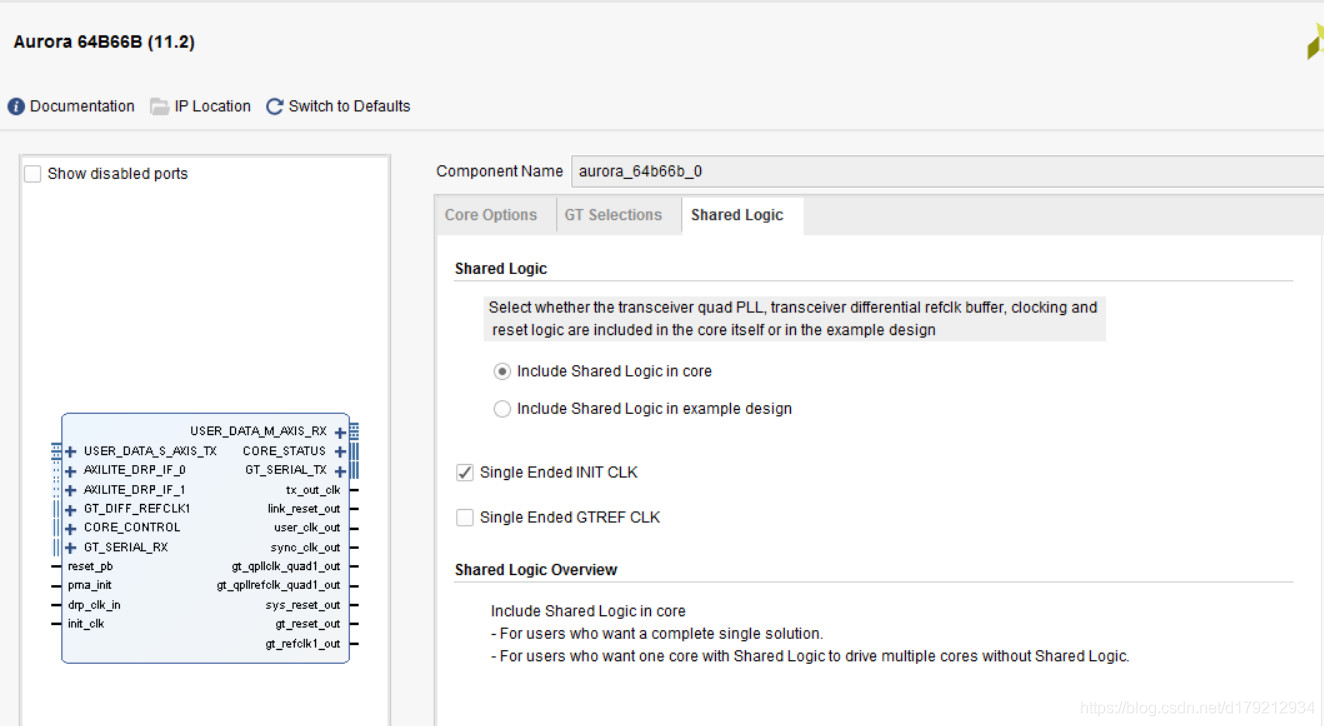

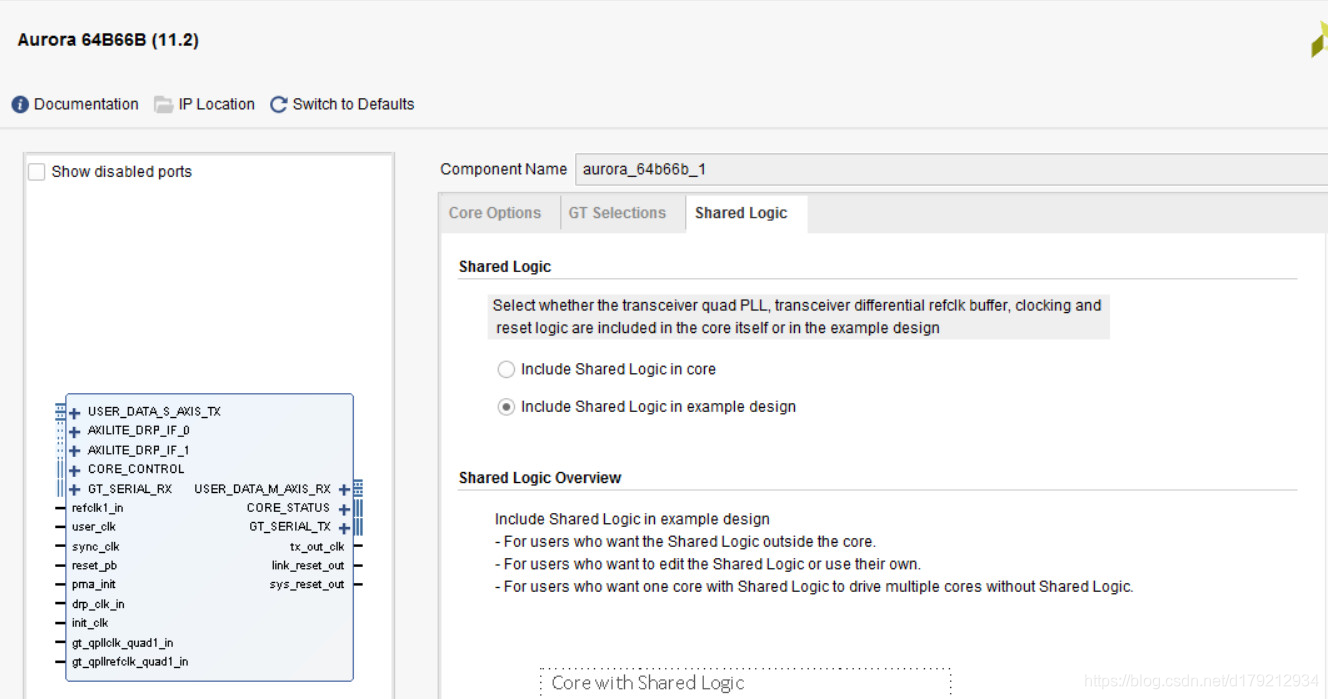

在工程中,主从双核的例化截图如下图所示(上图为主核,下图为从核):

由上两图可以发现,主从双核最大的区别在于时钟和复位的逻辑是否包含在例化的IP核中,主核的时钟和复位的逻辑包含在例化的IP核中,而从核是包含在生成的example design中。

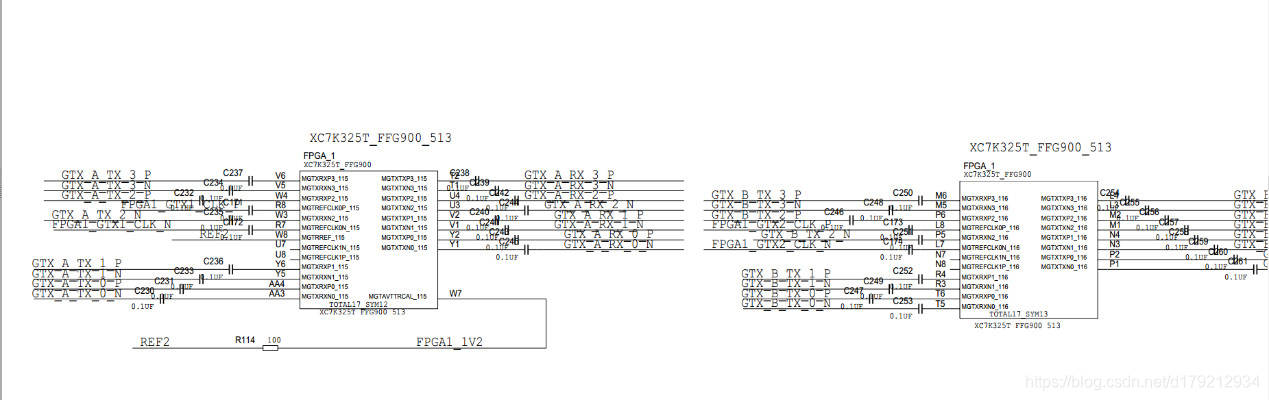

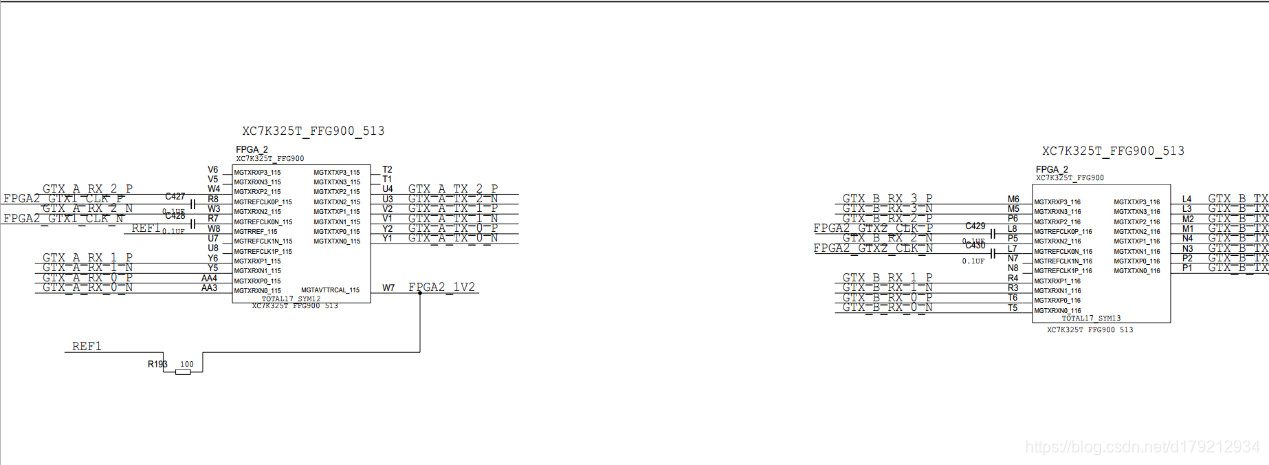

在完成Aurora的外部设计后,需要对GTX分配管脚,FPGA1和FPGA2中GTX的管脚如下图所示(上图为FPGA1,下图为FPGA2):

<

本文介绍了在Aurora主从双核配置中,使用GTX进行片间数据传输时遇到的布局布线错误。错误涉及GTX_COMMON和GTX_CHANNEL的放置问题,导致未在可路由站点对中放置组件。解决方案是根据Aurora用户手册,正确配置GTX_COMMON模块,确保其能驱动所有必要的GTX_CHANNEL。

本文介绍了在Aurora主从双核配置中,使用GTX进行片间数据传输时遇到的布局布线错误。错误涉及GTX_COMMON和GTX_CHANNEL的放置问题,导致未在可路由站点对中放置组件。解决方案是根据Aurora用户手册,正确配置GTX_COMMON模块,确保其能驱动所有必要的GTX_CHANNEL。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2551

2551

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?