按照上一篇介绍的fpga设计流程:FPGA开发流程以及Vivado的使用(一)-优快云博客,今天使用Vivado对38译码器进行了编写,遇到了一些问题,在这里记录一下。

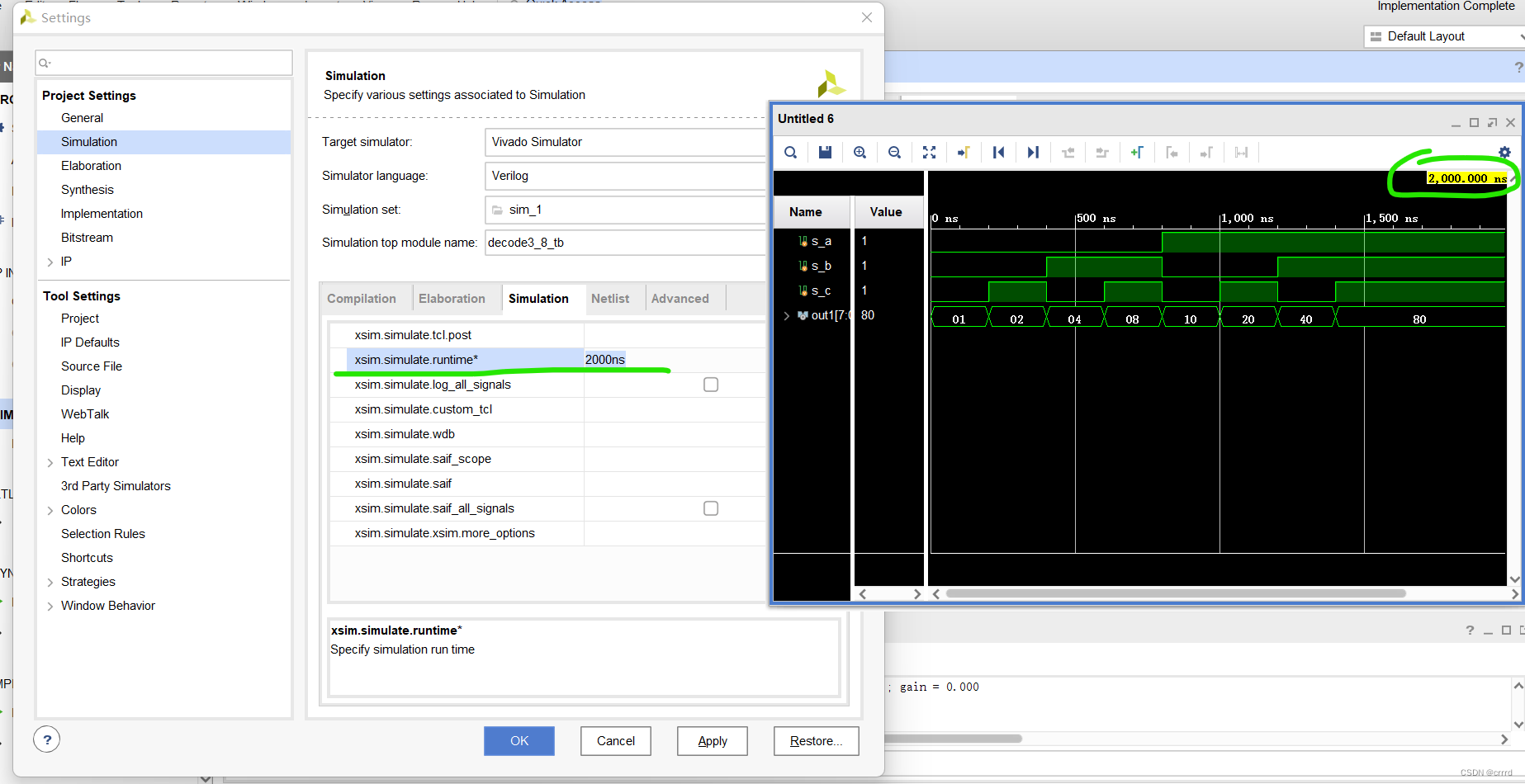

首先,上篇博客中提到了仿真时长的问题,发现可以通过改变Vivado默认的仿真时长解决,点击左侧栏中的Simulation->Settings,选择合适的仿真时间,比如2000ns,此时在运行仿真,可以看到右侧出现的波形中仿真时间变成了2000ns,但是我的代码中遍历全部情况只需要1400ns,因此可以添加$stop,运行仿真后会自动在1400ns停止。但如果仿真时长仍设定为1000ns,仿真过程就不会执行$stop想进行的操作。

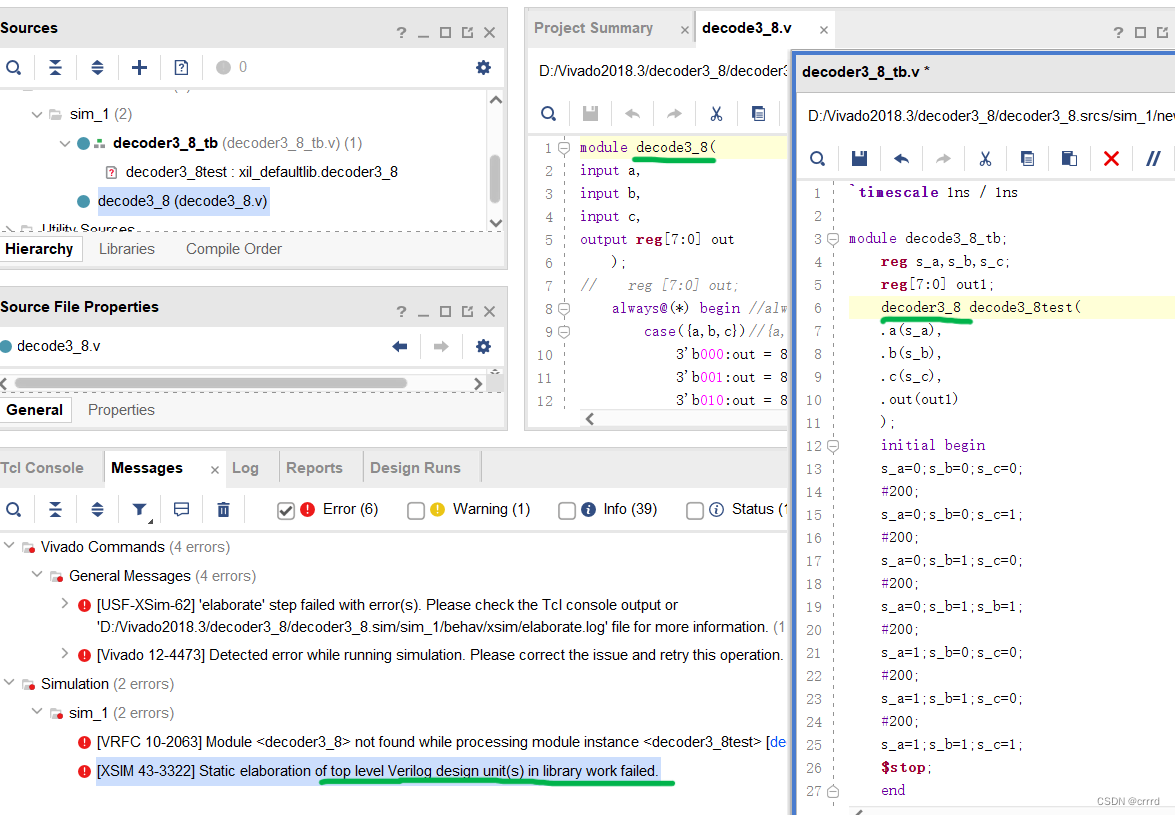

下面总结一下今天遇到的两个报错。设计文件形成组合电路后没有问题,在运行仿真文件时首先出现名为[XSIM 43-3322]Static elaboration of top level Verilog design unit(s) in library work failed.的报错。不太理解这里面提到的静态精化是什么意思,但就是说我们顶层Verilog设计单元在库工作中加载失败了。那么应该说明我在引用实例的时候出现了错误,经过检查发现,我在仿真文件中将设计文件中定义的名称敲错了,所以出现了这个问题。

改正后,上述错误消失,又出现了第二个错误:[VRFC 10-3236] concurrent assi

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

730

730

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?