在编译FPGA时,经常会报一些错误,记录一下如何解决

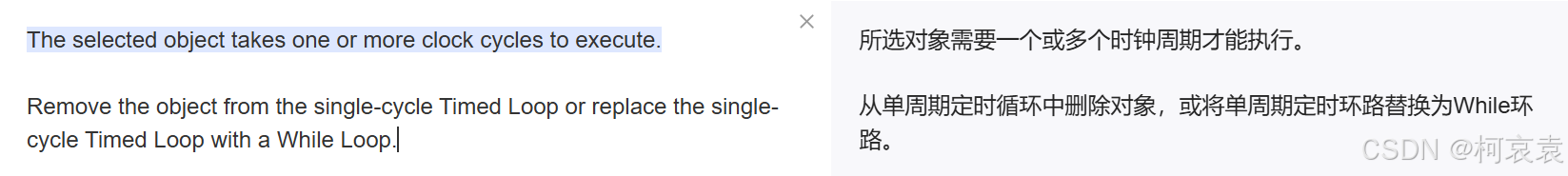

错误一:

错误提示

解决方法:将报错VI外部时钟替换为while循环

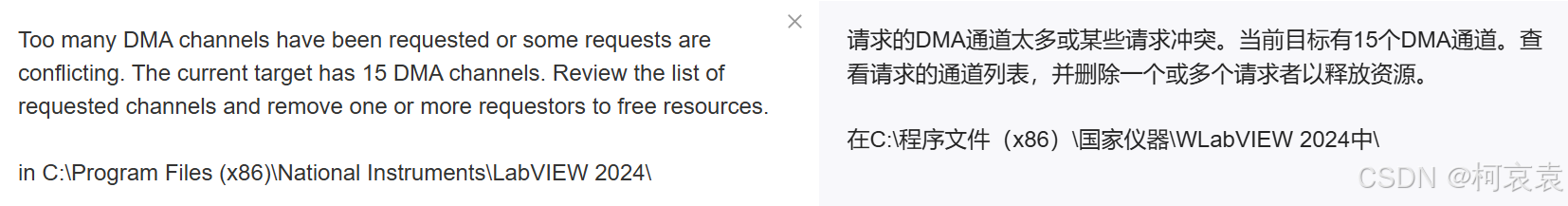

错误二:

错误提示

这个错误信息表明在您的LabVIEW项目中,请求的DMA(直接内存访问)通道数量超过了当前目标设备(可能是FPGA或其他硬件)所能提供的最大数量,即15个DMA通道。DMA通道用于在硬件和内存之间高效地传输数据,但当请求的数量超过硬件限制时,就会出现资源冲突或分配失败的问题。

解决办法:

尝试优化数据传输逻辑,减少DMA通道的使用。例如,通过合并数据传输请求或使用更少的DMA通道来传输更多数据。

如果某些DMA通道请求是不必要的,考虑移除这些请求。

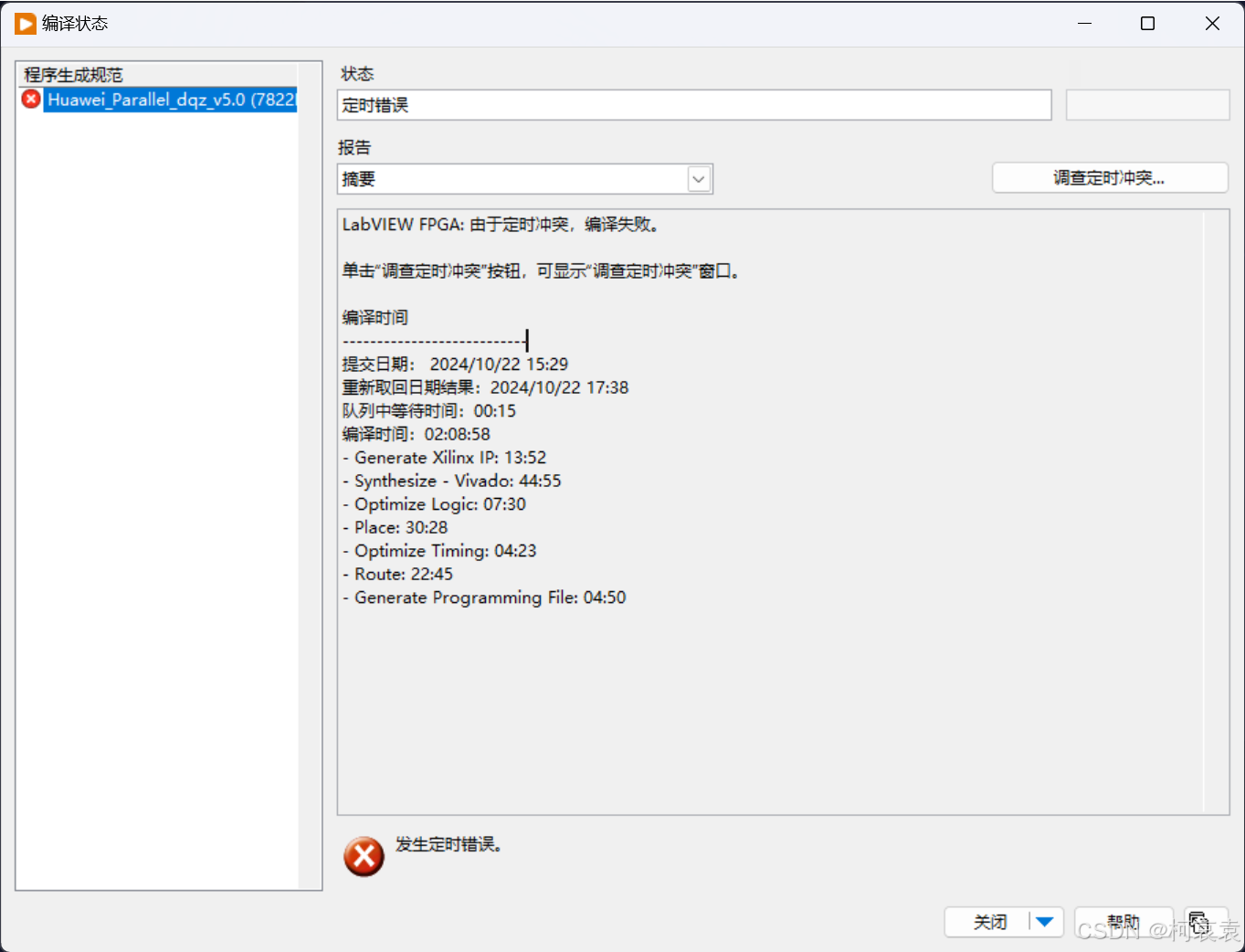

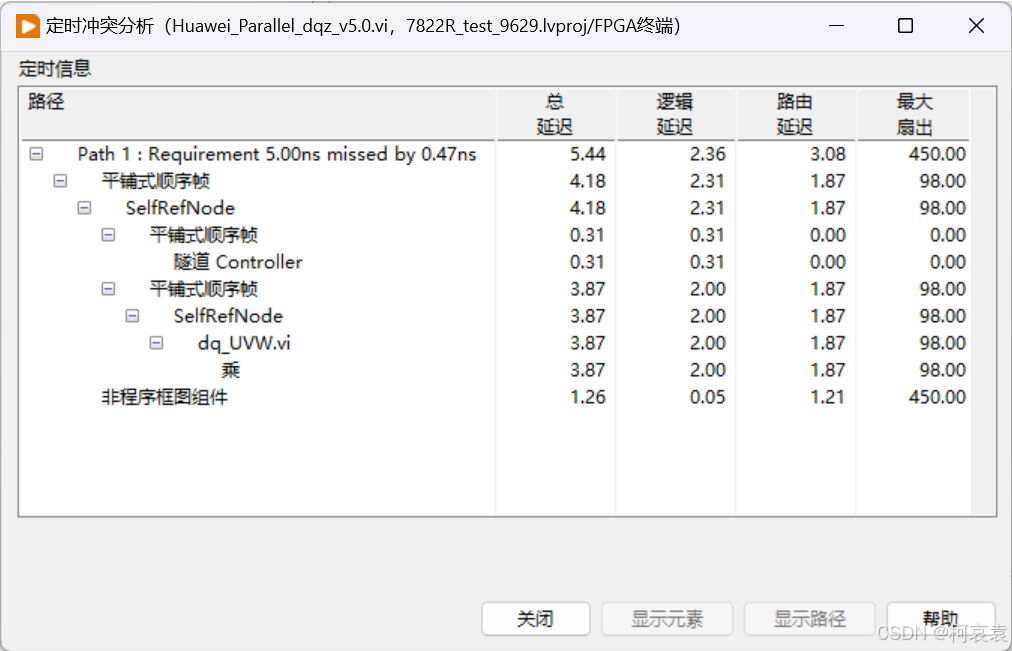

错误三:

解决办法:

1.检查时钟设置:

确保FPGA的时钟设置正确。检查时钟源、频率和相位设置是否符合设计要求。

如果FPGA设计依赖于外部时钟,确保外部时钟信号稳定并正确连接到FPGA。

2.检查定时逻辑:

仔细检查FPGA中的定时逻辑,包括时钟分频、状态机转换时间等。

确保所有定时路径都满足设计规格,没有超出最大时钟周期或违反时序约束。

3.资源冲突:

FPGA设计可能由于资源冲突(如同时访问共享资源)导致定时问题。

使用LabVIEW FPGA的资源冲突分析工具来查找并解决资源冲突。

4.编译设置:

检查LabVIEW FPGA编译设置,确保选择了正确的FPGA型号和编译选项。

尝试调整编译设置中的优化级别,有时降低优化级别可以解决定时问题。

5.代码审查:

仔细审查FPGA代码,查找可能导致定时错误的逻辑错误或设计缺陷。

使用LabVIEW FPGA的代码分析工具来帮助识别潜在的问题。

6.更新软件和硬件:

确保你的LabVIEW和FPGA硬件驱动都是最新版本。

有时,软件或硬件的更新可以解决已知的定时问题。

目前第三个问题还在解决中,有解决的小伙伴可以分享下,谢谢

1867

1867

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?