本篇博文是对ICG的一个系统理解

请勿随意转载: 优快云 博主:ciscomonkey

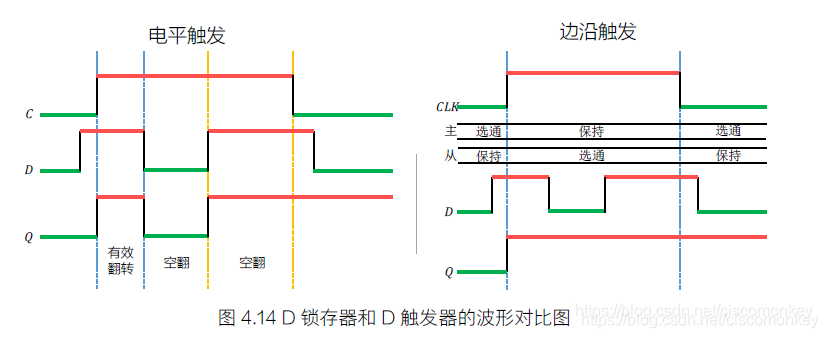

0、什么是电平触发latch?

如下图所示,我们可以看到latch也有由CLK(C)、D、Q组成的,不过在电平拉高阶段,一直处于改变数据的状态,而D触发器是边沿触发,所以是在CLK为上升沿的时候改变状态。

二者只是触发方式不同,导致改变数据的时间不同!

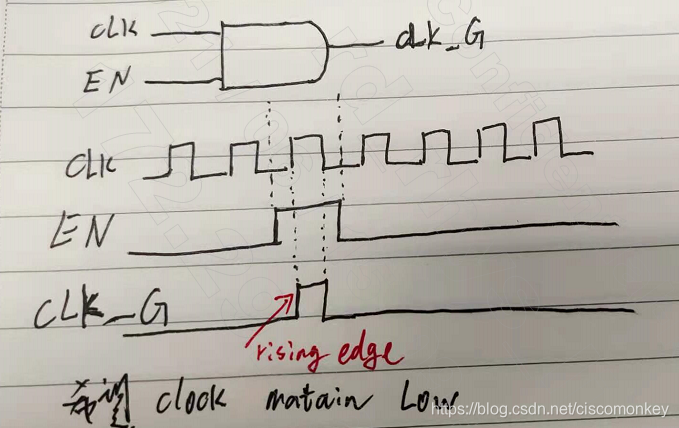

1、什么是ICG(integrated clock gating)

如下图所示,如果你希望关闭clock,那简单的方式是如图所示,我们通过一个与门,然后只要用一个框就能控制CLK是否通过,只要在框以内的CLK就能通过。使用与门,是希望不通过的时候CLK_G保持低电平。

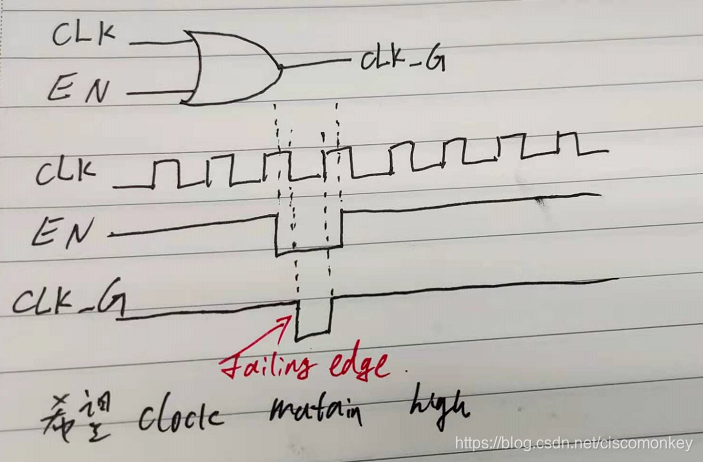

同理:如果我希望的是clock保持一个高电平,那么使用or gate,EN要开启通过的话,使用低电平。

但是上面这种结构却有风险存在,比如说与门,你确实把低电平的毛刺给消除了,但是如果高电平的地方出现毛刺怎么办呢?

所以我们有了负的的lockup,让其在高电平的毛刺不通过。

如下图所示,与门前面增加了低电平触发的lockup,实现了毛刺的滤除。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2918

2918

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?