一.理论知识

sdram芯片上电后,执行读写操作之前,首先要做的第一件事就是初始化,这里解释下初始化的目的。

1.在使用sdram资源的时候,要先给出芯片的地址,这个地址就是行/列地址。初始化第一步,首先就是要关闭所有bank中激活的行。虽然系统上电之后,sdram还没开始使用,没有被激活的行,但是依然要执行预充电这一步操作,确保在使用之前所有bank中没有激活的行。

2.sdram是动态存储器,物理层面是靠电容来维持电平信号,需要不断地给它刷新来给电容充电。在使用sdram资源之前,要给sdram的所有bank刷新。为了确保刷新成功,在初始化期间,要刷新多次。

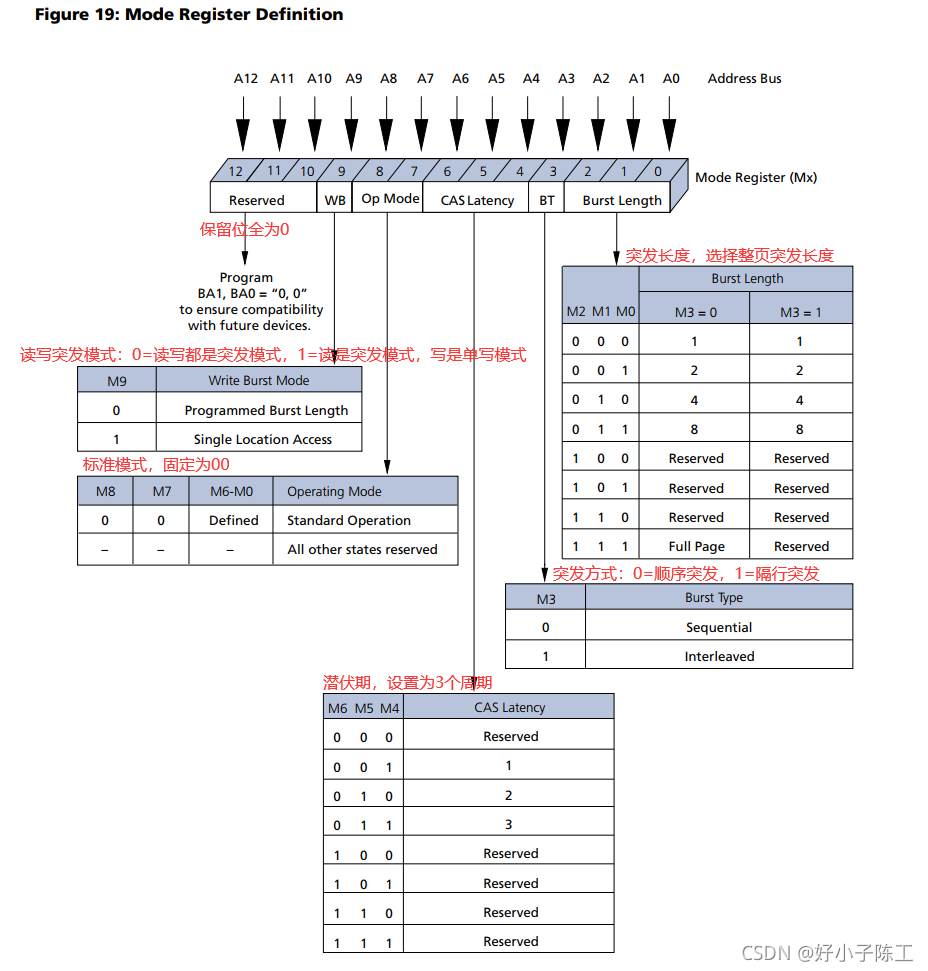

3.刷新完之后,要给sdram发送模式寄存器配置指令,模式寄存器主要控制芯片的读写方式,突发方式和突发长度等配置信息。为后面的读写操作提前设置参数信息。

二.解读数据手册

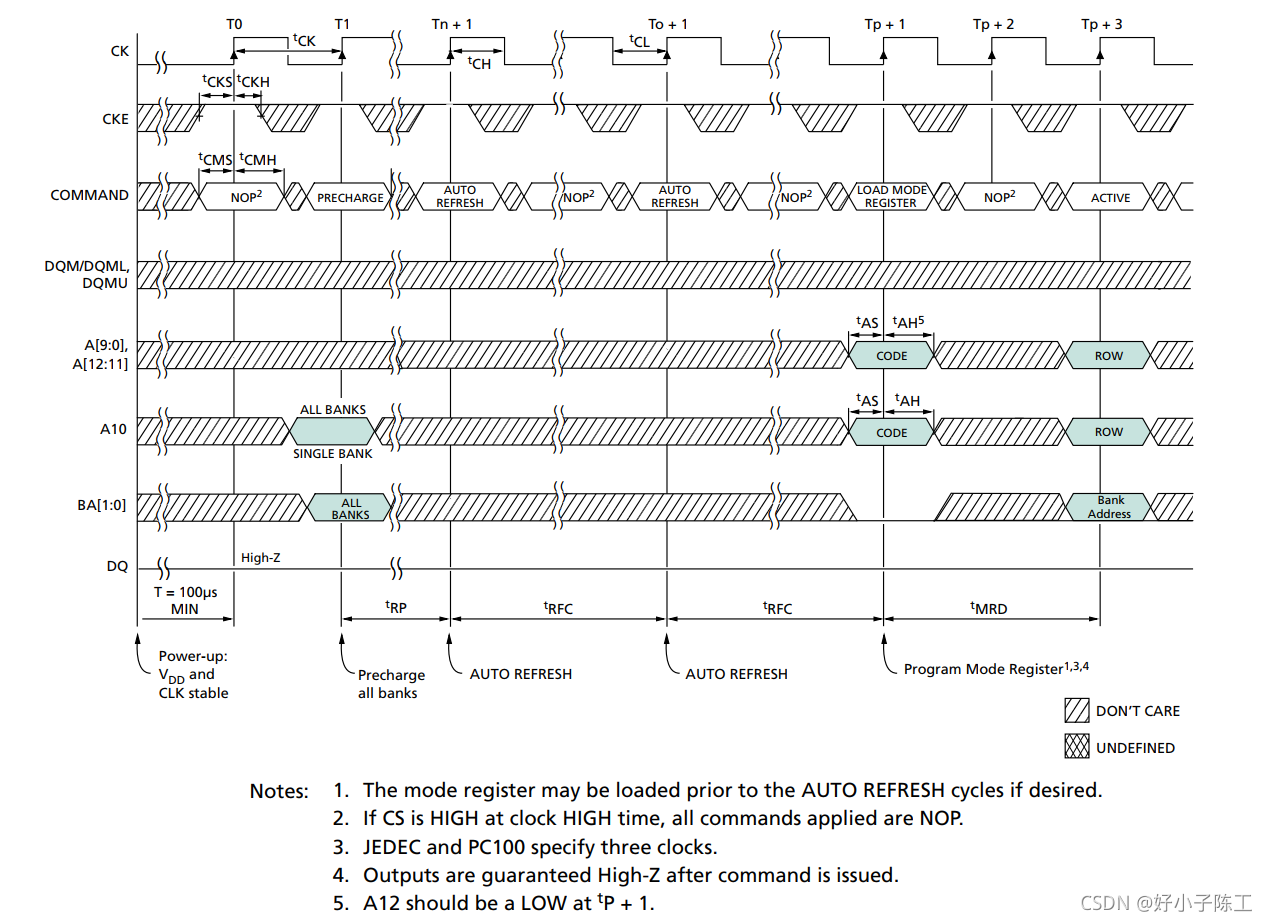

1.初始化操作时序

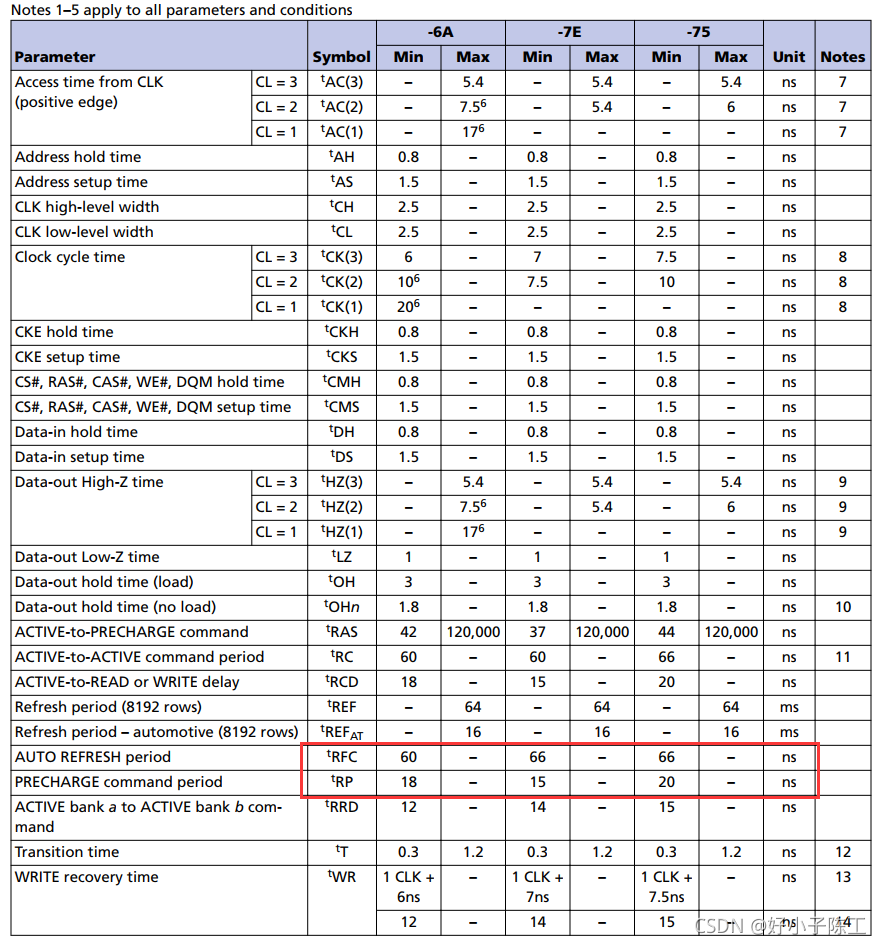

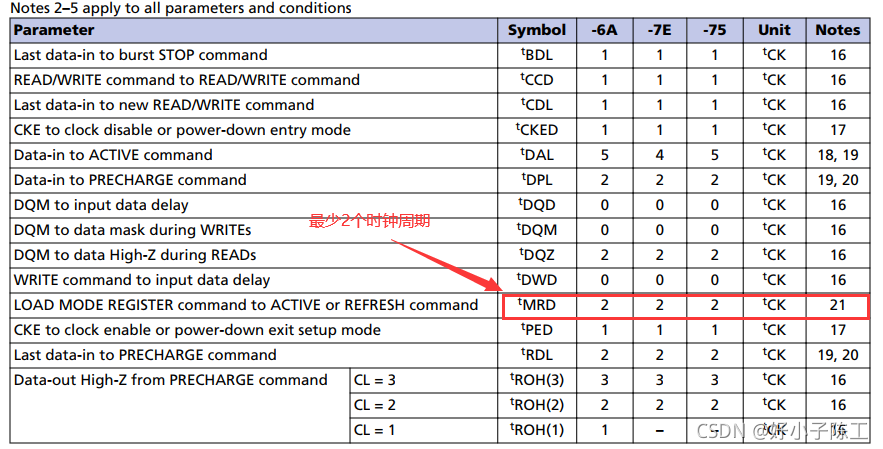

2.延迟时间

3.配置寄存器的值

上面的时序图是从镁光公司提供的sdram芯片数据手册中截选出来的。时序图介绍:

1.sdram上电后,加载稳定的时钟信号,然后设置CKE为高电平。芯片手册要求sdram的时钟频率最高不超过166M,这里我们选用100M时钟频率。sdram要求在时钟上升沿到来的时候,所有的信号数据要准备好,sdram会在上升沿采集这些信号。我们在fpga内部定义一个100M时钟信号,所有信号都在100M时钟的上升沿赋值。但是fpga的信号传输到sdram芯片中间会有延迟,所以我们另外再定义一个100M时钟信号,比前面的100M时钟信号偏移一定的角度,新的100M时钟上升沿比前面的100M时钟早到一会儿,然后把这个新的100M时钟信号发送给sdram。这样就能确保sdram能在时钟上升沿的时候采集到稳定的信号。

2.等待至少T=100us的时间,我们这里取200us,此过程中操作命令保持为空操作命令。

3.200us等待结束后,写入预充电命令,A10设置为高电平,对所有Bank进行预充电。

4.预充电指令写入后,等待tRP时间,从上图中找到tRP最少为20ns,sdram的时钟是100M,所以我们这里设置为2个时钟周期,此过程中操作命令保持为空操作命令。

5.等待tRP时间之后,写入自动刷新命令。

6.自动刷新命令写入后,等待 tRFC时间,从上图中找到tRFC最少为66纳秒,我们设置为7个时钟周期,此过程中操作命令保持为空操作命令。

7.tRFC等待时间结束后,再次写入自动刷新命令。

8.自动刷新命令写入后,

本文详细阐述了SDRAM芯片上电后的初始化步骤,包括关闭未激活行、预充电、刷新、设置模式寄存器,以及关键操作时序、延迟时间和Verilog代码实现。通过解读数据手册,一步步指导如何在FPGA中精确控制初始化流程以确保高效稳定的工作。

本文详细阐述了SDRAM芯片上电后的初始化步骤,包括关闭未激活行、预充电、刷新、设置模式寄存器,以及关键操作时序、延迟时间和Verilog代码实现。通过解读数据手册,一步步指导如何在FPGA中精确控制初始化流程以确保高效稳定的工作。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

883

883

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?