1、接口

- 将有关信号封装在一个接口(interface)中,进行模块连接时无需众多分散的端口。

- interface的端口列表只需定义时钟、复位等公共信号或者干脆不定义任何端口信号,而在变量列表中定义DUT与TB连接相关的logic变量。

- interface例化方式同module相同。

2、时钟块

- 在仿真时,为尽量避免时序电路中时钟和驱动信号的时序竞争问题,需尽量给出明确的驱动时序和采样时序,这就需要借助时钟块实现。

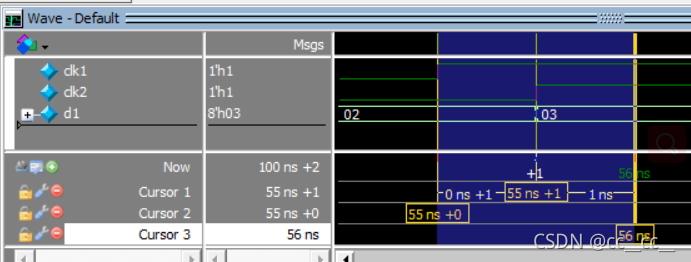

- 默认情况下,时钟对组合逻辑电路的驱动会存在一个无限小时间的延迟。下为示例,clk2和d均由clk驱动产生,通过在"Expanded Time Deltas Mode"下查看可知,这两个信号的产生相对于clk均存在着一个很小的延迟。

- 时钟块可以定义在interface、module和program中,同一个变量在不同时钟块中可以声明不同方向。

clocking clk_ex @(posedge clk); //上升沿驱动或采样

default input #2ns output #2ns; //默认情况在时钟上升沿前2s对输入采样,后2s对输出驱动

input in1, in2;

output negedge q; //在时钟下降沿进行输出驱动,覆盖上方条件

endclocking

本文介绍了硬件描述语言中的接口(interface)概念,强调其在模块连接时简化端口管理的作用。同时,探讨了时钟块在解决时序竞争问题中的重要性,特别是如何通过定义时钟块来明确驱动和采样时序。示例展示了如何在interface和module中使用clocking块,并指出同一变量在不同时钟块中可以声明不同方向,确保信号同步的准确性。

本文介绍了硬件描述语言中的接口(interface)概念,强调其在模块连接时简化端口管理的作用。同时,探讨了时钟块在解决时序竞争问题中的重要性,特别是如何通过定义时钟块来明确驱动和采样时序。示例展示了如何在interface和module中使用clocking块,并指出同一变量在不同时钟块中可以声明不同方向,确保信号同步的准确性。

915

915

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?