Array

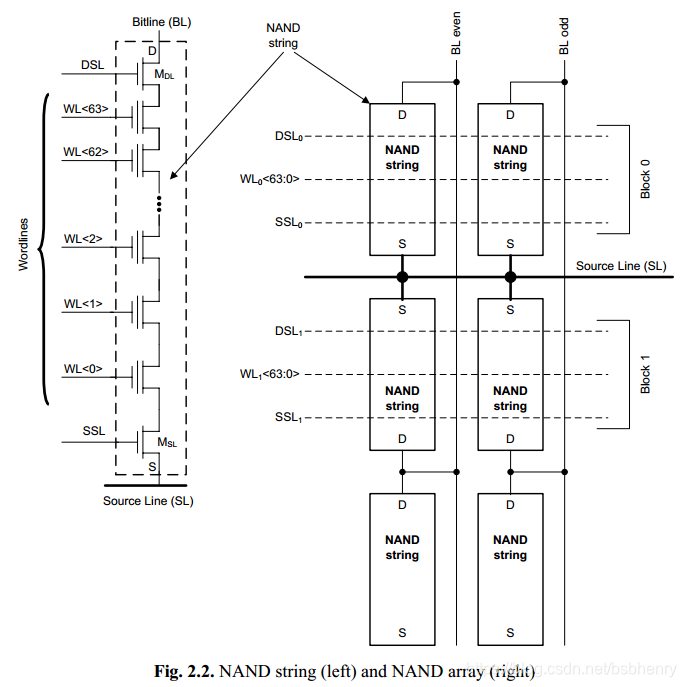

在String中,cell是串行方式连接的,一般32或64个一组,两端分别通过MSL连接到source line,MDL连接到bit line,并分别由晶体管控制开断。每个string和相邻的string(图中是上下方向)共用bit line。control gate是通过wordlines连接在一起。

Page是一个逻辑上的概念,page是由同一根wordline上的cell组成的。一根wordline上的page个数是由cell存储bit的能力决定的。SLC memory 单个cell可以存储1bit信息,MLC则可以存储2bit,TLC是3bit,QLC则是4bit。按照图中示意,bitline 分为even/odd两组,相应的cell也分为了两组,这两组分别属于两个page。

根据以上定义,则一个SLC的设备,一根wordline可以分为两个page,假设总共有65536个cell,则每个page的大小为4KB。

而MLC单个cell可以存储2bit的信息,则从逻辑上又可以进一步细分为两个page,一个是lower page,即由LSB(least significant bit)组成,一个是upper page,由MSL(most significant)组成。这样一个MLC的设备,一根wordline就分为了四个page。类似的,TLC单个cell可以存储3bit的信息,则有lower/middle/upper page。

对于擦除操作,同一组wordline上的所有string是一起进行的,它们组成了一个block。如上图,有两组wordline,WL0[63:0]和WL1[63:0],对应的分别是block0,block1。

Floorplan

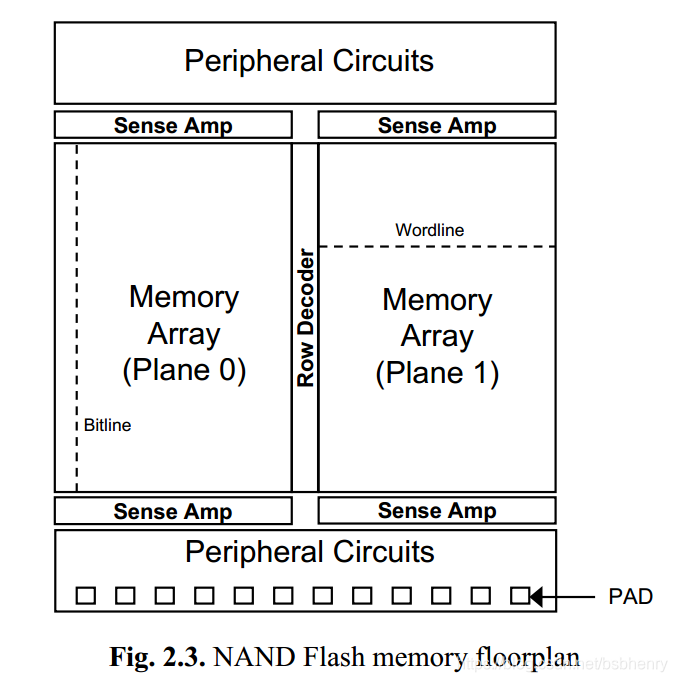

Nand Flash 芯片主要由array构成,同时需要外围电路来实现写读擦除功能。

Array一般分为若干个Plane,每个Plane都有独立的sense amplifier和cache,所以可以同时进行操作。wordline沿水平方向,bitline沿垂直方向,所有的bitline都连接到了sense amplifier上。Row Decoder在两个Plane之间。Row Decoder负责给被选中的string对应的各个wordline上加上合适的偏置。sense amplifier则将电流信号转换为数字量。

外围电路包括charge pumps(电荷泵),voltage regulators(电压调节器),及逻辑电路等。

PAD连接到芯片外部。

参考

Inside NAND Flash Memories

本文详细介绍了NAND闪存芯片的内部结构,包括阵列(Array)、cell的连接方式、page和block的概念,以及擦除、读取和写入操作的工作原理。此外,还解释了不同类型的存储单元(SLC、MLC、TLC)如何影响存储容量和数据读写。

本文详细介绍了NAND闪存芯片的内部结构,包括阵列(Array)、cell的连接方式、page和block的概念,以及擦除、读取和写入操作的工作原理。此外,还解释了不同类型的存储单元(SLC、MLC、TLC)如何影响存储容量和数据读写。

1122

1122

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?