亚阈值漏电功耗的分析与设计 —一种基于90纳米技术的电路级行波进位加法器‐感知 方法

摘要

无线传感器网络的设计空间主要集中在感知功率的电路上-。由于电路的事件-触发特性使其长时间处于 待机模式,漏电流功耗急剧上升,从而增加了其功耗。在众多漏电成分中,亚阈值漏电功耗(Psub_leak)是主 要部分,可通过一种称为短脉冲电源门控方法(SPOGA)的技术来降低。加法器是信号处理模块中的基本 数字子系统,本文在电路‐级抽象层次上,使用Cadence GPDK090对行波进位加法器(RCA)进行了P sub_leak分析。与传统和基于多阈值CMOS(MTCMOS)的RCA相比,Psub_leak显著降低,漏电节省达到35% 至40%。

© 2014作者们。由爱思唯尔有限公司出版。

关键词 : 亚阈值区漏电功率;行波进位加法器;电路-级;短脉冲 功率 g激活;多阈值CMOS;Cadence GPDK090

1 引言

无线传感器无线传感器网络(WSN)在新兴技术出现后具有广泛的应用程序。

WS设计社区 N 旨在使应用工具包在期望的时间内保持存活。显然,其性质为

电池供电设备力求在各个方面节省功率。大多数应用程序为事件驱动型,这使得电路操作大部分时间处于待 机模式,仅在很短的时间内处于活动模式。在待机或睡眠状态下,漏电流功耗的急剧上升主导了静态功耗, 从而带来了设计挑战1。因此,从功率角度来看,待机模式需要更多关注。在无线传感器网络的电路级设计 中,亚微米技术的缩小影响更为显著,即传统上用于动态功耗降低的电源电压缩放会影响阈值电压,进而使 亚阈值漏电功耗(Psub_leak)呈指数级增加1-3。因此,了解Psub_leak的消耗成为设计功率感知电路的基本要求。

数字子系统在所有类型的无线传感器网络架构的信号处理单元中起着关键作用9。其中,加法器是基本的子系 统,而需要线性数量门的加法器称为行波进位加法器(RCA),本文重点研究该加法器。本文分析了传统RCA中 的Psub_leak ,并采用一种称为短脉冲电源门控方法(SPOGA)的新型漏电减少技术设计了Psub_leak感知的RCA。该 设计使用Cadence GPDK的90纳米工艺节点实现,并与传统和传统的多阈值CMOS(MTCMOS)电路进行了对 比分析。

文献综述和相关工作在第二节中进行了讨论。传统RCA的分析在第三节中完成,亚阈值漏电功耗感知 型串行进位加法器在第四节中进行了讨论。仿真和结果在第五节中进行了讨论,第六节对论文进行了总结。

2 文献综述与相关工作

亚阈值漏电功耗和栅极漏电流功率是CMOS电路中漏电流功耗的主要组成部分。栅极漏电流功率只能通 过开发高k介电栅极绝缘体来有效降低,但这不在本文的讨论范围内;而亚阈值漏电功耗则可以通过切断电 源或使用高‐Vth (高阈值电压)晶体管 3来降低。Psub_leak在待机模式下几乎等于静态功耗,可通过公式1和公 式21, 2进行计算:

(1)

(2)

其中W是栅极宽度,V是热电压,K1和是实验导出常数,是电源电压,݄是阈值电压。

通过最小化内部节点电容,16位RCA的动态功耗降低,并实现了良好的延迟性能5。采用差分逻辑高效 地实现了RCA,并在随机输入操作数下达到了最佳性能6。在RCA中进行了时序误差缓解,并将其与其他加 法器进行了比较7。

3 传统RCA分析

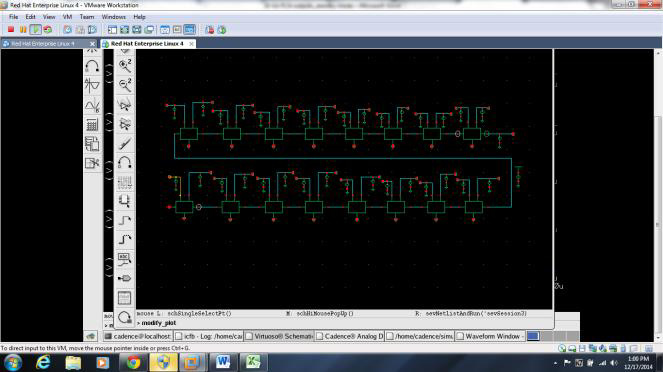

行波进位加法器(RCA)是由多个全加器并行连接而成的组合电路,其中一个加法器的进位输出作为 下一个更高位加法器的进位输入。本文采用如图1所示的传统16位RCA(16位RCA_CONV)作为测试平台 电路,用于分析其在待机模式下电路级的亚阈值漏电功耗,并使用了从FA_0到FA_15的16个两位全加器 使用。假设从A0 B0到A15 B15的所有输入均为0伏特,且进位-输入Cin为0伏特。总计 功率消耗,16-位RCA为2.4757μ瓦特。

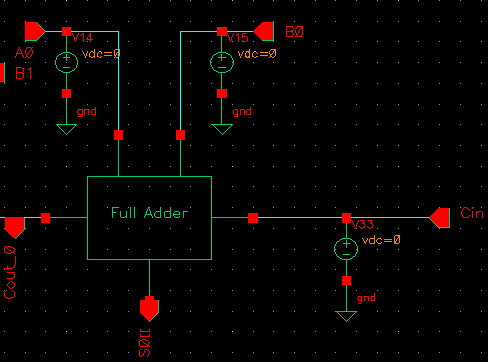

The one-位全加器 FA_0如图2所示,用于理解其功耗分析。该FA_0由EXOR_1门、EXOR_28门、 AND_1门、AND_2门和或门构成,每个门均由六个CMOS晶体管组成。由于输入A0 B0为00,该FA_0工 作在待机模式,PMOS(PM0、PM1、PM2和PM3)和NMOS晶体管(NM0、NM1、NM2和NM3)在其 工作区域运行,如表1所述。

这些区域分别为 R_0 (截止区)、R_1 (导通区)、R_2 (饱和区)和 R_3 (亚阈值区)。显然,当 V gs 低于 Vth时,晶体管 工作在亚阈值区,并消耗 154.7056nW 的亚阈值漏电功耗 Psub_leak 。全加器 FA_0的静态功耗 Pstatic为 154.73nW,其中 99.98% 的功耗由 R_3工作区的晶体管消耗;因此,全加器 FA_0到 16-位 RCA_转换器的漏电损耗为 6.25%。

| 全加器 0_ | 工作区域 | 工作区域 | 工作区域 | 工作区域 | Psub_leak (瓦特) | Pstatic (瓦特) |

|---|---|---|---|---|---|---|

| 门电路 | R_0 | R_1 | R_2 | R_3 | Psub_leak (瓦特) | Pstatic (瓦特) |

| EXOR_1 | NIL | NM1, PM0, PM3 | NIL | NM0, NM3, PM2 | 50.5126纳 | 50.5220纳 |

| EXOR_2 | NIL | NM1, PM0, PM3 | NIL | NM0, NM3, PM2 | 50.5037n | 50.5076n |

| AND_1 | NIL | NM3, PM0, PM1 | NIL | NM0, NM1, PM2 | 1.5954纳 | 1.5954纳 |

| AND_2 | NIL | NM3, PM0, PM1 | NIL | NM0, NM1, PM2 | 1.5928纳 | 1.5928纳 |

| OR | NIL | NM2, PM0, PM1 | NIL | NM0, NM1, PM2 | 50.5011纳 | 50.5122n |

| 总计 | 154.7056n | 154.73纳 | ||||

| ## 4 亚阈值漏电功耗-感知RCA |

从对16-位RCA_转换器的分析中,推断出亚阈值漏电功耗对静态功耗的影响。由于尺寸缩小,在待机模式下亚阈值漏电功耗显著增加,CMOS技术为瓦特级应用程序设计一种高效的亚阈值漏电功耗降低技术铺平了道路,该技术称为短脉冲电源门控方法(SPOGA)。

在此方法中,采用了多阈值CMOS(MTCMOS)与功率门控的混合概念,其中引入了高阈值电压(高‐Vth)睡眠晶体管。由于无线传感器网络(WSN)属于低占空比应用10, ,该混合方法导致漏电减少效果不佳。因此,采用了一种新颖的低占空比短脉冲概念来触发用于电路全局功率门控的睡眠晶体管。采用SPOGA技术设计了亚阈值漏电功耗感知的16位RCA(16‐bit RCA_SPOGA),如图3所示。输入信号送入16位RCA_转换器电路,总功耗Ptotal为0.2542μW。对所有全加器进行了分析,1位全加器_0的功耗如表2所示。亚阈值漏电功耗Psub_leak为4.4178nW,相较于16位RCA_CONV的漏电损耗,16位RCA_SPOGA的漏电损耗降低了1.74%。

| FA_0 | 工作区域 | 工作区域 | 工作区域 | 工作区域 | Psub_leak (瓦特) | Pstatic (瓦特) |

|---|---|---|---|---|---|---|

| 门电路 | R_0 | R_1 | R_2 | R_3 | Psub_leak (瓦特) | Pstatic (瓦特) |

| EXOR_1 | PM2 | NM1 | NIL | NM0, NM3, PM0, PM3 | 1.3271纳 | 1.337n |

| EXOR_2 | PM2 | NM1 | NIL | NM0, NM3, PM0, PM3 | 1.3263纳 | 1.336n |

| AND_1 | PM2 | NM3 | NIL | NM0, NM1, PM0, PM1 | 0.2195纳 | 0.2289纳 |

| AND_2 | PM2 | NM3 | NIL | NM0, NM1, PM0, PM1 | 0.2189纳 | 0.2284纳 |

| OR | PM2 | NM2 | NIL | NM0, NM1, PM0, PM1 | 1.326n | 1.336n |

| 4.4178纳 | 4.4663纳 | |||||

| 总计 |

5 仿真与结果

行波进位加法器使用Cadence Virtuoso设计,并在90nm工艺节点上通过Cadence Spectre进行仿真。采用1伏特的电源电压、温度为 27˚℃,瞬态分析的仿真时间为 10μ秒。在16-位 RCA_4753μ转换器中,连接了16个全加器,其总静态功耗为2.475728μ瓦特,亚阈值功耗为2瓦特。亚阈值漏电功耗的降低可通过改变晶体管宽度、阈值电压、漏源电压、-到-源极电压、体电流等参数实现,如其基本公式2所示。由于本文专注于电路级的降低技术,除其他与制造工艺相关的参数外,仅采用调节阈值电压的方法。-依赖。

| 16位RCA | Ptotal (W) | Pstatic (W) | Psub_leak (W) | 损平漏耗均电(%) |

|---|---|---|---|---|

| RCA_CONV | 2.4757μ | 2.4757μ | 2.4753μ | 99.98 |

| RCA_多阈值 CMOS | 1.7445μ | 0.8268μ | 0.7431μ | 66.24 |

| RCA_短脉冲电源门控方法 | 0.2542μ瓦特 | 71.4608n | 70.6848n | 63.36 |

16位RCA_SPOGA显著降低了亚阈值漏电流,并使全加器_0的漏电损耗最小。因此,其整体功耗相较于传统和现有流行技术多阈值CMOS(MTCMOS)更低,如表3所示。

现有技术通过33.74%的漏电节省减少了Psub_leak ,而SPOGA技术实现了36.62%的漏电节省。值得注意的是,亚阈值漏电功耗感知型16位RCA在漏电减少方面提供了2.88%的改进。SPOGA技术带来适度的面积开销;然而对于不同的占空比应用程序,特别是无线传感器网络应用,具有更高的灵活性。

6 结论

功耗感知电路在无线传感器网络应用中是不可避免的,因为它在目标应用的大部分持续时间内都处于待机模式。由于无线传感器网络架构的处理单元包含数字电路,本文重点研究行波进位加法器。由于静态功耗主要由亚阈值漏电成分主导,因此在传统和现有的多阈值CMOS 16位RCA中,针对90纳米工艺节点(Vdd=1 V)在电路级进行了分析。提出了一种新颖的5%占空比短脉冲触发方法,应用于全局功率门控电路中的高阈值电压睡眠晶体管。与传统和现有技术相比,Psub_leak显著降低,漏电节省达36.62%,并实现了2.88%的改进。尽管适中的面积开销可能会低估该技术的优势,但它公平地减少了漏电流功耗,从而降低了静态功耗。

未来,该设计将进行版图实现,并进行版图后仿真,以比较SPOGA技术的有效性。

138

138

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?