一、学习任务

基于Quartus-II软件完成一个1位全加器的设计,分别采用:1)原理图输入 以及 2)Verilog编程 这两种设计方法。软件基于quartusII 13.0版本,开发板基于Intel DE2-115。

二、学习内容

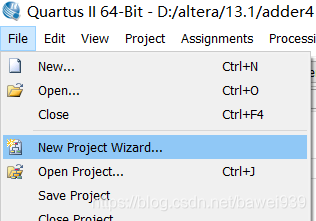

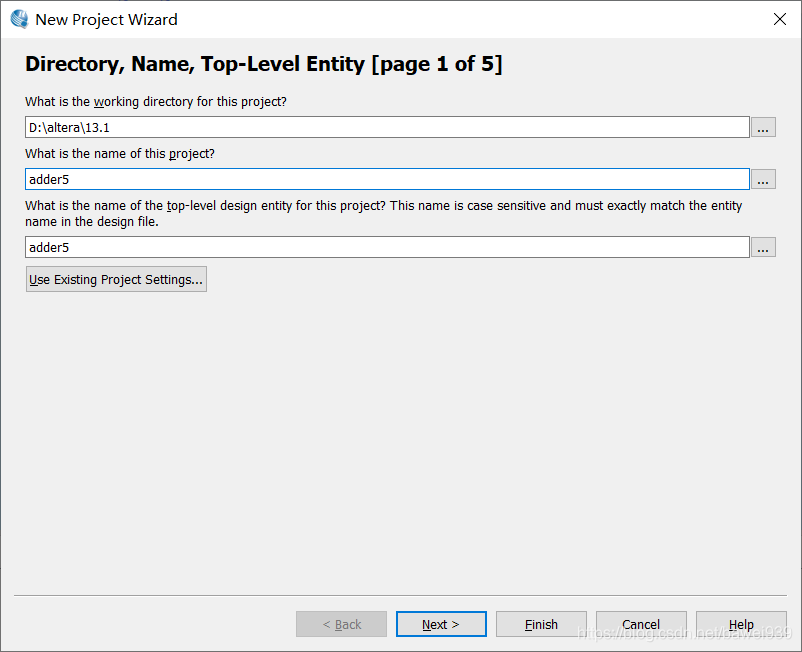

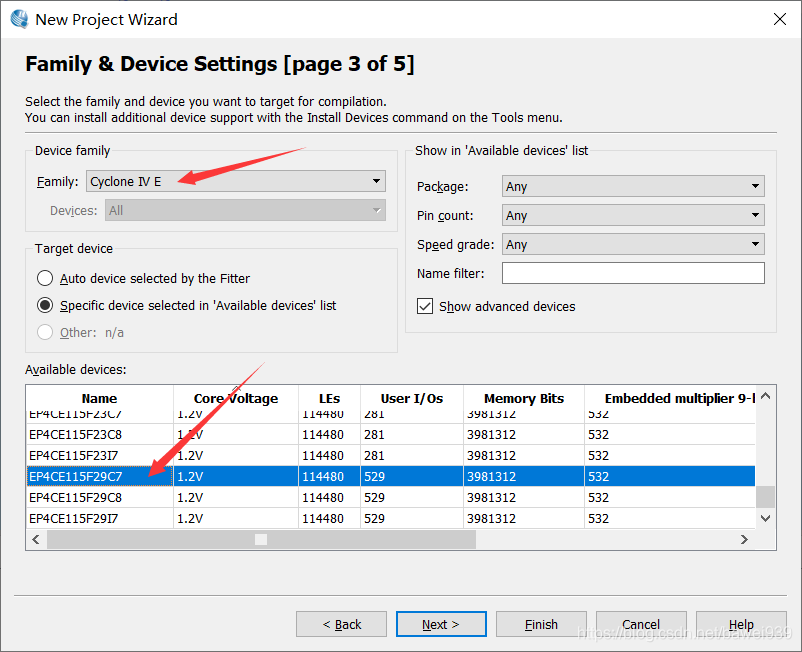

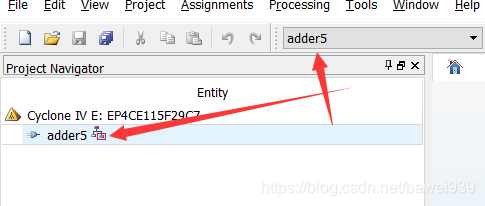

1.新建工程

选择目标芯片:cycloneIVE系列的EP4CE115F29C7

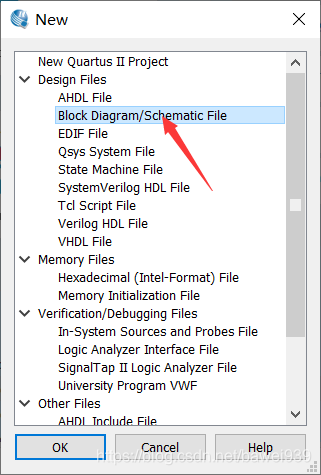

2.新建原理图文件

file->new

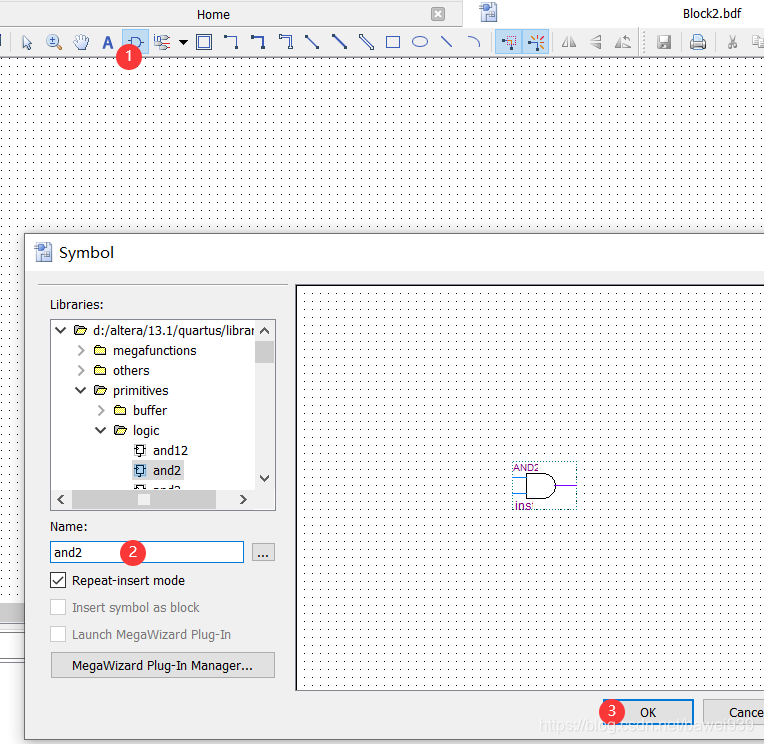

以下步骤 在2处输入 and2 xor

连线如图所示

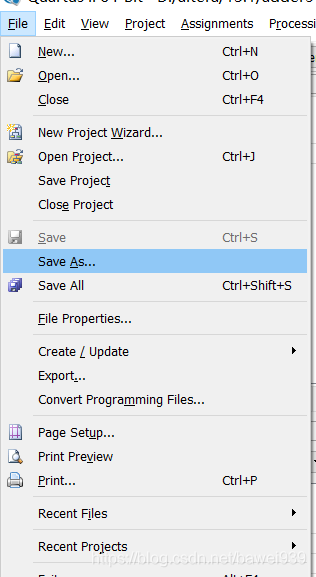

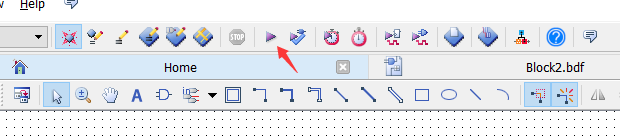

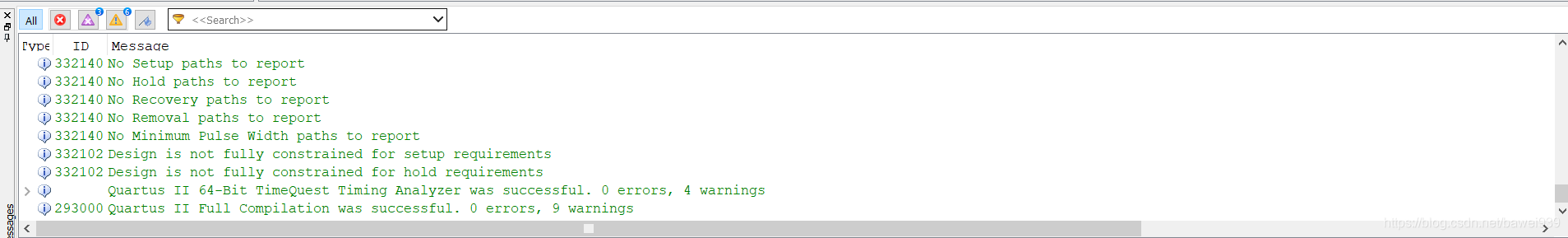

保存并编译

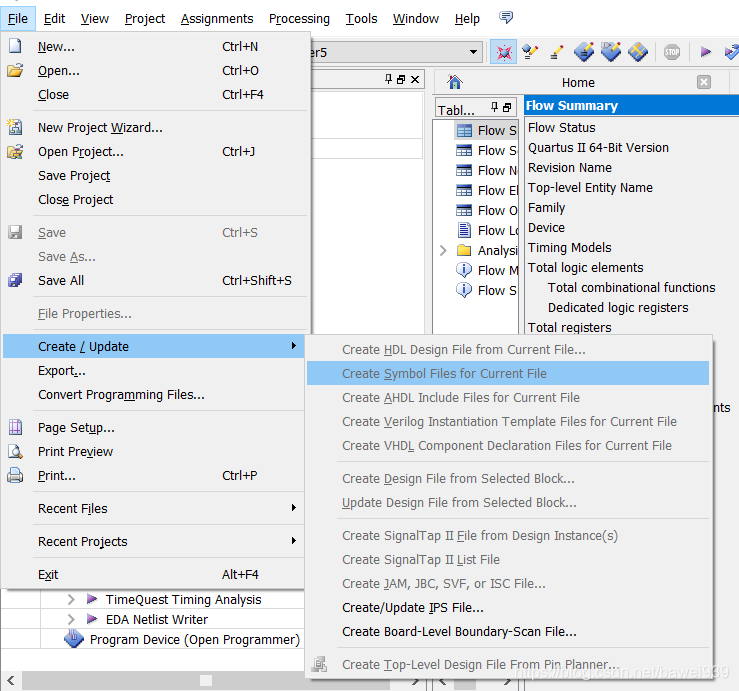

3.将设计项目设置成可调用的元件

为了构成全加器的项层设计,必预将以上设计的半加器adder.bdf

设置成可调用的元件。方法图所示,在打开半加器原理图文件adder.

bdf的情况下,选择菜中File中的Create/Update→Create Symbol Files for

Current File项,即可将当前文件adder. bdf变成一个元件符号存盘,以

待在高层次设计中调用。

使用完全相同的方法也可以将VHDL文本文件变成原理图中的一个元件

符号,实现VHDL文本设计与原理图的混合输入设计方法。转换中需要注意以

下两点:

〔1)转换好的元件必须存在当前工程的路径文件夹中;

(2)该方法只能针对被打开的当前文件

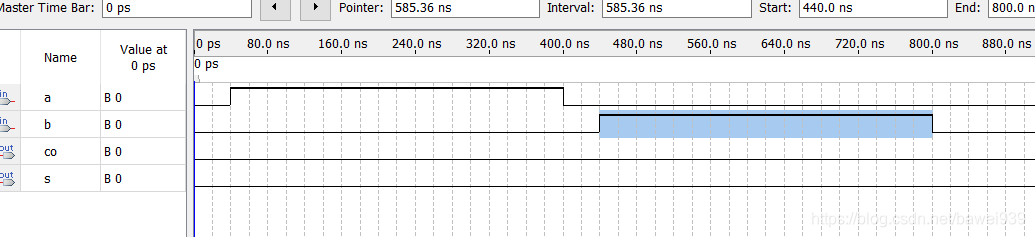

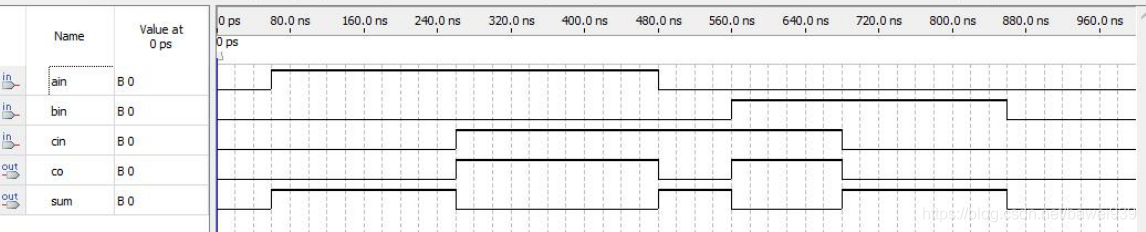

4.半加器仿真

4.1.新建波形文件

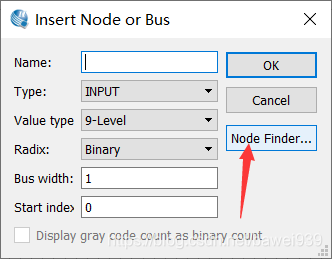

4.2.输入波形文件

在波形文件编辑器左端大片空白处双击,出现“insert node

or bus”对话框,点击“node finder”按钮。如图

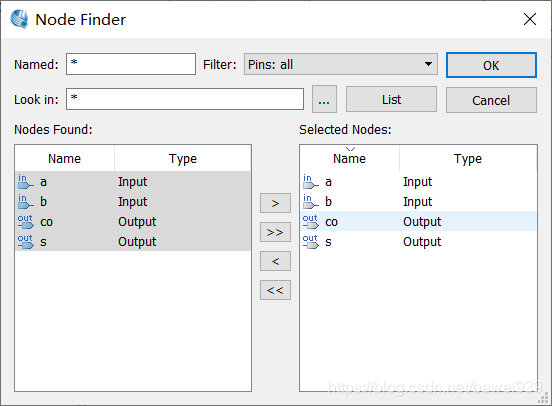

点击list在该界面上点击“>>”,则把左边所有的端口都选择到右边,进入波形。如图

设置输入波形取值。方法可以是选中某段需要设置数值“1”的波

形,即可。反之设置“0”,或其余数值同法可行。仿真如下:

本文详细介绍了使用Quartus-II 13.0设计1位全加器,涉及原理图绘制、元件调用、半加器仿真及Verilog编程过程。通过步骤教学,从创建工程开始,到设置可调用元件,再到波形文件操作和VHDL混合设计,适合初学者学习FPGA设计实践。

本文详细介绍了使用Quartus-II 13.0设计1位全加器,涉及原理图绘制、元件调用、半加器仿真及Verilog编程过程。通过步骤教学,从创建工程开始,到设置可调用元件,再到波形文件操作和VHDL混合设计,适合初学者学习FPGA设计实践。

2559

2559

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?