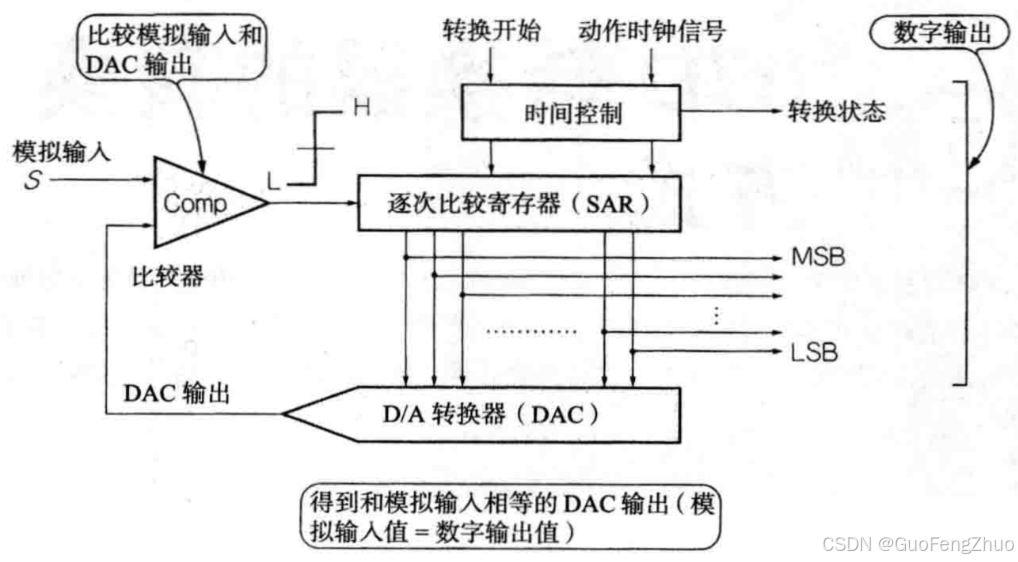

一、SAR ADC 工作原理

逐次比较型模数转换器(SAR ADC)的基本构成包括以下三个主要功能部件:N位分辨率的数字到模拟转换器(DAC)、比较器、逐次逼近寄存器(SAR)。

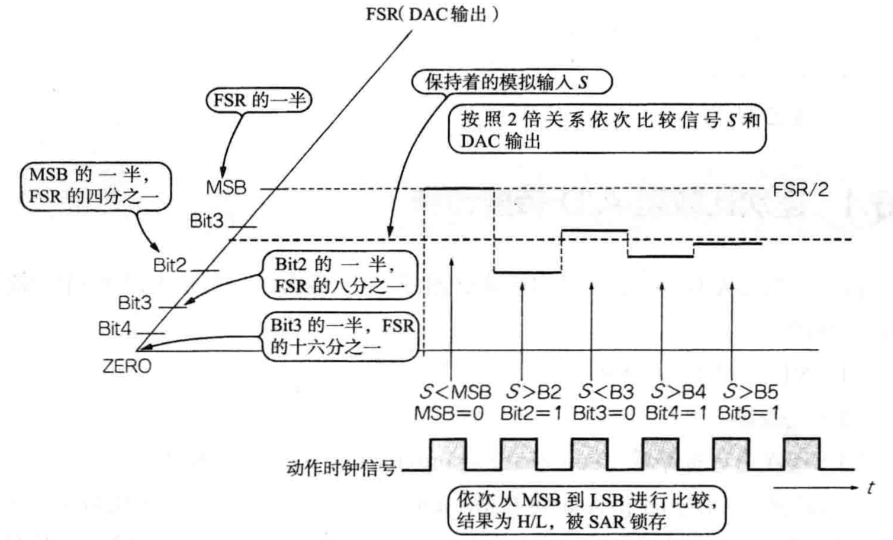

假设我们有一个16位的ADC,其基准电压(参考电压)为2.5V。当ADC开始工作时,会首先设置内部DAC输出一个初始值,通常是参考电压的一半1.25V,该输出值将输入电压进行比较。

如果输入信号≥1.25V,表明输入信号位于参考电压的上半部分,则逐次比较器MSB将被设定为1,其他位设定为0,同时对该位进行锁存;如果比较结果为输入信号<1.25V,表明输入信号位于参考电压的下半部分,MSB将被设定为0,同时对该位进行所存(如果对设置MSB位不理解,请复习权重概念)。

接着会尝试确定第二位。将DAC的输出设置为MSB确定后的一半(1.875或者0.625V),再次使用比较器进行比较,确定第二位是1还是0,并更新寄存器值同时锁存。这个过程会一直重复,且每次确定一位后,SAR都会更新DAC的输出,使其更接近输入信号的实际值。当所有位都被确定后,SAR通过并行或串行方式输出最终的数字值,这个值是输入模拟信号的数字表示。

逐次逼近型ADC的关键在于它的转换过程是逐步进行的,每一步都在尝试更精确地逼近输入信号的实际值。这种方法的优点是算法简单,实现容易,但在转换速度和精度上可能不如某些其他类型的ADC。

我们不妨以指令执行动作的角度来来理解:

- SAR寄存器初始化:在ADC转换开始时,SAR寄存器通常被清零或设置为初始状态。

- 位的确定:SAR寄存器按照从最高有效位(MSB)到最低有效位(LSB)的顺序,逐个确定每一位的值。

- 控制DAC输出:每当SAR寄存器确定了某一位的值(0或1),它就会更新DAC的控制信号,从而改变DAC的输出电压。

- 逐次逼近:SAR寄存器通过不断更新DAC的控制信号,逐步逼近输入模拟信号的真实值。

- 锁存位值:在确定了每一位的值之后,SAR寄存器会将这个值锁存起来,以便在确定下一位时使用。

- 完成转换:当所有位都被确定并锁存后,SAR寄存器中的值就代表了输入模拟信号的数字表示。

- 输出结果:最终,SAR寄存器中的数字值会被输出,作为ADC的转换结果。

二、SAR ADC采样阶段

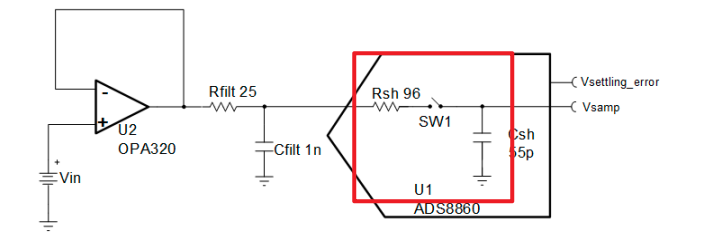

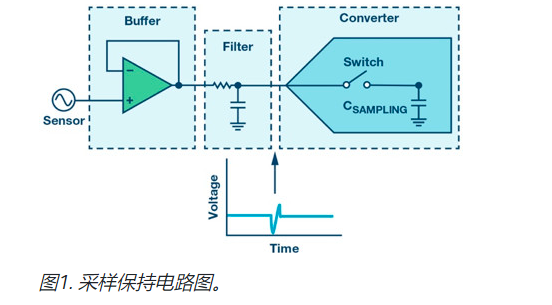

在SAR ADC的结构中,除了数字到模拟转换器(DAC)、比较器和逐次逼近寄存器(SAR)之外,采样保持电路也是其核心组件之一。

采样保持电路可视为由开关、电阻器、电容器组成的用于在转换过程中稳定输入的模拟信号的电路,其中开关是由CMOS构成。

SAR ADC的工作原理主要分为两个阶段:采样阶段和转换阶段。每个阶段都对确保ADC的精度和性能至关重要。

采样阶段是整个过程的第一步,此时开关S1闭合,使得外部放大器的输出电压能够对ADC内部的采样保持电容(Csh)进行充电。这一过程通过一个电阻器(Rsh)完成,以捕获输入信号的瞬时值。在高速采样率的ADC中,如1M采样率,采样时间可能极为短暂,仅有300纳秒。这个阶段的目的是确保Csh能够准确地存储输入信号的电压值。

紧接着是保持阶段,在这个阶段,开关S1打开,此时Csh保持其电荷,从而维持输入电压,直到转换过程完成。保持阶段是至关重要的,因为它确保了在转换阶段,输入信号的电压值不会因为外部信号的变化而改变,从而保证了转换的准确性。

随后进入转换阶段,SAR ADC采用逐次逼近的方法,从最高有效位(MSB)至最低有效位(LSB),逐步确定输入信号的数字值。在这一过程中,DAC的输出与采保电容上的电压进行比较,比较结果决定了每一位的值(0或1)。当所有位的比较完成后,最终的数字值被存储在结果寄存器中。

在设计SAR ADC时,确保采样和保持阶段的精确性对于整个转换过程的精度至关重要。为了使电压误差不超过最小可检测电压的一半,即1/2 LSB(下图,开关响应输入瞬间,输入电压发生跌落),选择具有更宽带宽的放大器和设计正确的外部RC电路能够提供迅速的响应变化。这直接关系到保持阶段电压的稳定性与精度。

尽管追求更低的电压误差对于提高ADC的精度是有益的,但必须认识到,存在一个理论上的最高精度限制,这是由量化噪声所决定的。量化噪声是SAR ADC在转换过程中不可避免的一部分,它源于ADC的有限分辨率。因此,在设计过程中,需要在减少电压误差和接受量化噪声之间找到合适的平衡点。过度追求电压误差的降低可能并不会显著提升整体精度,因为量化噪声已经为精度设定了一个上限。

三、 SAR ADC 外部运放和RC滤波电路的选型

对RC电路我们既要选择合适的RC值来满足调整率的精度 ,又要保证运放的稳定性。 大的电容将提供快速的电荷充电-给内部的采保电容在采样阶段开始时。 而电阻则有利于维持运放的稳定性 。

四、是否可移除RC电路 直接驱动SAR ADC ?

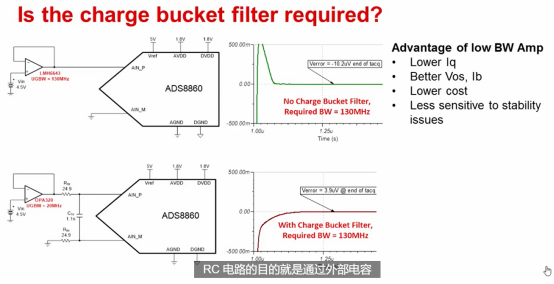

为什么我们不能忽略外部的RC 电路 ,下图很好地展示了 两个相同的ADC被不同的放大器来驱动的例子。 两种配置都具备很好的调整性能, 其中驱动中外部无RC的电路 ,要求运放配置130MHz的带宽;驱动外部带RC电路,运放配置只要求20MH的带宽。RC电路的作用是通过外部电容给内部的采保电容进行充电,来实现快速的调整率,总的来说如果有可能,调整时间允许的话建议低带宽的运放,因为低带宽的运放有较低的静态电流和失调电压偏置电流、较低的成本、 更好的稳定性 ,最后 RC电路还可以对噪声进行一定的抑制

五、如何找到合适的数据转换器

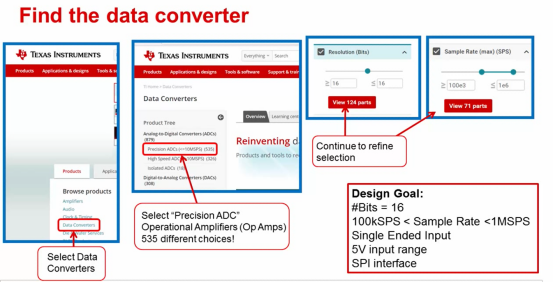

为了从众多的模数转换器(ADC)中挑选出符合特定设计要求的型号,我们可以遵循一系列明确的步骤。首先,我们需要明确设计目标,例如16位的分辨率、100kHz至1MHz的采样率、单端5V输入以及SPI接口。接下来,可以利用德州仪器(TI)的在线参数搜索工具,在TI的产品目录中找到“数据转换器”部分,进而选择“精密ADC”类别。

在初步搜索中,通过设定分辨率和采样率范围,我们可以将选择范围缩小到71种型号。进一步细化搜索条件,指定单通道单端输入、5V最大输入电压和SPI接口,将使我们的选择范围缩小到四个型号。在这四个型号中,我们可以选择使用率最高的ADS8860,这是一款16位、1MSPS的单端输入模数转换器,具有SPI兼容的串行接口。

最终,为了确保所选ADC能够达到最佳性能,我们需要使用软件工具来设计外部的放大器和RC滤波器参数。这个过程不仅节省了时间,而且确保了所选的ADC能够满足特定的技术规格和应用需求,从而为设计提供了一个精确且高效的解决方案。

六、FSR、Cin、Rsh、tacq等参数解析

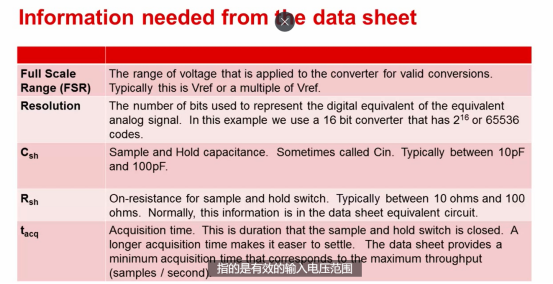

- FSR是满量程电压,即有效的输入电压范围 。一般 FSR就是参考电压或者参考电压的倍数 。

- Resolution 是分辨率 ,代表模拟信号量化数字的位数 。在这个例子中我们用的是16Bit ADC,2 的 16 次方即 65536 个数字代码。

- Csh 是采保电容, 也叫输入电容。 一般在 10pF 到 100pF 之间。

- Rsh 是采样保持开关的导通阻抗 ,一般在 10Ω 到 100Ω 之间 。这些信息在数据手册里都有

- tacq 是采样时间,是指在采样开关闭合的阶段所持续的时间。更长的采样时间会有利于调整精度 ,手册里会提供一个最小的采样时间

七、FSR、Cin、Rsh、tacq等参数在Datasheet中对应的参数

首先满量程 FSR 和分辨率会在参数表里找到,这个例子中满量程就是参考电压 ,分辨率是 16Bit ,内部的采保电容在等效的输入电路中可以找到,注意在这个例子中等效输入电容是采保电容和寄生电容之和 59pF ,采样保持电阻 同样的也可以在等效电路里可以找到是96Ω

如果是数据手册里没有提供采保电阻 Rsh 有一个方法可以近似地进行估算 就是用最小采样时间 去除以一百倍的采保电容 这里可以计算出来的是 53 Ω 虽然实际的值是 96 Ω 并不是完全的精确 但也可以提供一个大致合理的值

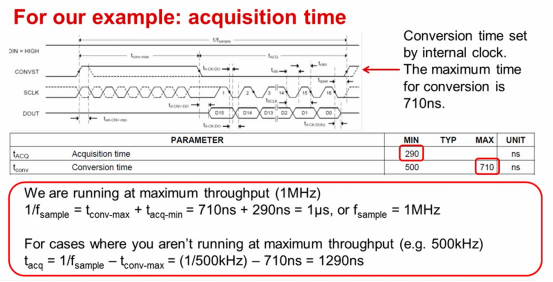

八、吞吐量周期

吞吐量的周期包含了采样时间和转换时间,一般来说吞吐量是最大转换时间和最小采样时间决定的在这个例子中 ADC 并没有跑在最大的吞吐量,采样时间就可以由当下存储量的周期(采样时间)减去最大转换周期(转换时间),这个例子的最大转换周期(转换时间)是由内部的时钟决定的 ,注意, 有一些 Device conversion 的时间是由其他是由外部的一些时钟来决定的 因此需要仔细阅读手册 最后需要提醒的是增加采样时间可以减少对运放带宽的要求同时还会降低整体功耗现在我们已经得到所有相关的信息参数信息  图中红框中分别列出了适用于最大吞吐量以及无法以最大吞吐量运行的采保时间的计算

图中红框中分别列出了适用于最大吞吐量以及无法以最大吞吐量运行的采保时间的计算

九、TI软件工具的使用

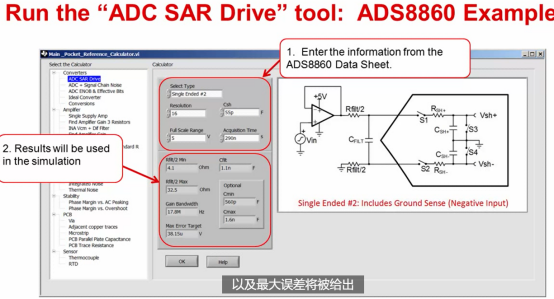

以ADS8860为例,工具的顶部选择 ADC 的输入类型 ->选择单端输入 ->选择16bit 分辨率->填入输入电容及满量程电压和采样时间 ->按下 OK 键 ;那么工具界面将响应给出 RC 值和运放的增益带宽积的值以及最大误差将被给出

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?