SAR ADC 实质上是实现一种二进制搜索算法,即 ADC 每个时钟周期仅得出一位结果,整个量化过程需要多个时钟周期,逐次逼近就是二分查找法不断进行量化趋近,使得数字码不断逼近模拟信号。

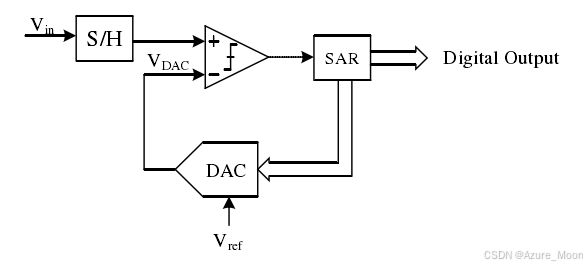

SAR ADC 的基本结构框图如下图所示,其中包括采样保持模块、DAC、比较器和逻辑控制模块。

工作过程如下:首先模拟输入信号 Vin 经过采样保持电路到达比较器的正输入端,然后数字控制逻辑(SAR)的最高位(MSB)置 1,其余位清零,在 SAR 和基准电压 Vref 的控制下,DAC 输出 1/2Vref 送到比较器的负输入端。如果 Vin > 1/2Vref,那么比较器输出为 1,则数字码最高位就为 1;如果 Vin < 1/2Vref,那么比较器输出为 0,则数字码最高位就为 0。

接着确定次高位,把数字控制 SAR 次高位置为 1,如果 MSB=1,则此时 DAC 的输出为 3/4Vref,通过比较 Vin与 3/4Vref 的大小就可以确定次高位了;同理如果 MSB=0,DAC 的输出为 1/4Vref ,比较 Vin与 1/4Vref 的大小从而确定次高位。以此类推,直到 SAR 的所有数字码都确定为止。

由于采用二进制搜索算法使 DAC 的输出逐次逼近模拟输入信号,因此对于 N 位的逐次逼近型ADC 至少需要 N 个转换周期。最后全部确定的数字输出码就是 SAR ADC 的最终输出。

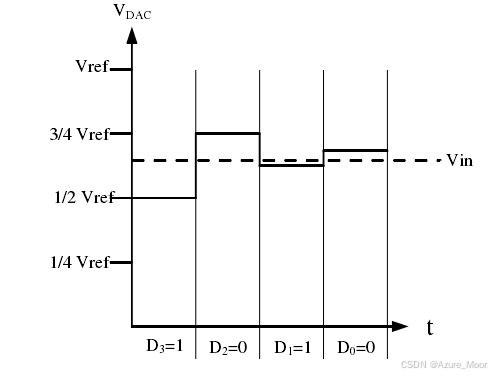

下面用一个简单的 4 位 SAR ADC 来说明工作原理。图中是一个 4 位 SAR ADC 逐次逼近示意图,X 轴表示时间,Y 轴表示 DAC 的输出电压。第一个转换周期,SAR 置为 1000,DAC 输出为 1/2Vref,由于 Vin > 1/2Vref,所以最高位 D3=1;第二个转换周期,SAR 置为 1100,DAC 输出为 3/4Vref,由于 Vin < 3/4Vref,所以D2=0;第三个转换周期,SAR 置为 1010,DAC 输出为 5/8Vref,由于 Vin > 5/8Vref,所以 D1=1;第四个转换周期,SAR 置为 1011,DAC 输出为 11/16Vref,由于 Vin < 11/16Vref,所以最低位 D0=0。所以该 4 位 SAR ADC 的最终的输出码为 1010。

990

990

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?