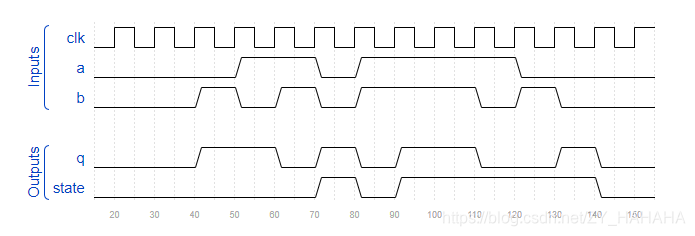

记录一个小题(hdlbits)

Sim/circuit10

这个给q赋值时没有用always ,因为老有一个延时

module top_module (

input clk,

input a,

input b,

output q,

output state );

wire q1,q2,q3,q4;

wire state1;

always@(posedge clk)begin

state=state1;

end

assign q1=({a,b,state}==3'b010)?1:0;

assign q2=({a,b,state}==3'b100)?1:0;

assign q3=({a,b,state}==3'b001)?1:0;

assign q4=({a,b,state}==3'b111)?1:0;

assign q=q1|q2|q3|q4;

assign state1=(~a&b&state)|(a&(~b)&state)|(a&b)

endmodule

做个记录,这题花了几个小时,一是没有想好咋组合,二是时序问题,用always一直有延时

本文记录并解析了一个hdlbits上的时序逻辑题目。该题通过组合逻辑和简单的时序逻辑实现状态转移,难点在于如何正确组合信号及解决由always块带来的延时问题。

本文记录并解析了一个hdlbits上的时序逻辑题目。该题通过组合逻辑和简单的时序逻辑实现状态转移,难点在于如何正确组合信号及解决由always块带来的延时问题。

1695

1695