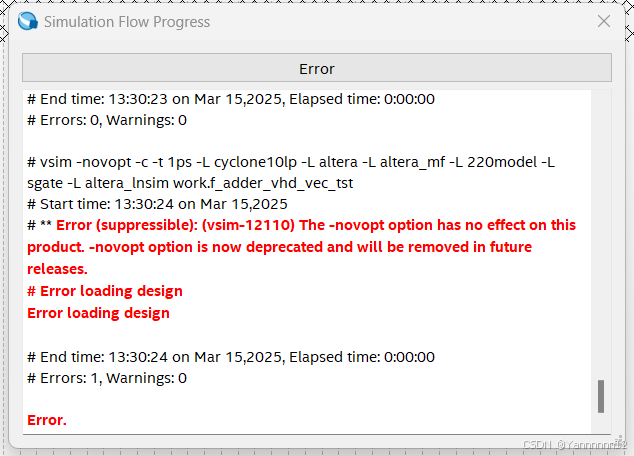

在使用Quartus Prime的过程中遇到了这个问题:

一开始以为是版本问题,Quartus Prime和modelsim不兼容,还重新下了,发现不是。同时也不是环境变量的问题。

最后发现好像是stimulate的过程中尝试使用novopt,但是所用的modelsim版本不支持,同时之后的新版本也弃用了,最后斟酌了半天解决了。

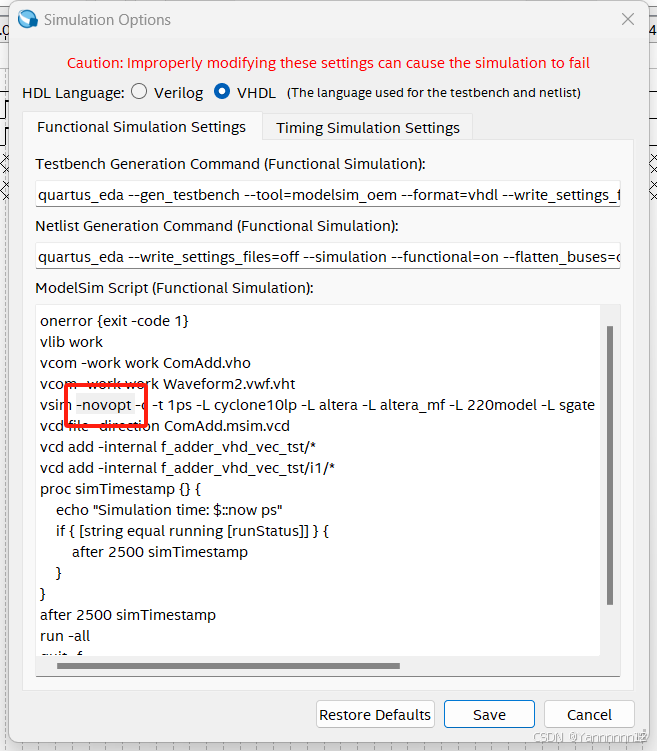

解决方式如下:

在setting里面把红色框的部分去掉就可以了,但是这个每次重新启动stimulate都需要删除掉,如果有更加好的解决方法欢迎讨论~觉得有帮助的就点个赞叭!

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?