实验四 数据通路的组织

- 实验内容

(1) 了解数据通路的组织方法。

(2) 掌握指令执行过程的控制原理。

(3) 设计一个单总线结构的数据通路,支持 Demo_IS 指令系统的取数(LD)、减法(SUB)、双字长分支(JNZ)指令。

(4) 将测试程序存入主存,根据程序执行过程的μOPCmd(微操作命令)序列,控制所设计数据通路,来验证数据通路的正确性。

二、电路设计与实现

- 需求分析:本实验要求支持Demo_IS指令系统的取数(LD)、减法(SUB)、双字长分支(JNZ)指令,其功能分别为:RD←M[(RS)]、RD←(RD)-(RS)、ZF=0 时 PC←addr。其中,RD、RS表示寄存器编号,(Rx)、M[(Rx)]表示寄存器、存储单元的内容,addr为直接寻址方式的地址码,ZF 为上一条指令所产生的结果状态标志。

- 模块划分:由Demo_IS指令系统分析结果可见,ALU应具有加法、减法功能,需产生状态标志ZF,可使用实验二设计的ALU来实现;GPRs应包含4个8位寄存器,具有1个读端口和1个写端口,可使用实验一设计的寄存器组来实现;MEM的容量应≤256×8位,可使用实验三设计的存储模块来实现。为了简化控制,假设PC具有计数功能,可用 Quartus II 提供的lpm_counter 模块来实现。

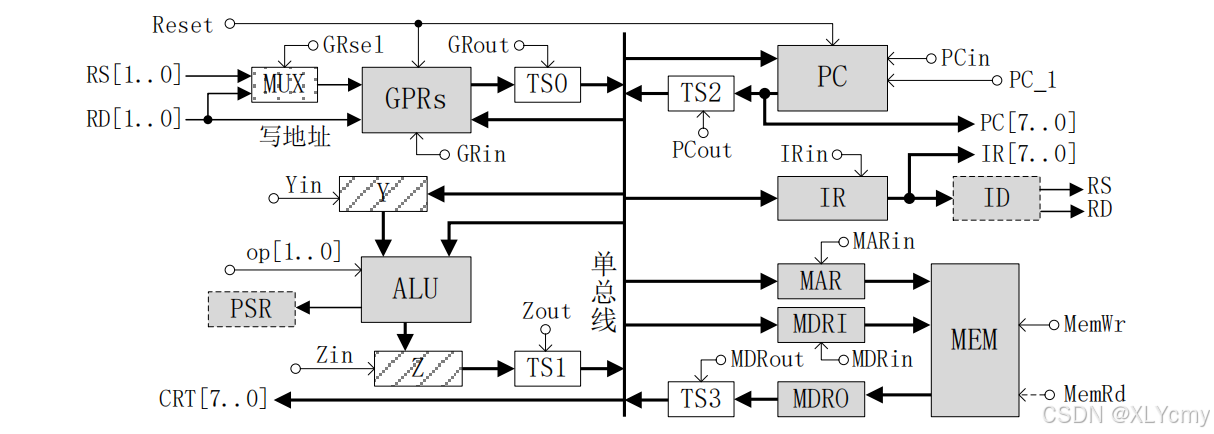

- 引脚组织与器件选择:为了满足Demo_IS中3条指定指令的要求,数据通路的功能部件应包括ALU、寄存器组GPRs、状态寄存器PSR、存储器MEM、程序计数器PC、指令寄存器IR,以及地址寄存器MAR、数据寄存器MDR。

- 电路组成:

三、电路正确性验证

1、电路仿真

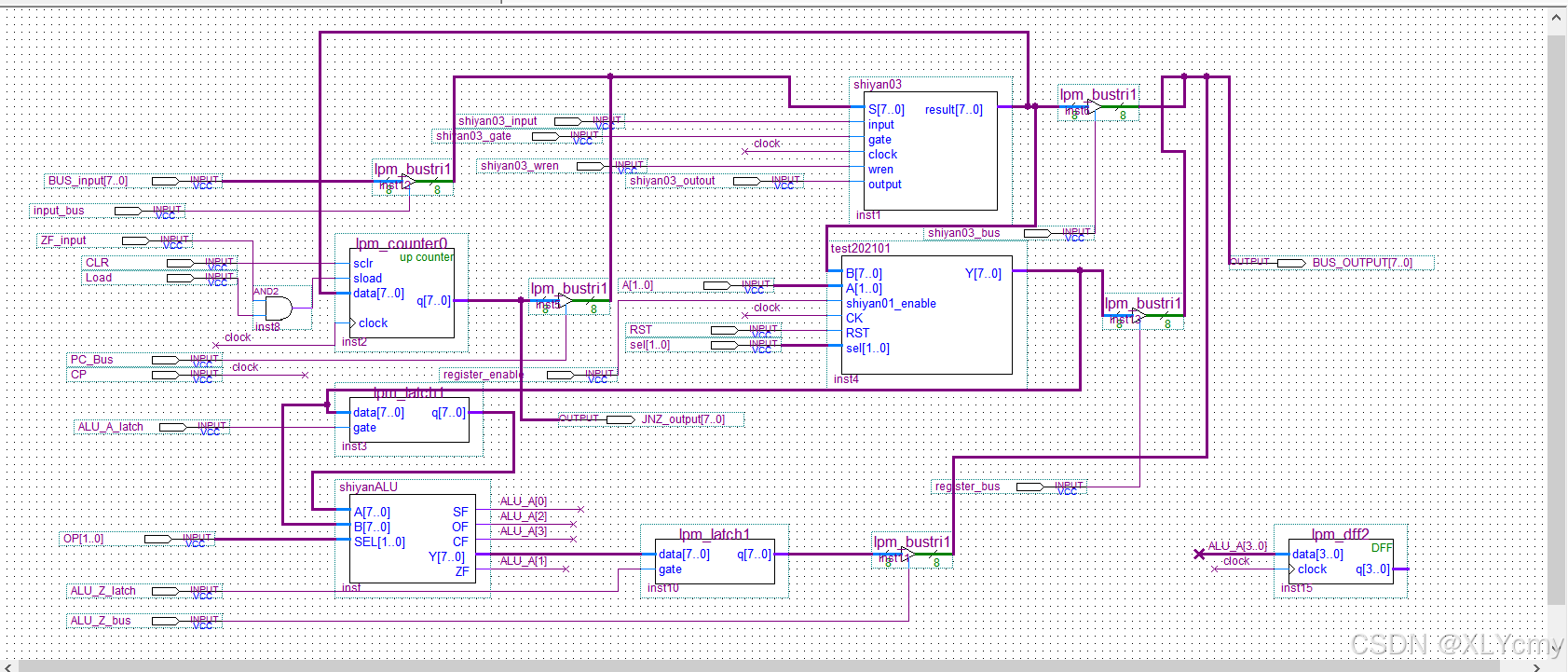

电路图:

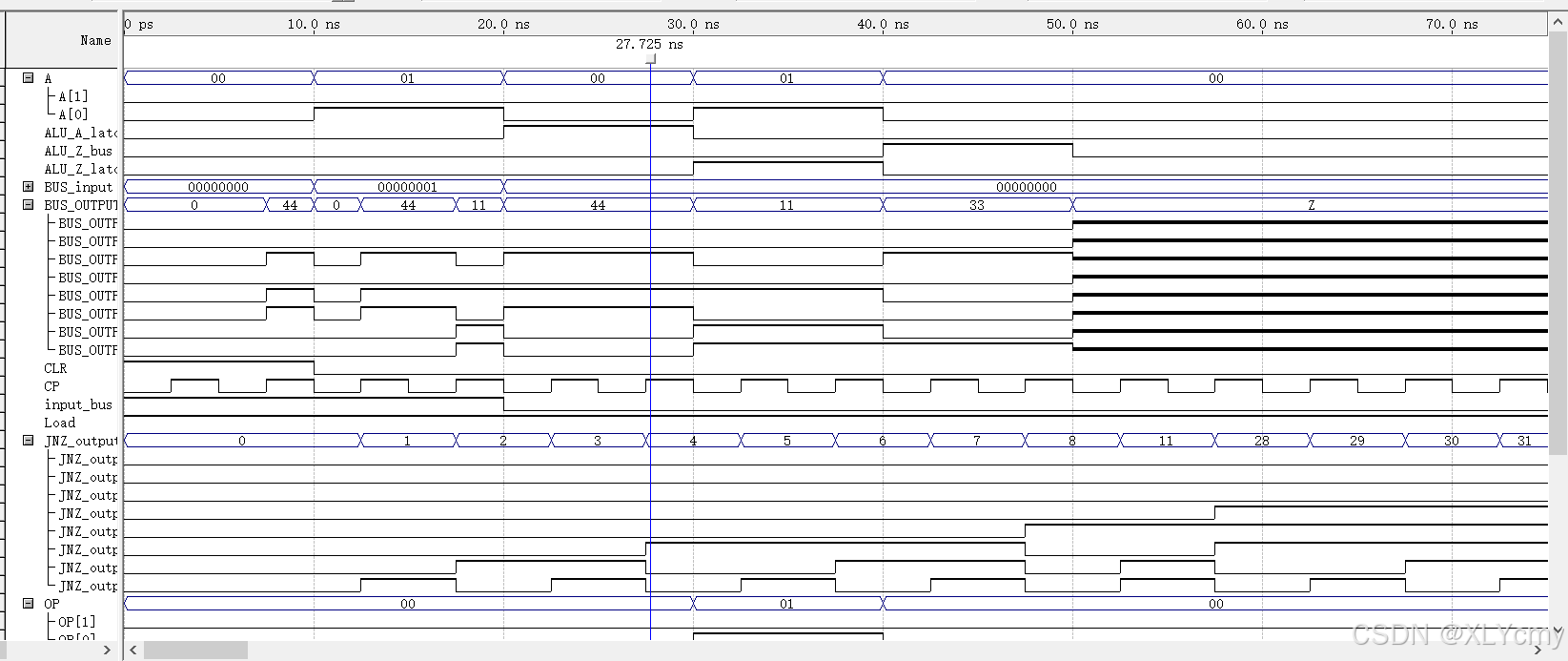

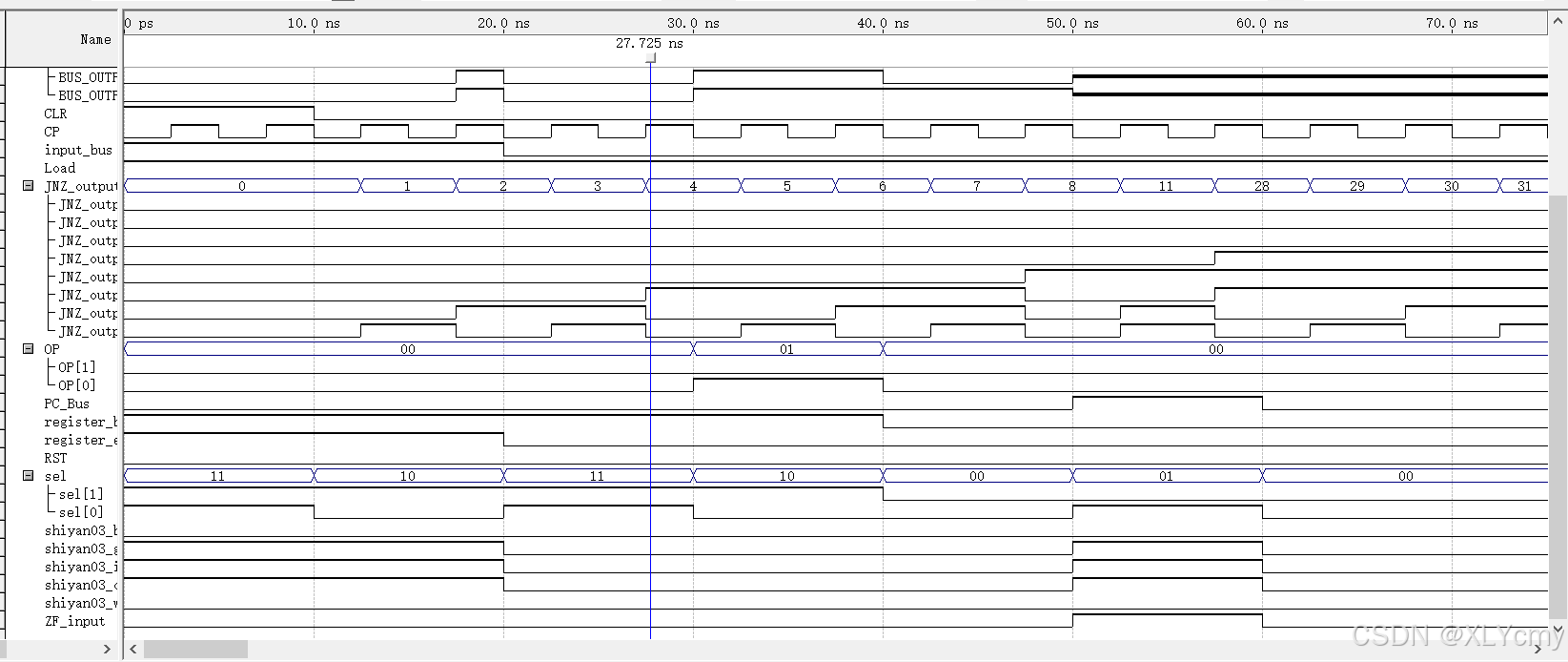

波形图:

- 结果分析

前两组时钟周期实现RD←M[(RS)],将rom中0号单元的内容(44)读入0号寄存器,将rom中1号单元的内容(11)读入1号寄存器,延时分析:由于实验三中使用了lpm_latch(锁存器,在时钟上升沿存入),在第二个时钟周期到来时才有输出。故第二组时钟周期先输出的是latch在第一个时钟周期内存入的地址读出的数据(44),再输出新存入的(11),仿真结果正常。(该延时在后面的PC的JNZ也有体现)

第三到五组时钟周期分别实现Y←(RS),Z←(RD)-(RS),输出结果Z,保证每次只有一个数据流动在总线上,即可避免输出。44-11=33,结果正确。

最后一组时钟周期实现JNZ指令,由于PC连接总线输出总与读取主存产生的输出冲突,故增加输出,专用于PC。使用计数器,在时钟周期开始,将sclr置为高电平对PC进行初始化,此后每个时钟周期自动+1,sload是置数端,load恒置一,ZF=1控制跳转,(为了方便,ZF手动输入,不从ALU接入),此时PC=8,读取主存,ROM第8个单位值为28,在第二个时钟周期上升沿读出,而第一个时钟周期,计数器已完成置数而latch并未存入新地址,读出的上一次地址产生的11,结果正确。

- 实验小结

-

本实验的总线仅有output左边的一小段,将所有器件的输出连接上三态门再连接output,实际上属于局部的点点互连,并不完全是单总线,为了防止冲突,bus_input没有直接连接output,pc也没有直接连接output,是不美观的。

7383

7383

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?