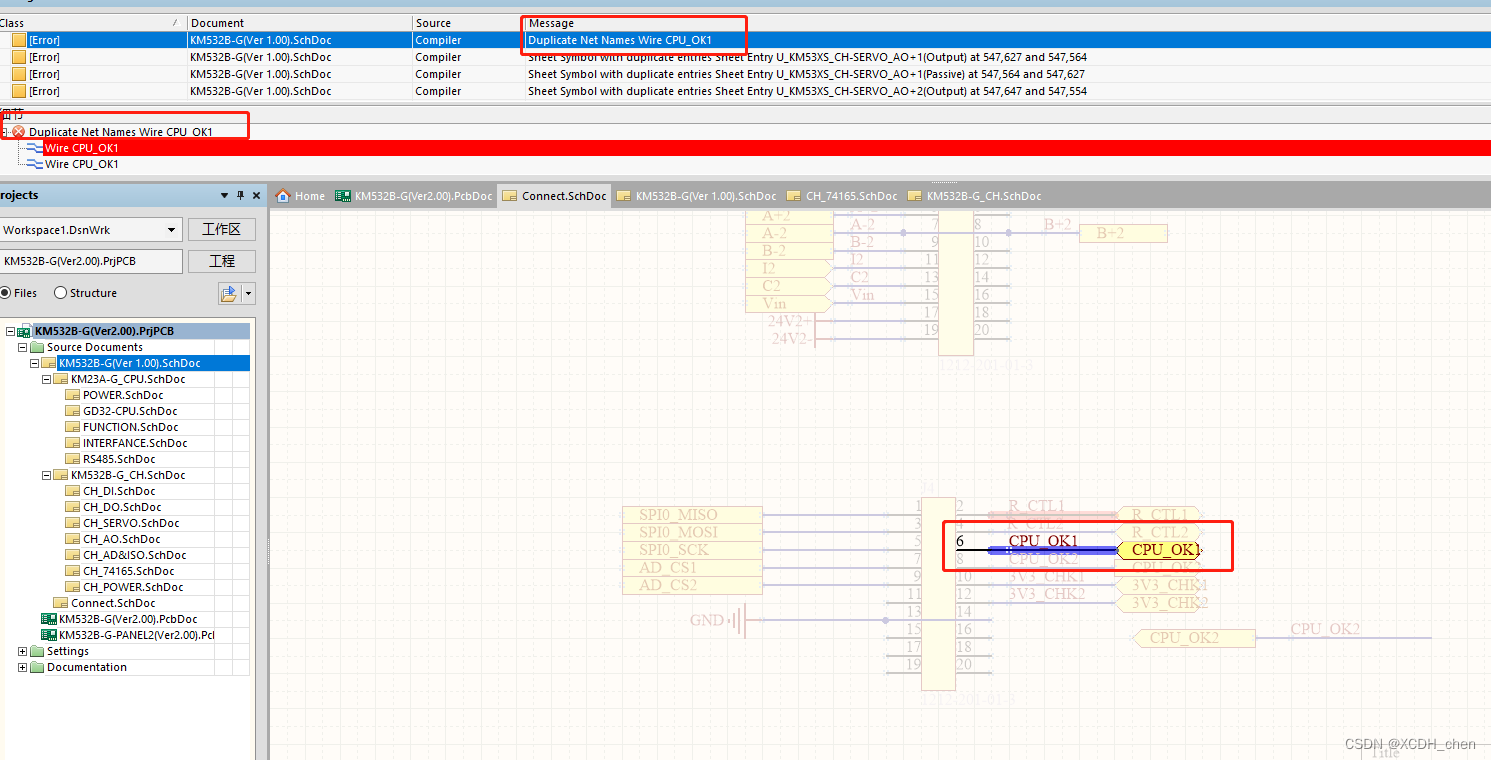

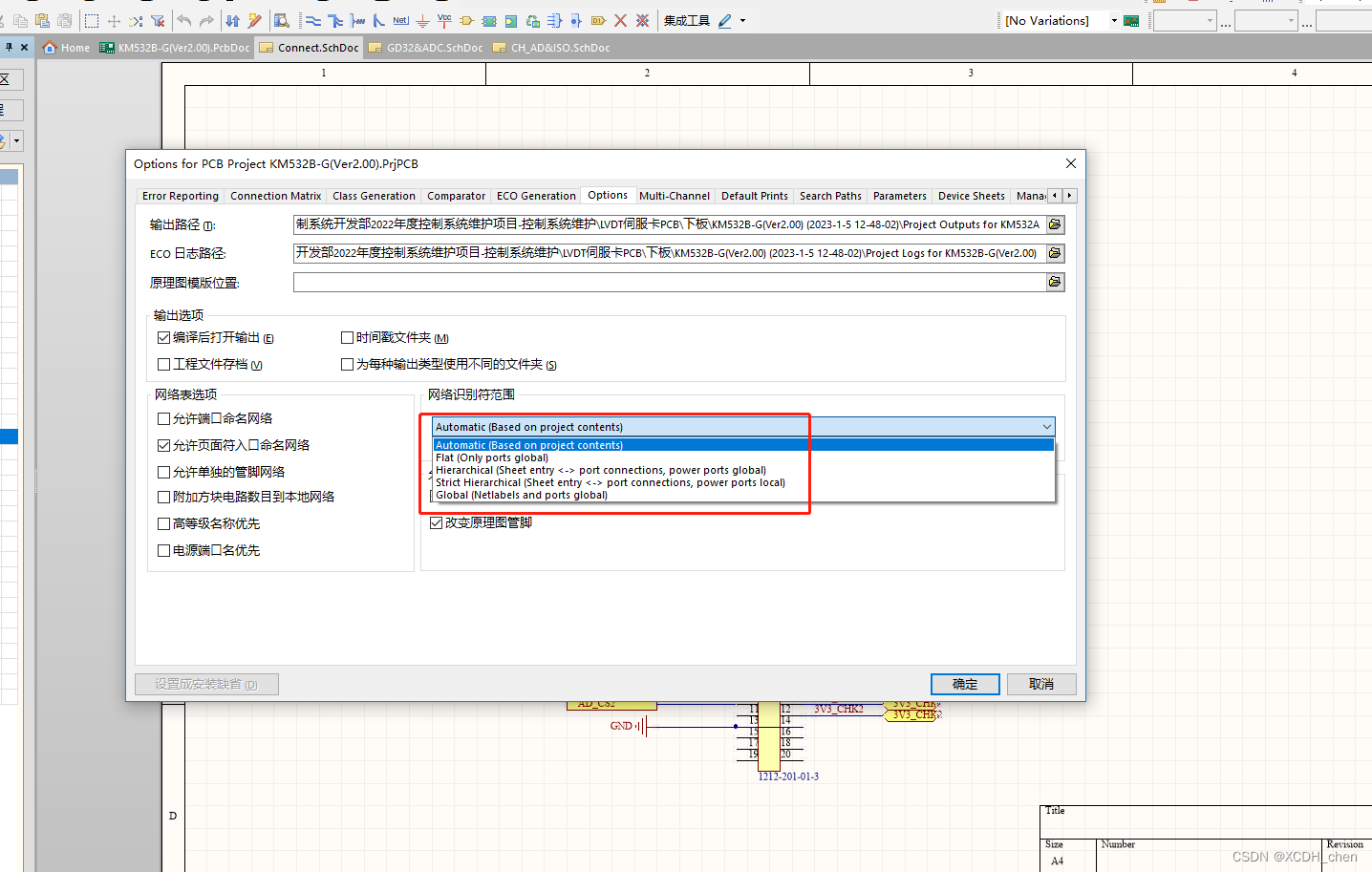

关于Duplicate Net Names Wire网络名重复错误的解决方法有很多,我自己在遇到这个问题的时候,也尝试了许多方法,如更改网络识别符的范围为global,我报错的CPU_OK1的重复命名报错是解决了,可是又会出现更多的其他类型错误;还有的方法是直接忽略这个错误,把网络名重复的优先级更改一下,把报错改成警告,但是从原理图更新到PCB就会出现元器件无法更新的错误,所以我在网络上的方法大概试完了发现还是不能解决。

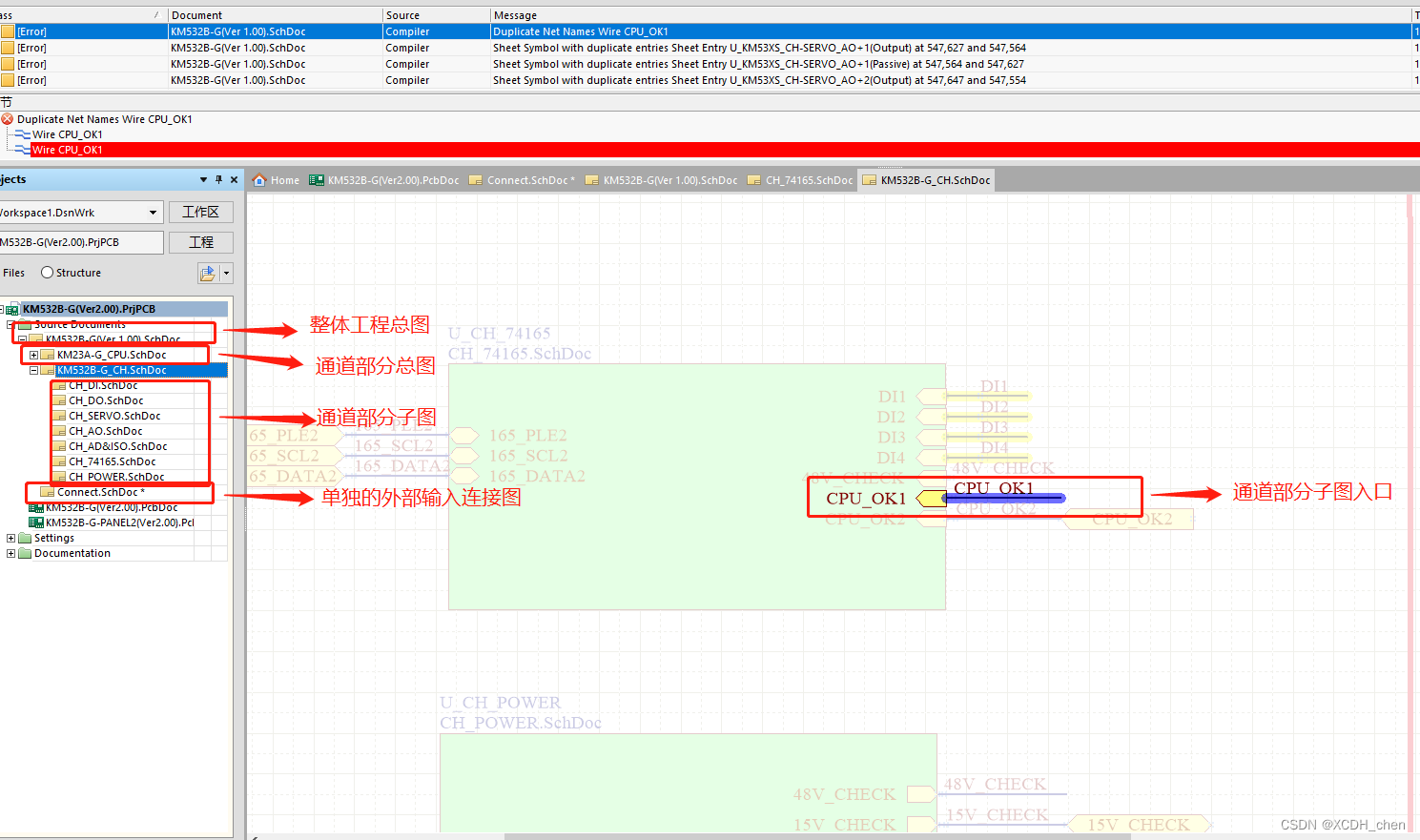

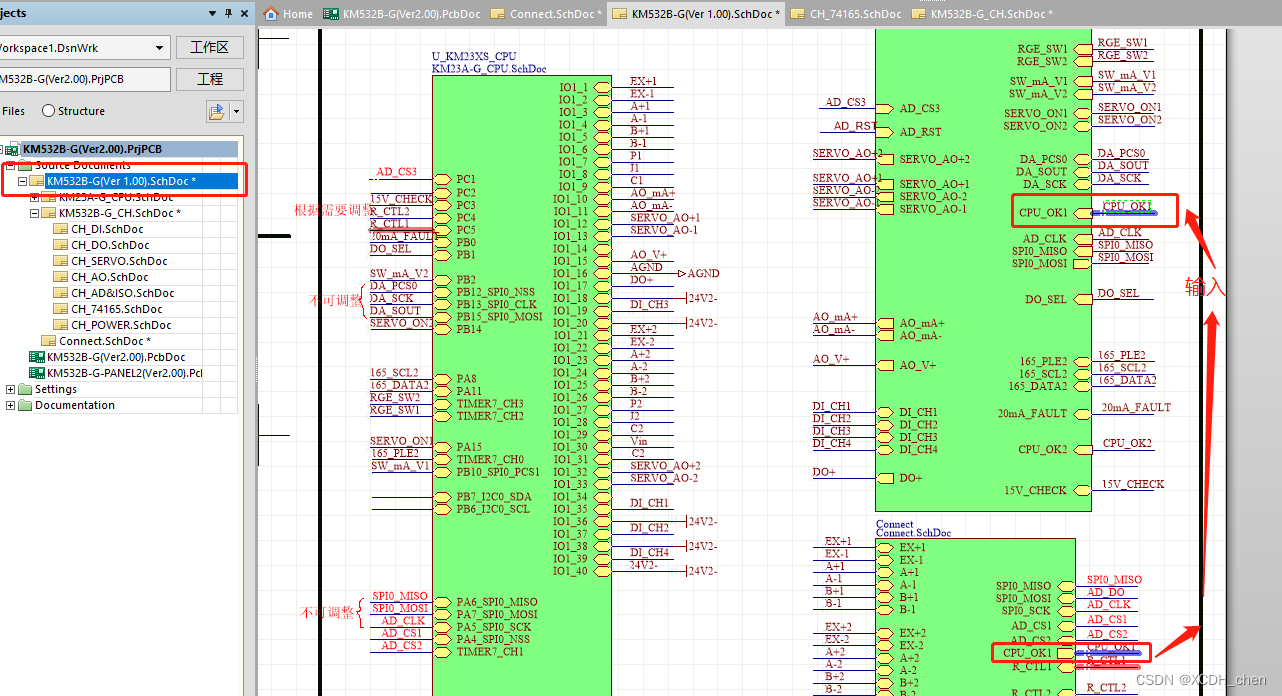

我花了挺长时间后,终于发现问题不在于AD的设置,而在于原理图的总图和子图之间的信号流向的问题。以上的CPU_OK1横跨两张原理图连在一起,所以我们再设计原理图的时候就需要添加页面符来帮助信号进行跨图纸的连接。这个时候我们需要理清子图和总图之间的信号流向问题。

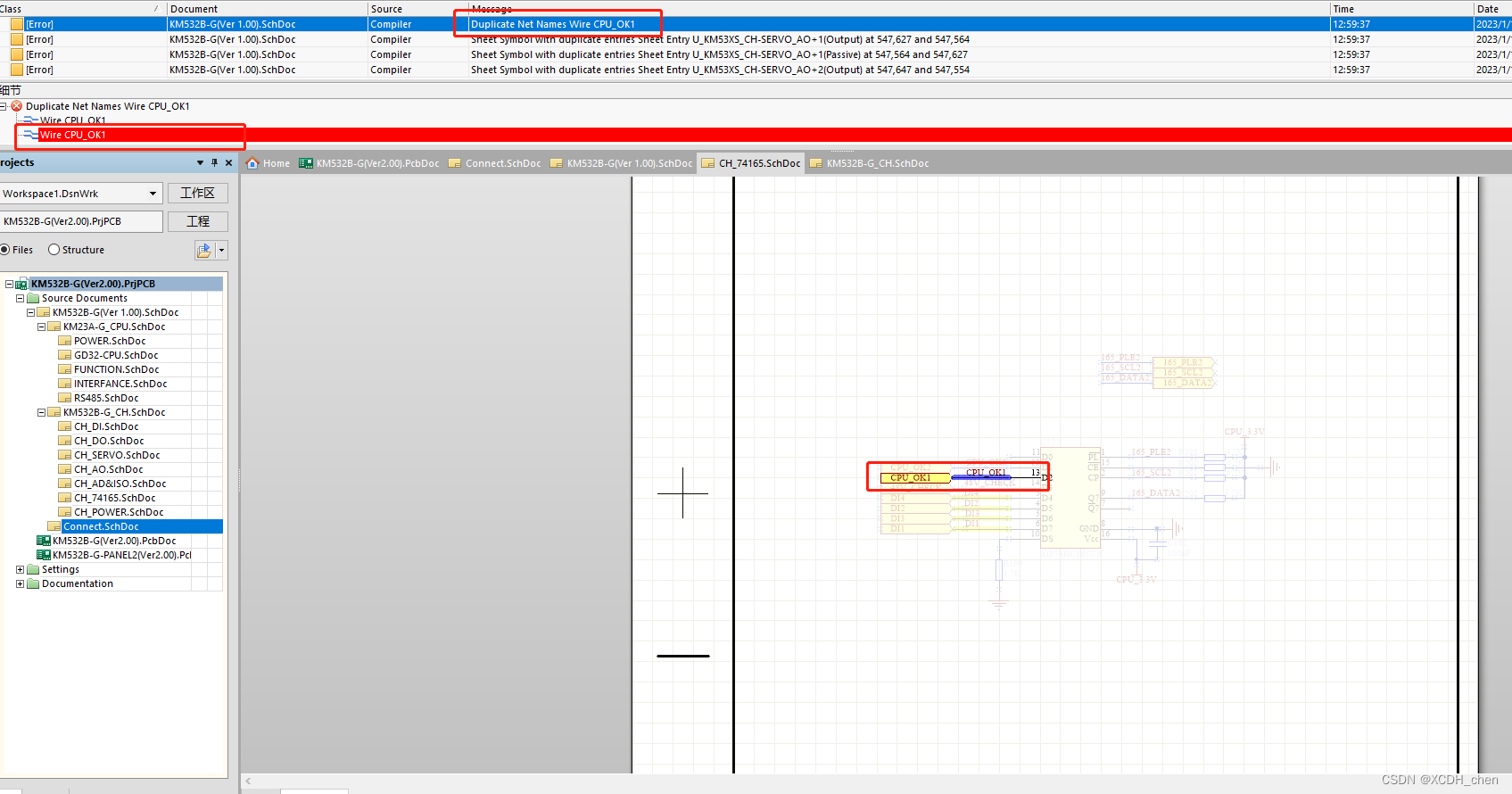

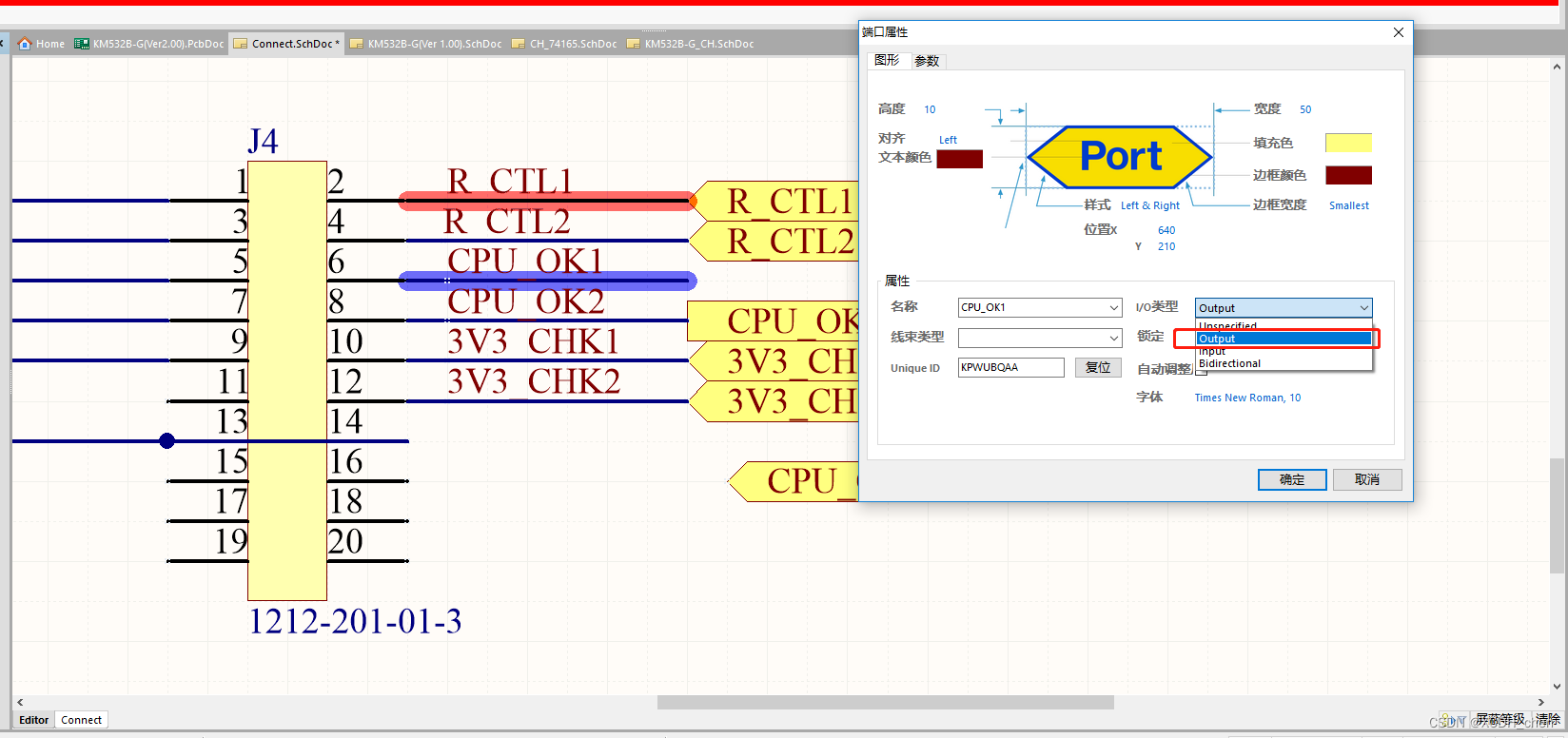

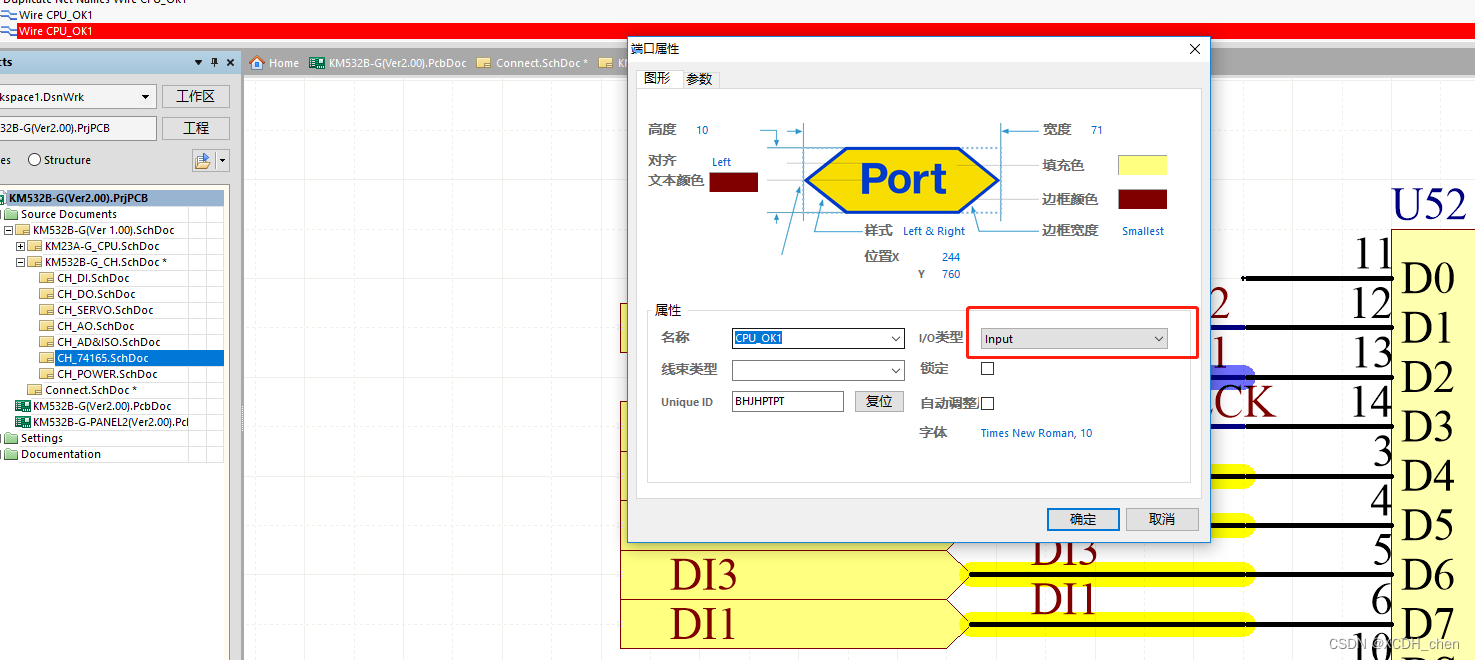

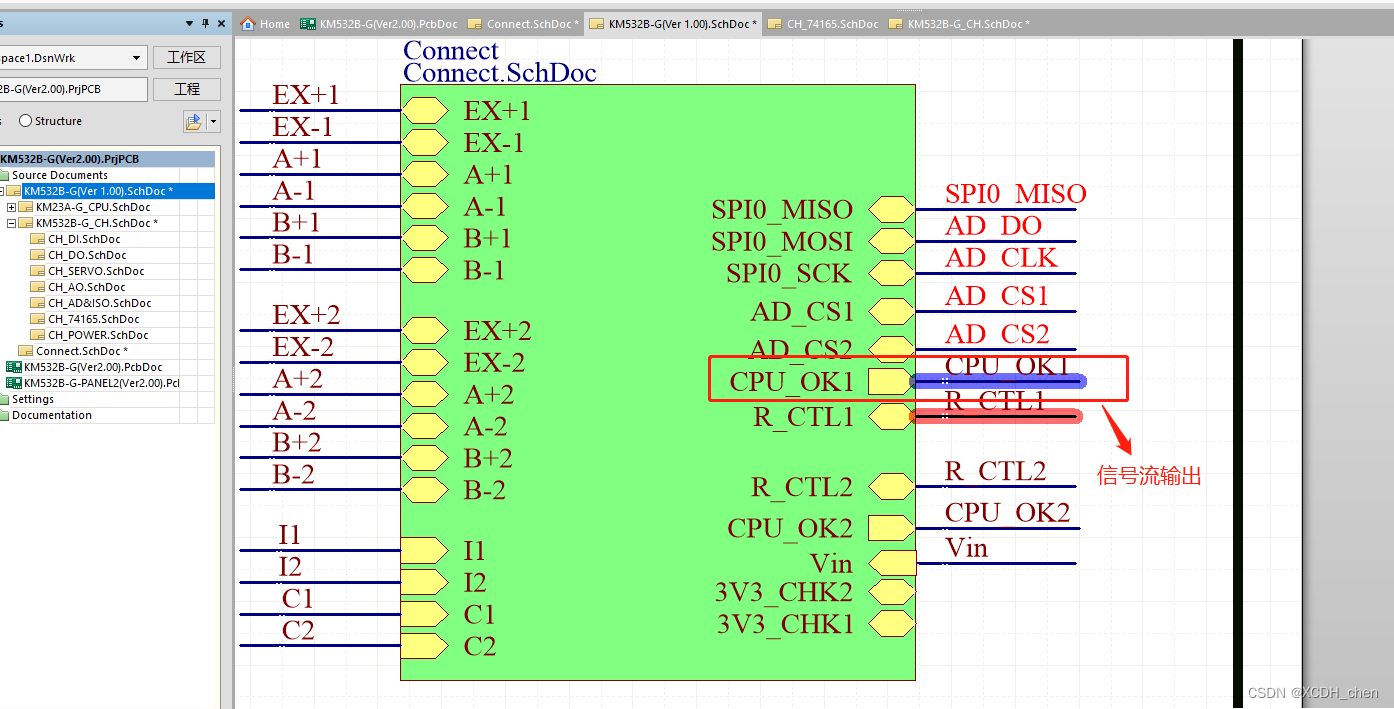

首先,CPU_OK1是在connect这个独立的外部信号输入图纸中,我们输入到这张图纸中的信号需要输出到别的原理图中,所以我们对于页面符Port的I/O类型需要选择Output,并加上网络标签符。

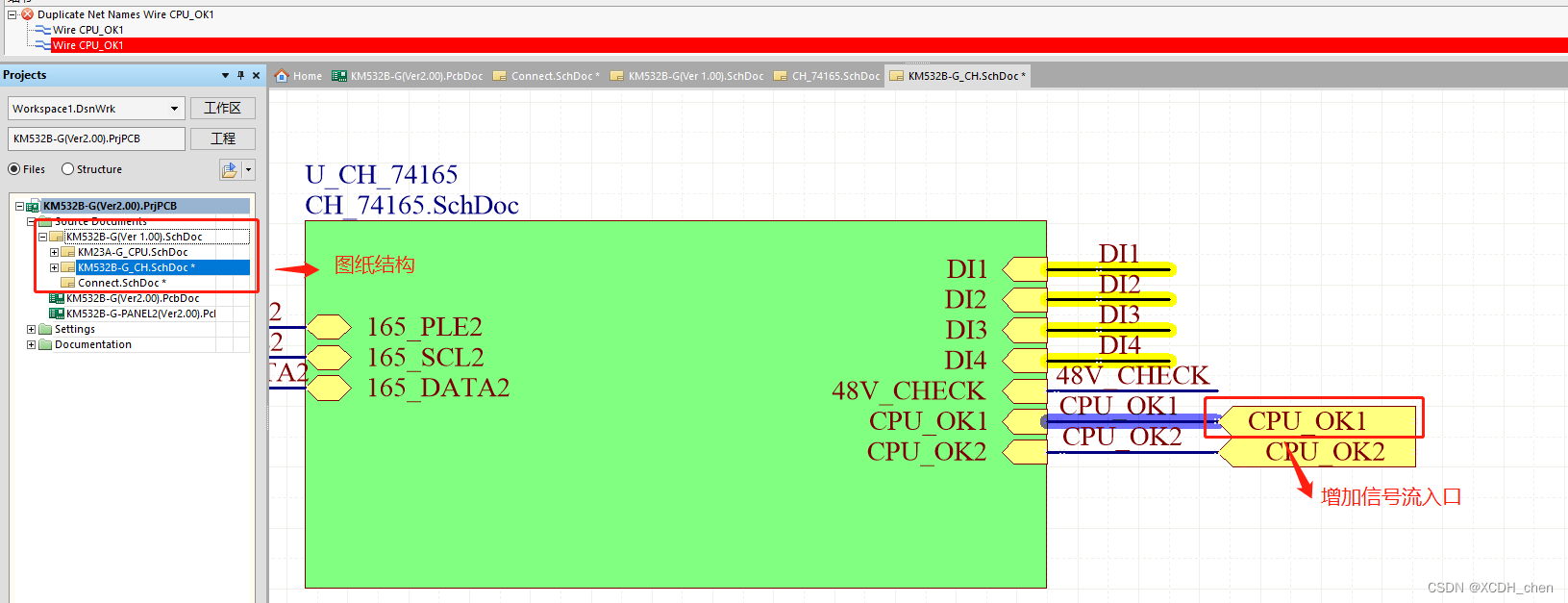

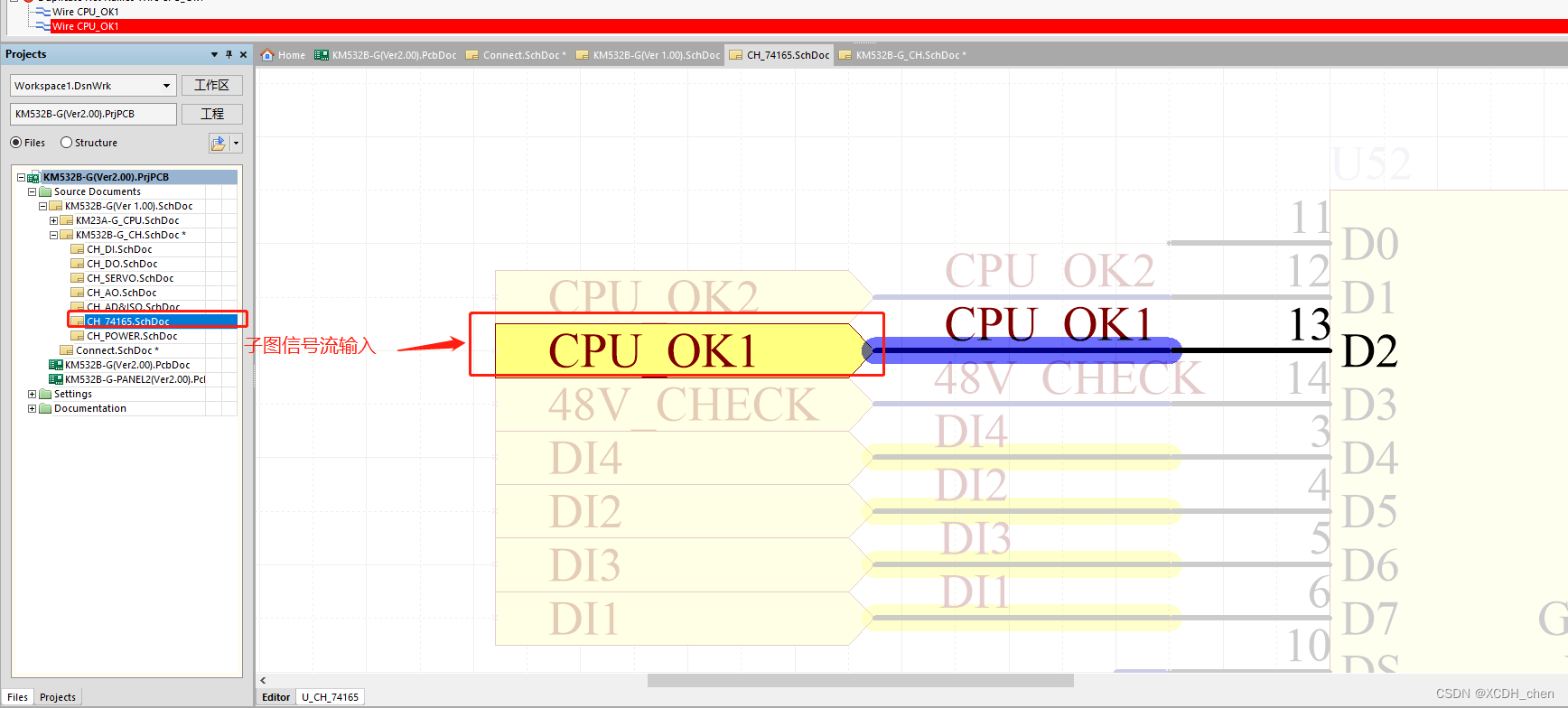

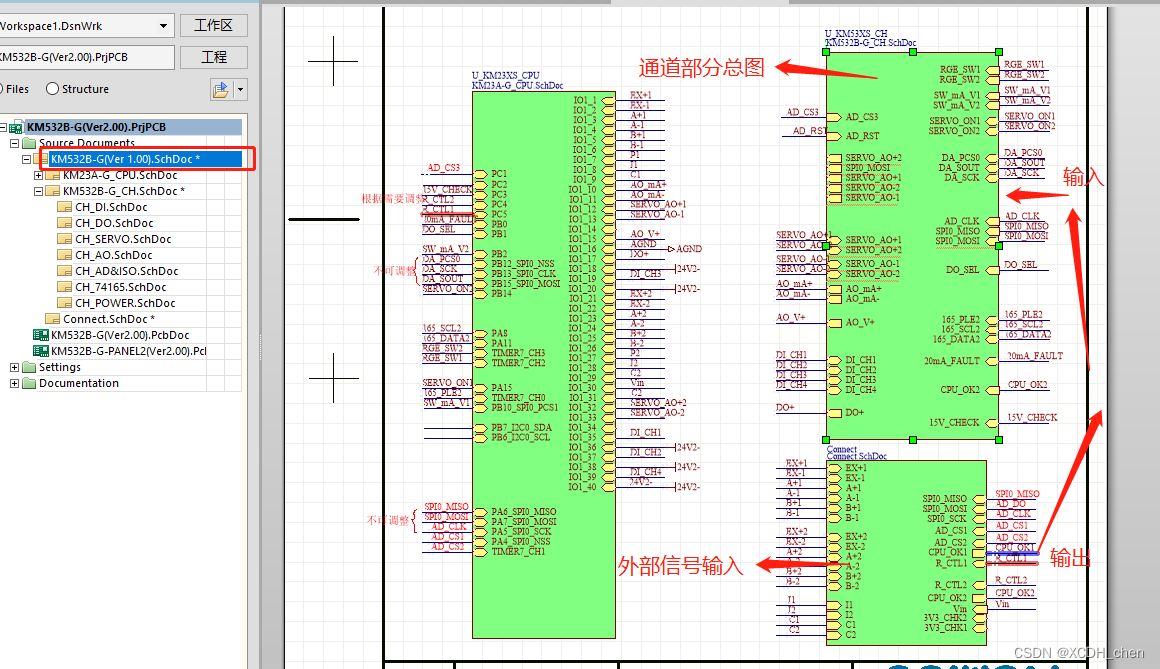

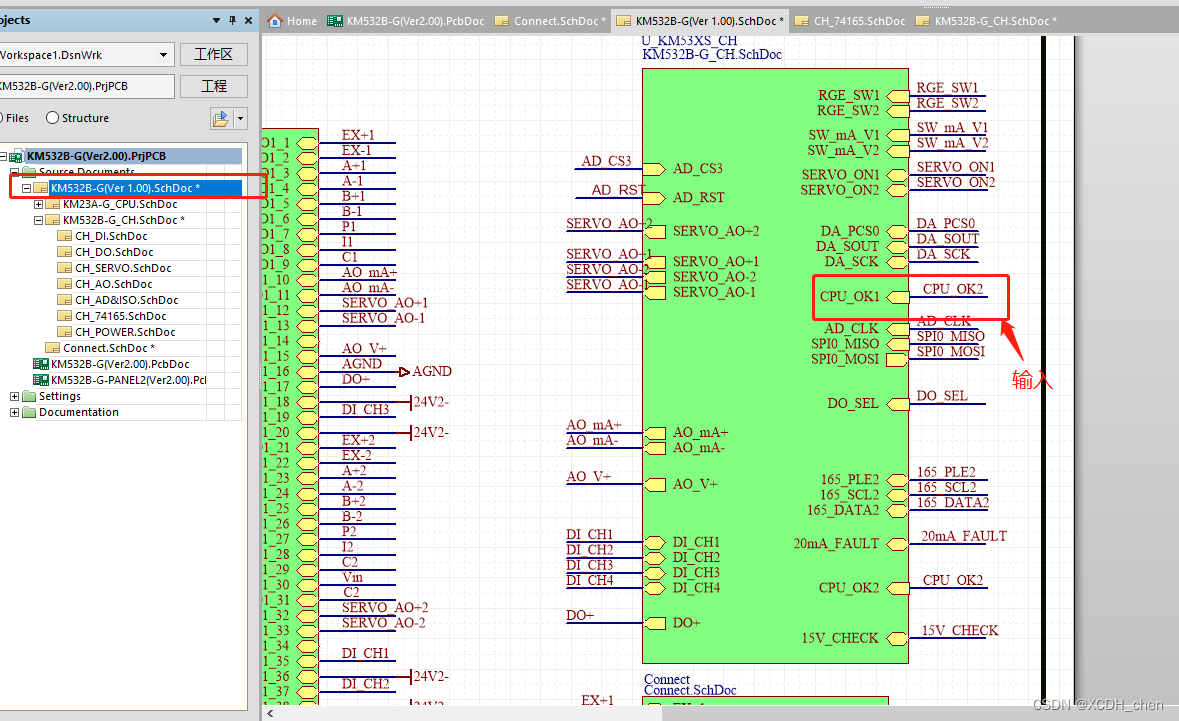

以上是CH通道部分的总图 ,而前面出现Duplicate Net Names Wire网络名重复错误的CH_74165子图包含在总图中,但是缺少了输入部分的页面符,我们信号从connect输出到CH_74165子图需要经过CH通道部分总图流入CH_74165子图,所以要添加输入页面符,Port的I/O类型需要选择Input,效果如下。

信号从CH通道部分总图流入CH_74165子图也需要增加输入符Port的I/O类型需要选择Input。

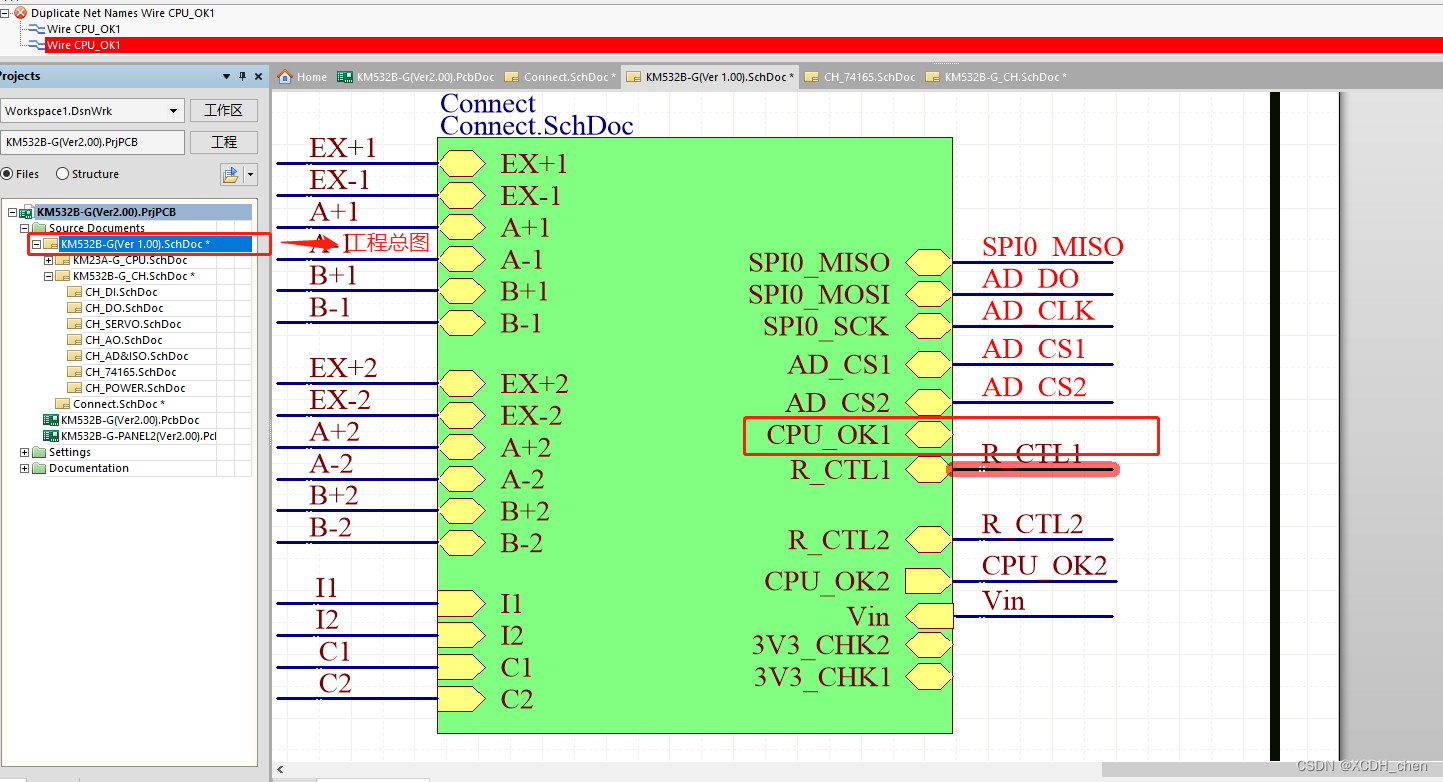

最后我们需要在工程总图需要包含connect到CH通道部分总图的信号流,增加connect外部信号输入图纸页面符输出到CH通道部分总图中,一整个信号的完整流程就添加完毕,这样一来就可以解决Duplicate Net Names Wire网络名重复错误。

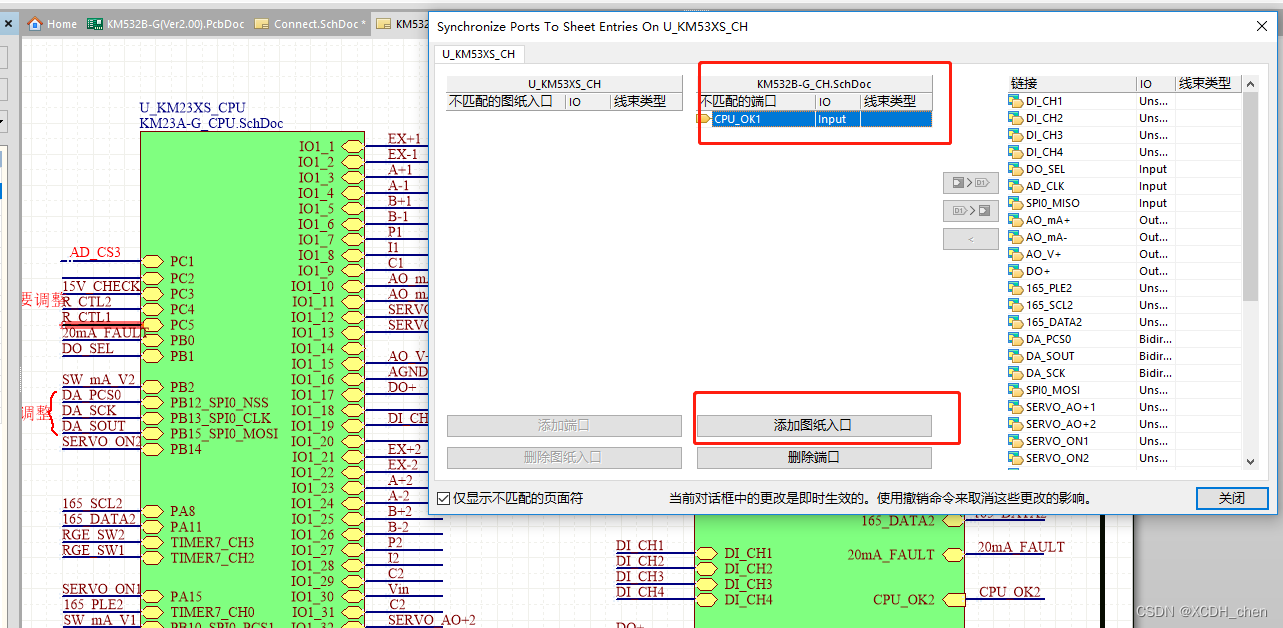

右击绿色的图纸可以检查未添加的Port端口,可以避免有些页面符遗漏造成的错误, 添加页面符操作:同步图纸入口和端口

右击绿色的图纸可以检查未添加的Port端口,可以避免有些页面符遗漏造成的错误, 添加页面符操作:同步图纸入口和端口

信号从connect外部信号输入图纸页面符输出到CH通道部分总图中

信号从connect外部信号输入图纸页面符输出到CH通道部分总图中

总的来说,因为相同网络信号流跨图纸连接而造成的Duplicate Net Names Wire错误其实并不是错误,而是因为信号流没有整理清楚。因为自己没有在优快云上找到这个问题的答案,所以在解决之后记录一下,希望可以帮助到遇到相同问题的朋友们。

文章介绍了在遇到DuplicateNetNamesWire错误时,问题根源在于原理图的信号流向和页面符设置。通过理清信号跨图纸连接,正确设置Port的I/O类型,以及确保页面符的完整,可以解决这个问题。重点在于理解并管理好信号流和图纸间的接口。

文章介绍了在遇到DuplicateNetNamesWire错误时,问题根源在于原理图的信号流向和页面符设置。通过理清信号跨图纸连接,正确设置Port的I/O类型,以及确保页面符的完整,可以解决这个问题。重点在于理解并管理好信号流和图纸间的接口。

1万+

1万+