原文:http://www.cnblogs.com/zhtxwd/archive/2011/12/31/2309176.html

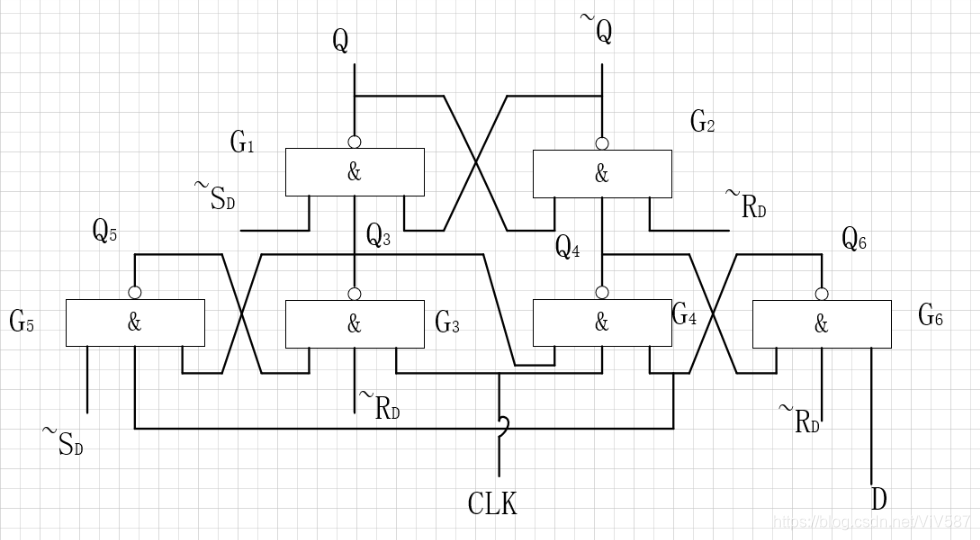

D触发器:

工作原理:

~SD和~RD为触发器的异步置0、置1端。它们不受时钟信号的控制,一旦有效,触发器马上被强迫置0或置1,正常工作时,~SD和~RD均处于高电平状态。

下面分析异步置0、置1输入无效时,电路的工作情况。

1. 在CLK=0期间,触发器输出状态保持不变,因为当CLK=0时,门G4、G3的输出Q3、Q4都是高电平,由G1、G2组成的锁存器处于保持状态,因而触发器的输出Q和~Q保持不变。在此期间,由于Q3=1打开了门G5,Q4=1打开了门G6,所以Q6=~D,Q5=D,为CLK上升沿的到来建立了准备状态。

2. 当CLK由0变为1时,触发器输出的新状态Qn+1=D。因为CLK由0变为1后,门G3、G4被打开,使得Q3=~D,Q4=D(需要注意,这里的D应是上升沿到来前一瞬间已经稳定下来的输入信号D)。若D=0,则输出状态置0,即Qn+1=0;若D=1,则输出状态置1,即Qn+1=1。所以触发器输出的新状态Qn+1=D。

3. 在CLK=1期间,触发器输出状态保持不变。CLK刚从0变为1后,G6的另一个输入端Q4=D,那么,在CLK=1期间如果输入信号D变为~D,则G6的输出Q6一定变为1.Q6置1将不会使由G3和G5组成的RS锁存器的状态发生变化,即Q3=~D仍保持不变(这里因为由与非门组成的RS锁存器低电平为有效信号),而这时门G4的输出为D。这表明,在CLK=1期间,输入信号的改变,不能引起Q3和Q4的变化,因而触发器的输出状态仍然维持CLK上升沿到来时由原来输入信号D作用的结果,而CLK=1期间输入信号D的变化被阻塞掉了,故称此触发器为维持阻塞触发器。

从上面的分析可以知道,输入信号D是在CLK=0的时刻,经过与G5和G6两个与非门的延迟Tsu之后才传输到Q5和Q6端的,然后再CLK跳变为1的时候被锁存到输出端的.

我们假设Tsu=5ns,如果D输入信号在CLK跳变为1之前4ns(<5ns)的时候,才发生变化,那么在CLK跳变为1时,输入信号D还没有传输到Q5和Q6,SR锁存器锁存的将是D变化之前的数据。也就是说D输入信号只有在CLK跳变之前>Tsu的时间里准备好,触发器才能将数据锁存到Q输出端口,也就是所说的要保证信号的建立时间.

在CLK跳变为1之后,Q5和Q6的信号要经过G3和G4两个与非门的延迟(Thd)才能传递到Q3和Q4,构成SR锁存器之前的D输入的阻塞,保证在CLK=1是输入数据变化不会影响锁存结果。

我们假设Thd=5ns,如果D输入信号在CLK跳变为1之后5ns内发生跳变,因为此时Q3和Q4还没发生变化,均为’1’,Q5和Q6的状态将会发生跳变。在CLK=1的时刻,Q3和Q4跟随Q5、Q6的改变也发生跳变,末端SR锁存器的输出Q也发生跳变,造成输出结果不对。 也就是说在CLK跳变为1之后的Thd时间内,D信号不能发生变化,也就是所说的要保证信号的保持时间(Thd)。

同样,复位信号的恢复时间和移除时间可以类似地分析。

本文详细解析了D触发器的工作原理,包括异步置0、置1功能,以及在时钟信号控制下的数据传输过程。特别强调了信号的建立时间和保持时间对于确保数据正确锁存的重要性。

本文详细解析了D触发器的工作原理,包括异步置0、置1功能,以及在时钟信号控制下的数据传输过程。特别强调了信号的建立时间和保持时间对于确保数据正确锁存的重要性。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?