各行各业都有标准,标准的制定能有效的减少沟通成本、提高品质。同样在FPGA内部,为了各个IP核模块能够完美的连接和运行,也为了工程师们减少不必要的工作量,使用标准协议是非常必要的。在Zynq系列芯片中一般使用3种常见的互联协议:Axi Lite、Axi Stream和Axi Full,对应于不同的应用场景。Axi Full用于大量数据的传输,协议复杂但是功能强大,是Axi协议的完整版;Axi Lite是Axi协议的轻量版,用于ARM处理器配置和读取FPGA的寄存器,或者少量数据的传输;Axi Stream应用于数据流的传输,去掉了地址线,协议更加简单也符合图像等流形式数据的传输。

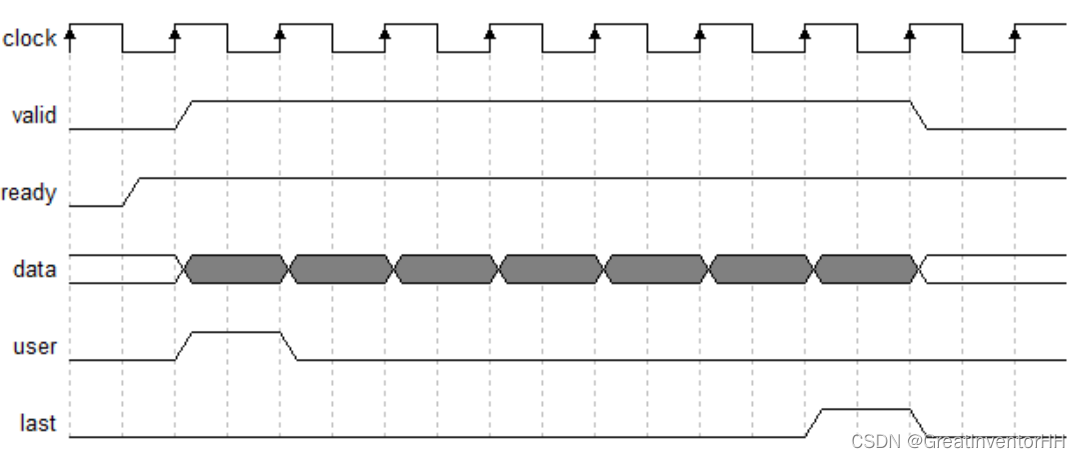

上图是Axi Stream的传输协议波形图,ready用于表示接收数据模块准备好信号,valid表示数据有效信号,只有在valid和ready都为高时数据才有效;user用于传输用户自定义信号,在VDMA中表示帧数据起始,也就是图像的第一个像素;last表示一包数据传输完成,在VDMA中表示一行数据的传输完成。可以说Stream协议非常的简单,也能满足大部分流数据应用,很多Xilinx的IP核都配置了这个标准接口。

除了Xilinx自身的标准协议外,用户还可以把自己的信号打包成标准协议,发布并应用。Vivado提供了许多标准接口协议,可以将用户的信号例化成Bus Inferface的形式,不同模块拥有相同的Bus Inferface且一个是Ma

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

3745

3745

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?