1,建立工程

通过建立工程来指定工程目录,分配工程名称,指定顶层设计的名称等;对合适的FPGA器件以及相应的仿真分析工具进行选择。

顶层设计:也就是把你要进行操作的那个工程放在最顶端。因为quartus 软件只能对顶层工程文件仍进行编译。如果你不把你讲 要进行操作的工程置于最顶层,软件只能对你前一次的过程进行编译。

取个例子,quartus软件就像是Altera公司的里一栋办公楼里的某一个部门,这个部门位于Altera公司这栋办公楼的顶楼,quartus这个部门要处理文件时,要求其他部门亲自把文件送到顶楼来,不然就不予处理,因为Altera给他的职务就是只能在你的办公区(顶楼的那片区域)上班,而不管任何部门,不把文件亲自拿到顶层来quartus你这个部门就不给他做任何事。不然quartus软件就会一直编译之前拿到顶层来的文件。另外顶层文件名和工程名一致即module

所以,在编译工程时,注意置顶,不然有时候提示的错误都让你丈二的和尚-----------摸不着头脑。(*^__^*) 嘻嘻……

2.设计输入

主要输入方法有原理图输入和硬件描述语言输入等。

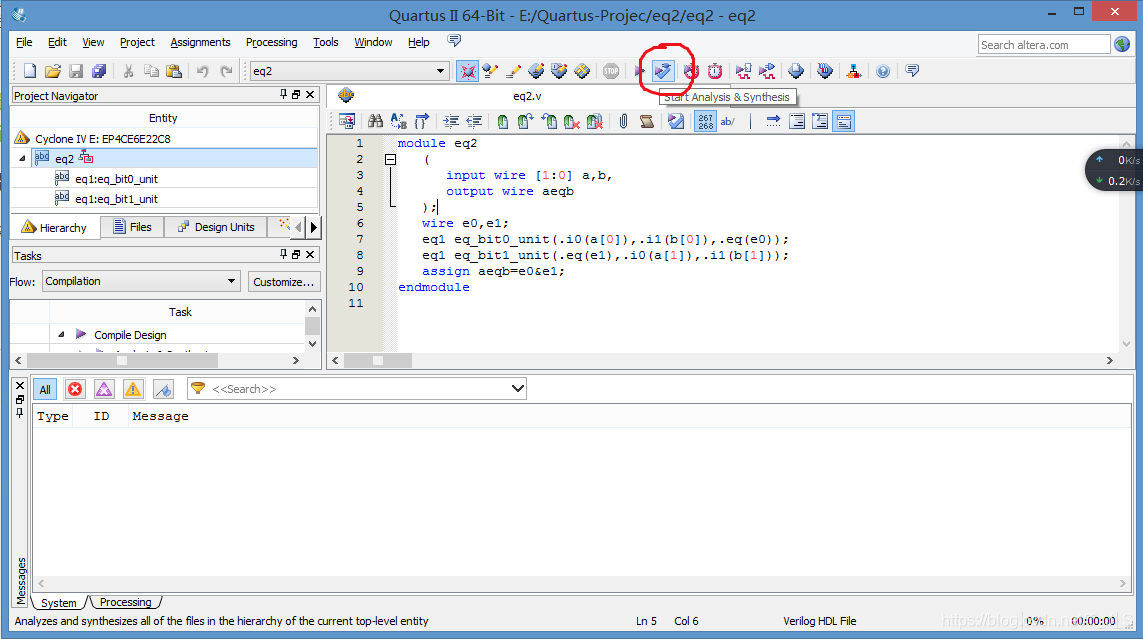

3.综合

我们直接将系统功能通过HDL语言描述出来时,FPGA最终是要用到逻辑门来实现这些描述的功能。综合就是将较高抽象层次(逻辑功能描述)的描述编译转化为较低层次的描述(由与门、或门、非门、RAM、触发器等基本逻辑单元组成的电路之间连接关系的描述)。下图(start Analysis&Synthesis)就是综合按钮。

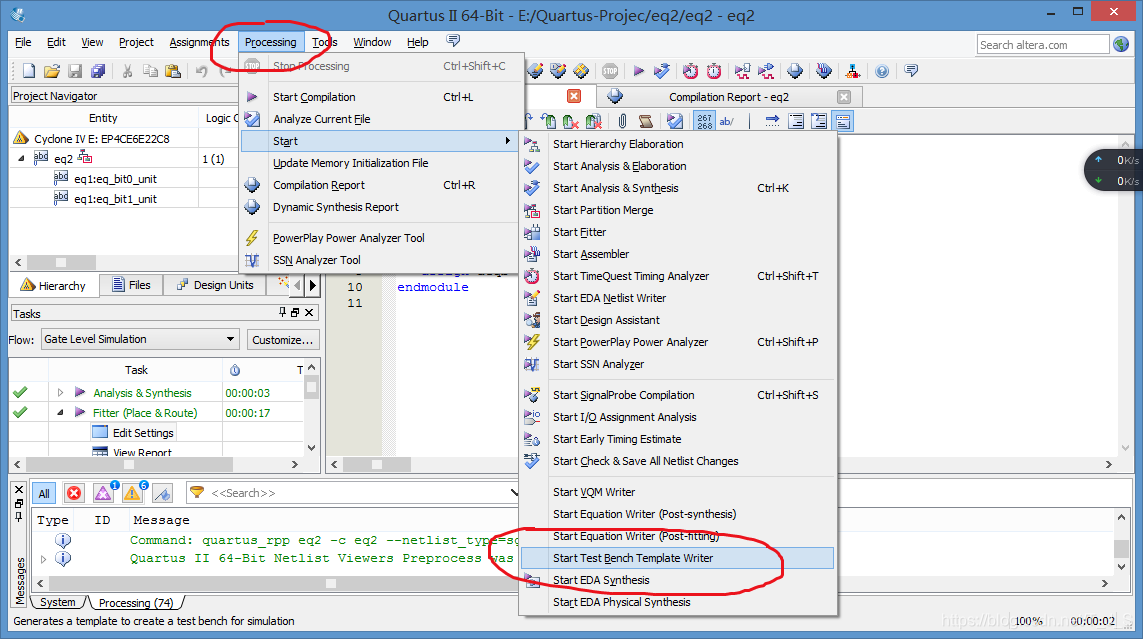

4.功能仿真

就是将系统的逻辑功能仿真出来,也称为前仿真。不需要适配具体的FPGA型号,只关心设计的系统是否能够实现预期的功能。由于没有具体的FPGA对象,所以,功能仿真不含有时序延迟信息,无法判断竞争与冒险等问题。

Modelsim调用来完成。编写Testbench。最后调用即可,这里只是简单的论述一下。

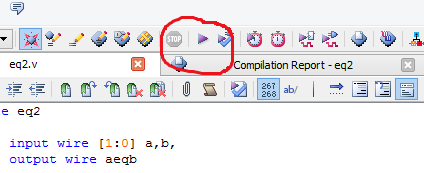

5编译适配

在综合里已经将系统的逻辑功能转化成了门电路和电路之间的连接关系。但不同FPGA的门电路的布局是不同的。适配就是指定具体的FPGA器件中,使之产生最终的下载文件。下图三角符合按钮就是。

6.时序仿真

由于有了具体FPGA器件信息,所以时序仿真除了仿真具体的系统功能以外,还要仿真系统的时序延迟情况,可以分析出系统速度是否合适、是否出现竞争冒险等现象,是比较接近具体硬件电路的仿真形式。时序仿真也叫后仿真。

Modelsim调用来完成。编写Testbench。最后调用即可,这里只是简单的论述一下。

7.编译下载。

以上7个步骤中追重要的是综合、时序仿真。综合要看程序占用多少逻辑资源,选择FPGA。接下来是时许仿真,看程序是否出现毛刺等现象。最后编译下载查看是否成功。

251

251

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?