触发器是最基本的时序元件,其中D触发器是应用最广范的。

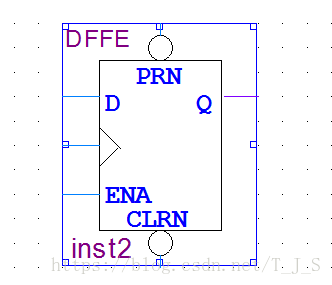

边沿型D触发器包含时钟信号端口(图中包含三角型标记的端口)、复位端口CLR、置为端口PRE、使能端口ENA、输入数据端口D、输出端口Q。

D触发器执行过程:首先,判断复位端口是否连接信号,如果连接信号,在编写代码时要对电路进行复位操作,复位结果输出置0;其次,判断置位端口是否连接信号,如果连接信号,在编写代码时,要进行置位操作;最后,判断使能端口是否连接信号,如果有,根据情况进行使能。如果为真,上升或下降沿到来时,进行数据传输。

D触发器执行过程:首先,判断复位端口是否连接信号,如果连接信号,在编写代码时要对电路进行复位操作,复位结果输出置0;其次,判断置位端口是否连接信号,如果连接信号,在编写代码时,要进行置位操作;最后,判断使能端口是否连接信号,如果有,根据情况进行使能。如果为真,上升或下降沿到来时,进行数据传输。

module DFF(d,clk,q)

input d,clk;

output q;

reg q;

always @(posedge clk)//上升沿

q=d;

endmodule

上述是经典的D触发器程序,遇见这样的always块就是D触发器的应用。加上复位、置位、使能的话,用if语句。

异步复位与置位:触发器的复位和置位与时钟信号无关。

always@(posedge clk or negedge rst or posedge set)

begin

if(~rst)

q=0;

else if(set)

q=1;

else

q=d;

end

同步复位与置位:指在硬件电路中,复位与置位信号只有在时钟上升沿或下降沿到来的时候才进行复位与置位操作。其他时间无效。

always@(posedge clk )

begin

if(~rst)

q=0;

else if(set)

q=1;

else

q=d;

end

本文深入解析了D触发器的工作原理及应用,介绍了其关键组成部分,包括时钟信号、复位、置位、使能和数据输入输出端口。通过代码示例展示了D触发器在同步与异步复位置位条件下的行为,以及如何使用Verilog实现。

本文深入解析了D触发器的工作原理及应用,介绍了其关键组成部分,包括时钟信号、复位、置位、使能和数据输入输出端口。通过代码示例展示了D触发器在同步与异步复位置位条件下的行为,以及如何使用Verilog实现。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?