写在前面

万万没想到秋招春招找工作以C++为主、FPGA为辅,最后去了FPGA岗位

也算是不忘初心,回归了从研一就开始学的FPGA老本行

但之前学FPGA的时候并没有养成写笔记的习惯,导致后面有些东西都比较模糊,因此打算从今天开始从头来过,把之前基础知识和新学到的FPGA相关内容记录下来,记录我的FPGA之路!

这是某本书上的第一章节,感觉写的还是挺不错的,大概看了一下让我回想起很多知识,个人感觉比较适合学习了Verilog语法和数电之后上板的同学

1. 原理介绍

1.1 数码管

数码管按段分可分为七段数码管和八段数码管,区别就是八段数码管多了个小数点

常见的数码管有两种:共阴数码管和共阳数码管

共阴数码管就是高电平亮,低电平灭;共阳数码管就是低电平亮,高电平灭。

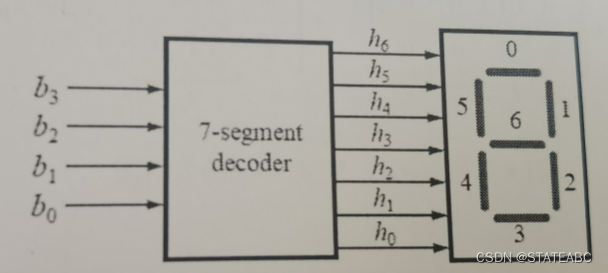

1.2 译码器

七段数码管译码器的结构图如下,4个输入变量能够组合成十六进制数字0-F,那么相应的输出就可以通过七个输出变量,表示成数字,从而达到译码的效果。

这里译码器有两种写法,一种比较复杂,就是通过对应的真值表或者卡诺图写出h的逻辑表达式,写起来比较繁琐,就直接放代码,通过逻辑门(assign赋值语句)实现译码器

assign h[6] = (~b[3] & ~b[2] & ~b[1]) | (~b[3] & b[2] & b[1] & b[0]) | (b[3] & b[2] & ~b[1] & ~b[0]);

assign h[5] = (~b[3] & ~b[2] & ~b[0]) | (~b[3] & ~b[2] & b[1]) | (~b[3] & b[1] & ~b[0]) |(b[3] & b[2] & ~b[1] & b[0]);

assign h[4] = (~b[3] & b[0]) | (~b[3] & b[2] & ~b[1]) | (b[3] & ~b[2] & ~b[1] & b[0]);

assign h[3] = (~b[2] & ~b[1] & b[0]) |

本文介绍了FPGA的基础知识,包括数码管的类型和工作原理,七段数码管译码器的实现,D触发器的特性及其同步、异步复位的区别,以及寄存器和计数器的概念和Verilog代码实现。通过示例代码展示了如何在FPGA中设计数码管显示和计数器功能。

本文介绍了FPGA的基础知识,包括数码管的类型和工作原理,七段数码管译码器的实现,D触发器的特性及其同步、异步复位的区别,以及寄存器和计数器的概念和Verilog代码实现。通过示例代码展示了如何在FPGA中设计数码管显示和计数器功能。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

3244

3244

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?