- 在TI的C2000系列微控制器(如DSP28335)中,GPIO引脚被组织成不同的端口(例如A、B、C等,A对应0到31),每个端口有自己的一组寄存器来控制和读取状态。

GPIO寄存器分类

1. 控制寄存器(Control Registers)

- 用于配置外设的功能和行为。它们通常包含位域,每个位或几位组合在一起控制某个特定的功能。例如,

GpioCtrlRegs是一个典型的控制寄存器集合,用于配置GPIO引脚的方向、复用功能等。

struct GPIO_CTRL_REGS {

union GPACTRL_REG GPACTRL; // GPIO A Control Register (GPIO0 to 31)

union GPA1_REG GPAQSEL1; // GPIO A Qualifier Select 1 Register (GPIO0 to 15)

union GPA2_REG GPAQSEL2; // GPIO A Qualifier Select 2 Register (GPIO16 to 31)

union GPA1_REG GPAMUX1; // GPIO A Mux 1 Register (GPIO0 to 15)

union GPA2_REG GPAMUX2; // GPIO A Mux 2 Register (GPIO16 to 31)

union GPADAT_REG GPADIR; // GPIO A Direction Register (GPIO0 to 31)

union GPADAT_REG GPAPUD; // GPIO A Pull Up Disable Register (GPIO0 to 31)

Uint32 rsvd1;

union GPBCTRL_REG GPBCTRL; // GPIO B Control Register (GPIO32 to 63)

union GPB1_REG GPBQSEL1; // GPIO B Qualifier Select 1 Register (GPIO32 to 47)

union GPB2_REG GPBQSEL2; // GPIO B Qualifier Select 2 Register (GPIO48 to 63)

union GPB1_REG GPBMUX1; // GPIO B Mux 1 Register (GPIO32 to 47)

union GPB2_REG GPBMUX2; // GPIO B Mux 2 Register (GPIO48 to 63)

union GPBDAT_REG GPBDIR; // GPIO B Direction Register (GPIO32 to 63)

union GPBDAT_REG GPBPUD; // GPIO B Pull Up Disable Register (GPIO32 to 63)

Uint16 rsvd2[8];

union GPC1_REG GPCMUX1; // GPIO C Mux 1 Register (GPIO64 to 79)

union GPC2_REG GPCMUX2; // GPIO C Mux 2 Register (GPIO80 to 95)

union GPCDAT_REG GPCDIR; // GPIO C Direction Register (GPIO64 to 95)

union GPCDAT_REG GPCPUD; // GPIO C Pull Up Disable Register (GPIO64 to 95)

};

GPACTRL

- GPACTRL寄存器是TI的C2000系列微控制器中用于配置GPIO端口A引脚输入同步和滤波行为的一个关键寄存器。它允许开发者对GPIO引脚的输入信号进行更精细的控制,确保外部信号在采样前已经稳定,并且可以根据需要过滤噪声或毛刺。

//----------------------------------------------------

// GPIO A control register bit definitions */

// GPxCTRL寄存器单元内部被分成4组,分别是QUALPRD0~QUALPRD3(8位),每组8位,该8位对应8个GPIO引脚,有着各自相同的时钟周期。不同组之间时钟周期可以相同可以不同。https://blog.sina.com.cn/s/blog_a7c071b30102wp2c.html

struct GPACTRL_BITS { // bits description

Uint16 QUALPRD0:8; // 7:0 Qual period

Uint16 QUALPRD1:8; // 15:8 Qual period

Uint16 QUALPRD2:8; // 23:16 Qual period

Uint16 QUALPRD3:8; // 31:24 Qual period

};

union GPACTRL_REG {

Uint32 all;

struct GPACTRL_BITS bit;

};

// Set input qualifcation period for GPIO25 & GPIO26 inputs

GpioCtrlRegs.GPACTRL.bit.QUALPRD3=1; // Qual period = SYSCLKOUT/2

GpioCtrlRegs.GPAQSEL2.bit.GPIO25=2; // 6 samples

GpioCtrlRegs.GPAQSEL2.bit.GPIO26=1; // 3 samples

GPAQSEL1/2

- GPAQSEL1/2 是TI的C2000系列微控制器中用于配置GPIO引脚输入同步周期的一个寄存器位字段。具体来说,它定义了当GPIO引脚被配置为同步输入时,输入信号需要满足的稳定周期(即在多少个系统时钟周期内保持稳定),以确保可靠的采样。

GpioCtrlRegs.GPAQSEL1.bit.GPIO7 = 0; // Synch to SYSCLOUT,输入时钟同步,不进行采样

GpioCtrlRegs.GPAQSEL2.bit.GPIO26=1; // 3 samples 3次相同采样确定输入,起到滤波作用,防止外部脉冲干扰

GpioCtrlRegs.GPAQSEL2.bit.GPIO25=2; // 6 samples

GpioCtrlRegs.GPAQSEL1.bit.GPIO12 = 3; // asynch input 同步输入

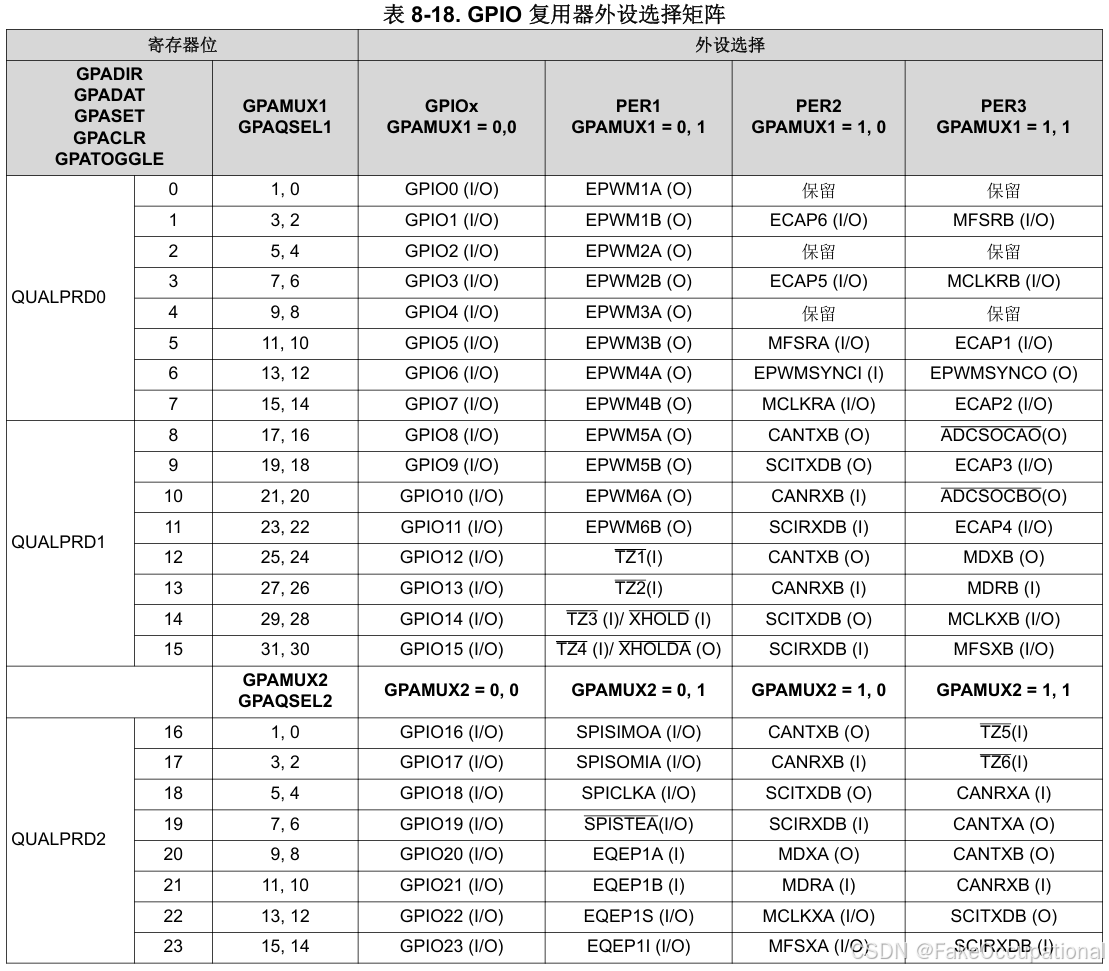

GPAMUX1/2

- GPAMUX1/2 负责的引脚功能选择(GPIO0GPIO15/GPIO16GPIO31)。

GpioCtrlRegs.GPAMUX1.bit.GPIO0 = 1; // GPIO0 = PWM1A

GpioCtrlRegs.GPAPUD.bit.GPIO6 = 0; // Enable pullup on GPIO6

GpioDataRegs.GPASET.bit.GPIO6 = 1; // Load output latch

GpioCtrlRegs.GPAMUX1.bit.GPIO6 = 0; // GPIO6 = GPIO6

GpioCtrlRegs.GPAPUD.bit.GPIO29 = 0; // Enable pullup on GPIO29

GpioCtrlRegs.GPAMUX2.bit.GPIO29 = 1; // GPIO29 = SCITXDA

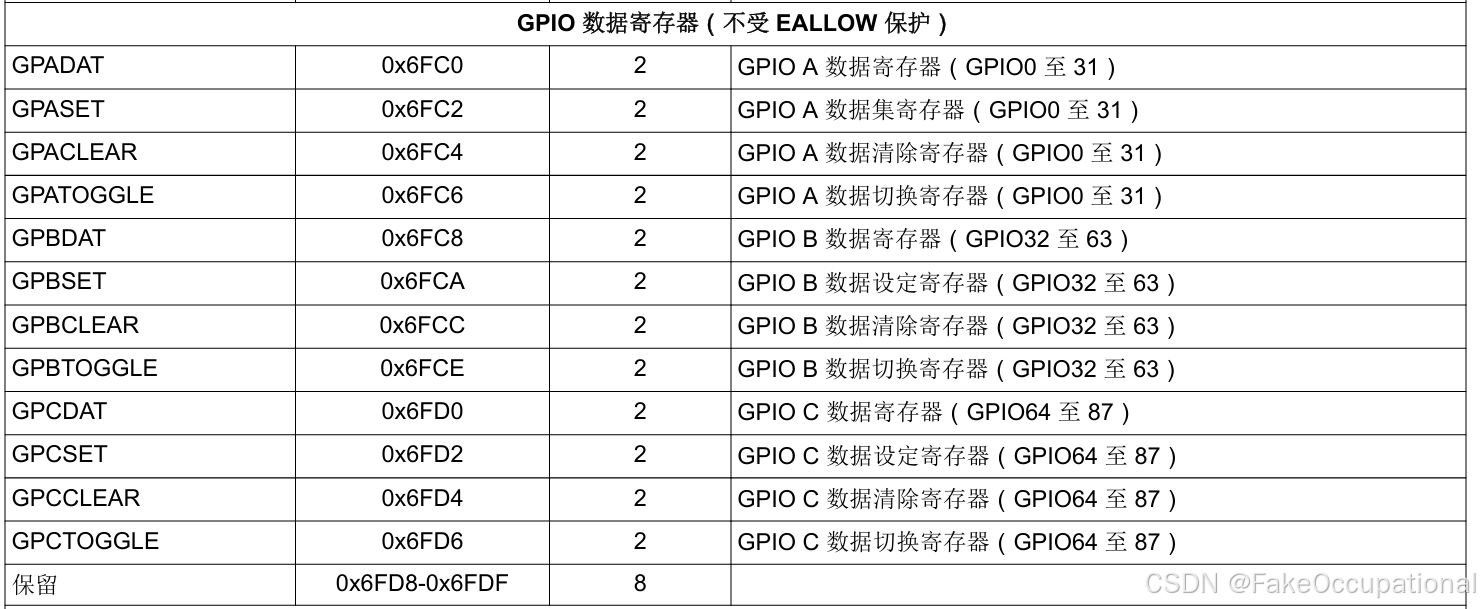

2. 数据寄存器(Data Registers)

- 用于读取或写入外设的数据。对于GPIO来说,数据寄存器允许您设置或读取引脚的状态。

GpioDataRegs就是这样的一个数据寄存器集合。

// DSP2833x_Gpio.h

struct GPIO_DATA_REGS {

union GPADAT_REG GPADAT; // GPIO Data Register (GPIO0 to 31)

union GPADAT_REG GPASET; // GPIO Data Set Register (GPIO0 to 31)

union GPADAT_REG GPACLEAR; // GPIO Data Clear Register (GPIO0 to 31)

union GPADAT_REG GPATOGGLE; // GPIO Data Toggle Register (GPIO0 to 31)

union GPBDAT_REG GPBDAT; // GPIO Data Register (GPIO32 to 63)

union GPBDAT_REG GPBSET; // GPIO Data Set Register (GPIO32 to 63)

union GPBDAT_REG GPBCLEAR; // GPIO Data Clear Register (GPIO32 to 63)

union GPBDAT_REG GPBTOGGLE; // GPIO Data Toggle Register (GPIO32 to 63)

union GPCDAT_REG GPCDAT; // GPIO Data Register (GPIO64 to 95)

union GPCDAT_REG GPCSET; // GPIO Data Set Register (GPIO64 to 95)

union GPCDAT_REG GPCCLEAR; // GPIO Data Clear Register (GPIO64 to 95)

union GPCDAT_REG GPCTOGGLE; // GPIO Data Toggle Register (GPIO64 to 95)

Uint16 rsvd1[8];

};

union GPADAT_REG {

Uint32 all;

struct GPADAT_BITS bit;

};

//----------------------------------------------------

// GPIO A DIR/TOGGLE/SET/CLEAR register bit definitions */

struct GPADAT_BITS { // bits description

Uint16 GPIO0:1; // 0 GPIO0

Uint16 GPIO1:1; // 1 GPIO1

Uint16 GPIO2:1; // 2 GPIO2

Uint16 GPIO3:1; // 3 GPIO3

Uint16 GPIO4:1; // 4 GPIO4

Uint16 GPIO5:1; // 5 GPIO5

Uint16 GPIO6:1; // 6 GPIO6

Uint16 GPIO7:1; // 7 GPIO7

Uint16 GPIO8:1; // 8 GPIO8

Uint16 GPIO9:1; // 9 GPIO9

Uint16 GPIO10:1; // 10 GPIO10

Uint16 GPIO11:1; // 11 GPIO11

Uint16 GPIO12:1; // 12 GPIO12

Uint16 GPIO13:1; // 13 GPIO13

Uint16 GPIO14:1; // 14 GPIO14

Uint16 GPIO15:1; // 15 GPIO15

Uint16 GPIO16:1; // 16 GPIO16

Uint16 GPIO17:1; // 17 GPIO17

Uint16 GPIO18:1; // 18 GPIO18

Uint16 GPIO19:1; // 19 GPIO19

Uint16 GPIO20:1; // 20 GPIO20

Uint16 GPIO21:1; // 21 GPIO21

Uint16 GPIO22:1; // 22 GPIO22

Uint16 GPIO23:1; // 23 GPIO23

Uint16 GPIO24:1; // 24 GPIO24

Uint16 GPIO25:1; // 25 GPIO25

Uint16 GPIO26:1; // 26 GPIO26

Uint16 GPIO27:1; // 27 GPIO27

Uint16 GPIO28:1; // 28 GPIO28

Uint16 GPIO29:1; // 29 GPIO29

Uint16 GPIO30:1; // 30 GPIO30

Uint16 GPIO31:1; // 31 GPIO31

};

- 示例:

GpioDataRegs.GPADAT.bit.GPIO0 = 1;// 设置GPIOA0为高电平unsigned int state = GpioDataRegs.GPADAT.bit.GPIO0;// 读取GPIOA0的状态

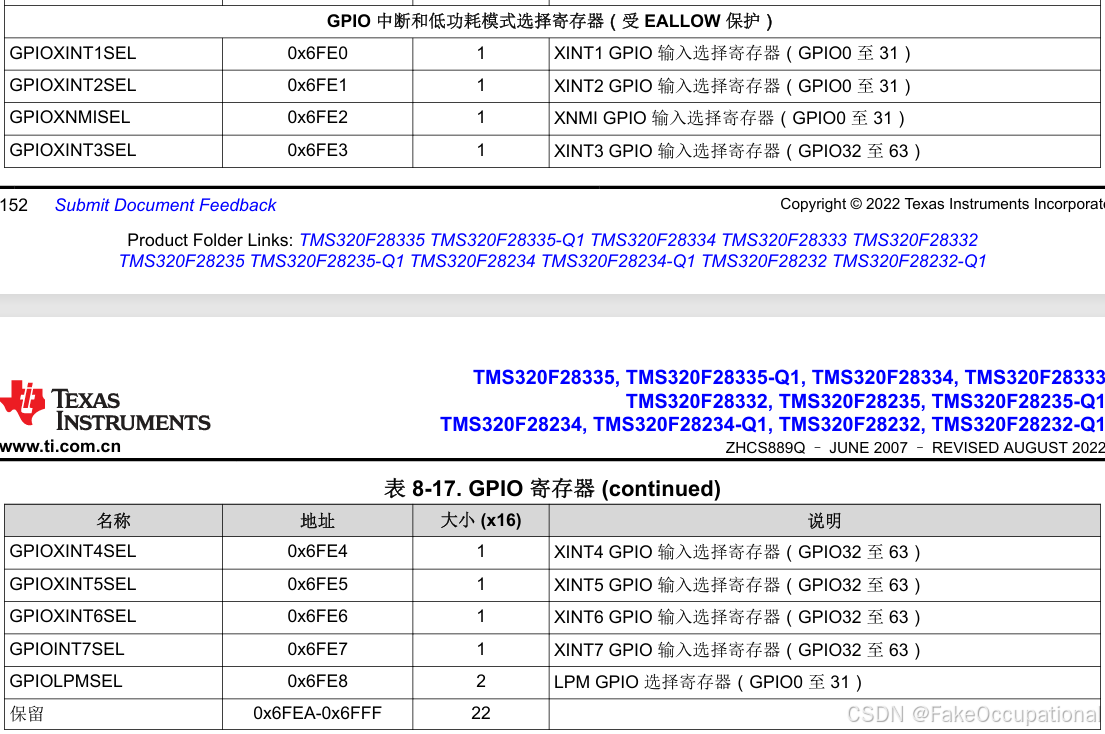

3. GPIO 中断(interrupt)和低功耗模式选择寄存器(受 EALLOW 保护)

中断

-

C2000系列微控制器支持多个外部中断(XINT)和非屏蔽中断(NMI),这些中断源可以配置为由不同的GPIO引脚触发。每个外部中断(如XINT1到XINT7)和非屏蔽中断(XNMI)都有相应的寄存器用于选择触发这些中断的GPIO引脚。

-

GPIOXINT1SEL 寄存器用于配置C2000系列微控制器中外部中断(XINT1)的来源(其他同理:XINT2、XINT3、XINT4、XINT5、XINT6、XINT7)。具体来说,这个寄存器允许您选择哪个GPIO引脚(从GPIO0到GPIO31)将作为外部中断1(XINT1)的触发源。

-

GPIOXNMISEL 配置可从GPIO0到GPIO31中选择引脚作为XNMI的触发源。

EALLOW;

// 确保GPIO15为普通GPIO功能

GpioCtrlRegs.GPAMUX1.bit.GPIO15 = 0;

// 配置GPIO15为输入模式

GpioCtrlRegs.GPADIR.bit.GPIO15 = 0;

// 使能上拉电阻(如果需要)

GpioCtrlRegs.GPAPUD.bit.GPIO15 = 0;

// 选择GPIO15作为XINT1的触发源

GpioCtrlRegs.GPIOXINT1SEL = 15;

// 配置XINT1为上升沿触发(假设使用PIE中断控制器)

PieCtrlRegs.XINT1CR.bit.POLARITY = 1; // 设置为上升沿触发

EDIS;

低功耗模式

- GPIOLPMSEL 寄存器用于配置C2000系列微控制器中低功耗模式(Low Power Mode, LPM)下的GPIO引脚行为。具体来说,这个寄存器允许您选择哪些GPIO引脚在进入低功耗模式时保持活动状态,从而可以在低功耗状态下继续响应外部事件或维持某些功能。

EALLOW;

// 设置GPIO15在低功耗模式下保持活动

GpioCtrlRegs.GPAMUX1.bit.GPIO15 = 0; // 确保GPIO15为普通GPIO功能

GpioCtrlRegs.GPADIR.bit.GPIO15 = 0; // 配置GPIO15为输入模式(如果需要)

GpioCtrlRegs.GPAPUD.bit.GPIO15 = 0; // 使能上拉电阻(如果需要)

GpioCtrlRegs.GPIOLPMSEL.bit.GPIO15 = 1; // GPIO15保持活动

// 其他引脚默认为0,即不保持活动

EDIS;

2108

2108

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?