名称:基于FPGA的数字锁控制电路VHDL代码Quartus仿真(文末获取)

软件:Quartus

语言:VHDL

代码功能:

任务及要求

硬件描述语言VHDL是一种用形式化方法描述数字电路和系统的语言。利用这种语

,数字电路系统的设计可以从上层到下层(从抽象到具体)逐层描述自己的设计思

想,用一系列分层次的模块来表示复杂的数字系统。然后,利用电子设计自动化(ED

A)工具,逐层进行仿真验证。设计一个用于数字锁的控制电路,功能要求如下

1.开锁代码为二位十进制数(BCD码表示),当输入代码的位数和位值与锁内给定

的密码一致,且按规定程序开锁时,方可开锁,并点亮开锁指示灯(用输出高电平表示)。否则,系统进入“错误”状态,发出报警信号。

2.开锁程序由设计者确定,并要求锁内给定的密码是可调的。

3.报警方式是点亮指示灯(输出高电平),直到输入复位信号,报警才停止。

1. 工程文件

2. 程序文件

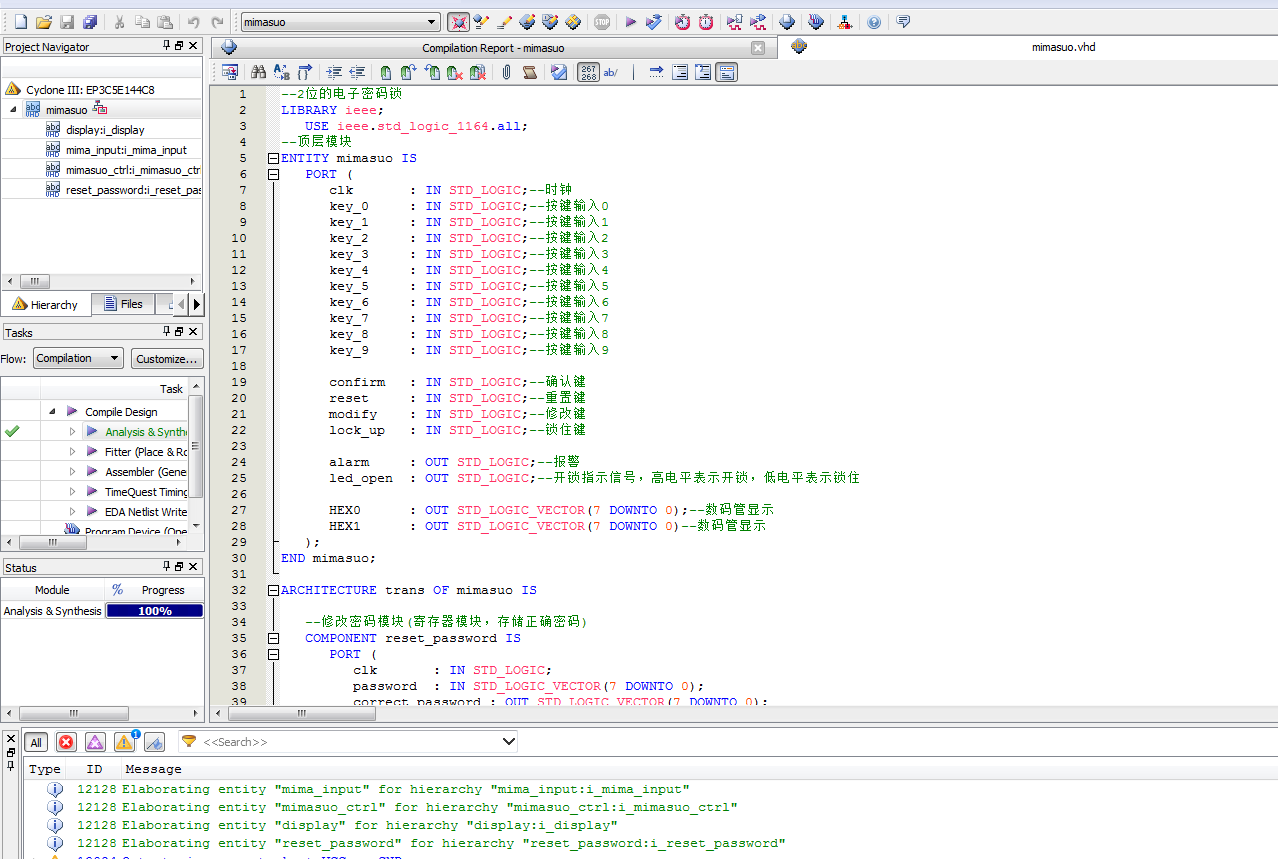

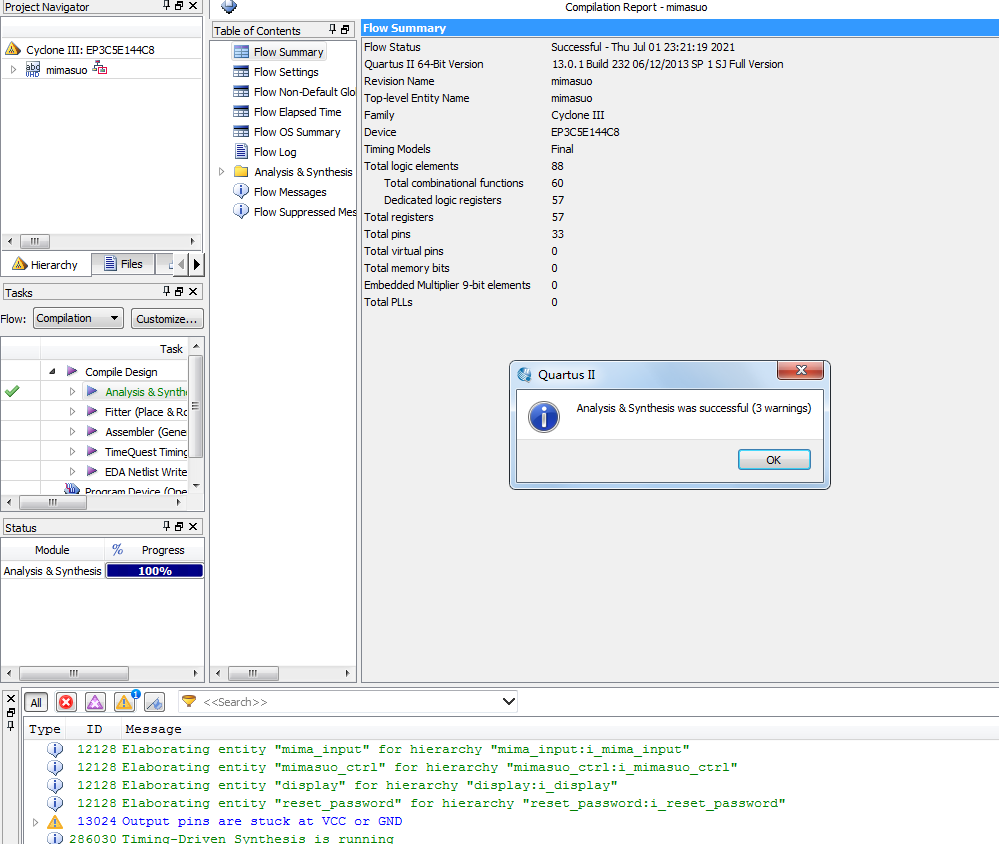

3. 程序编译

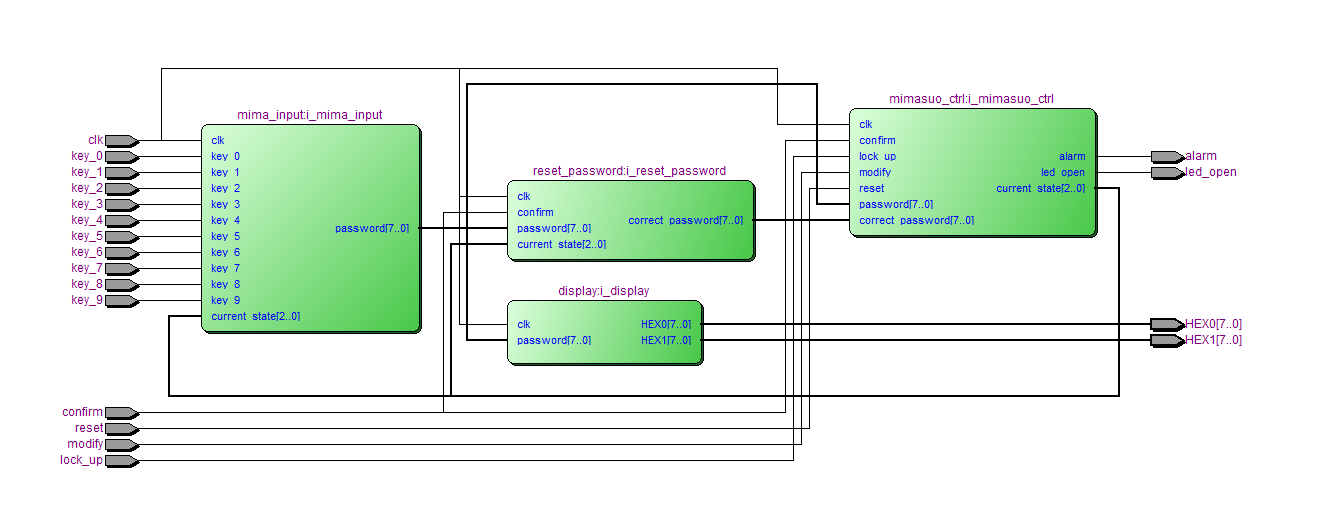

4. RTL图

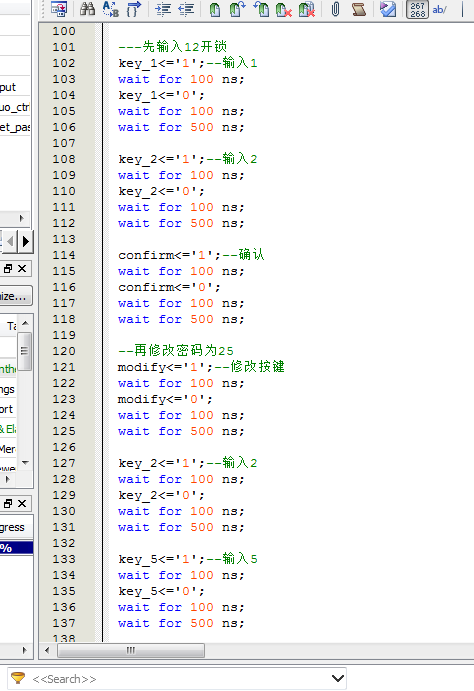

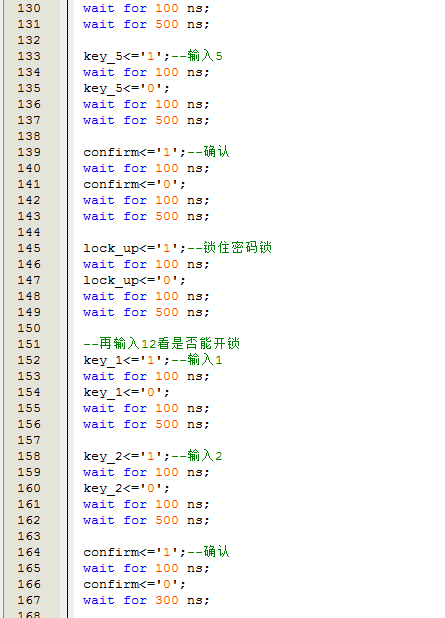

5. Testbench

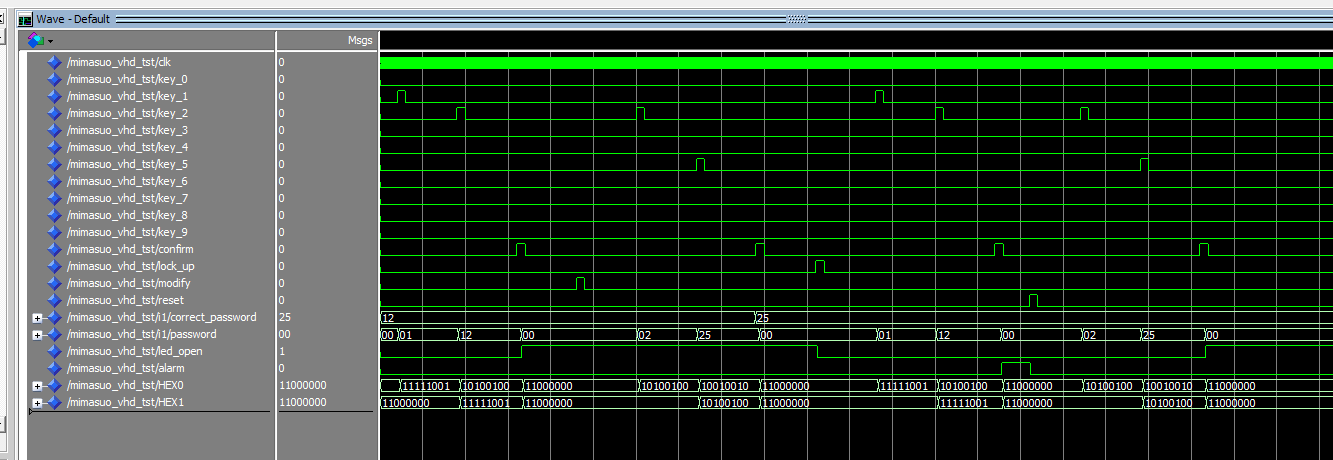

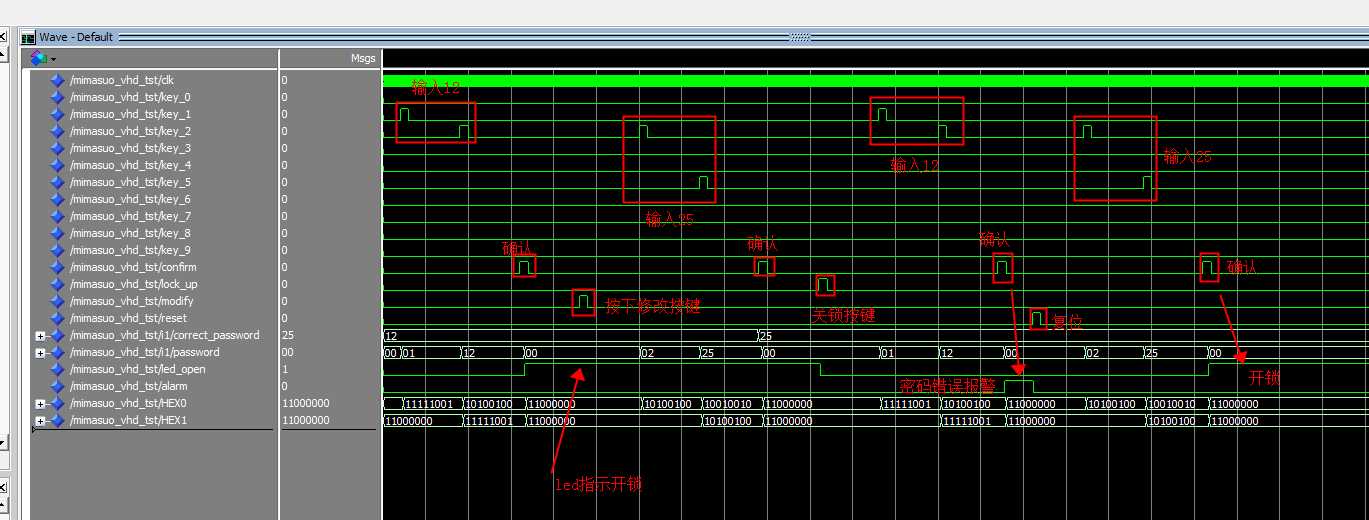

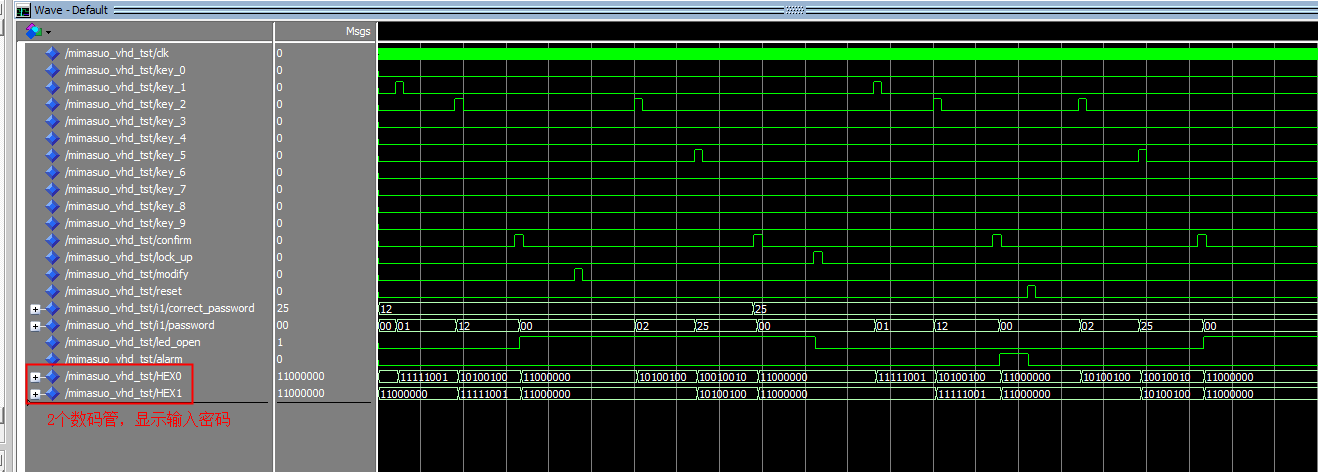

6. 仿真图

仿真图为:先输入初始密码12,开锁,开锁指示灯亮。按下修改密码按键,输入25,确认后将密码修改为25。再输入12,此时无法开锁,密码错误,报警。按下报警复位按键,清除报警。再输入25,确认,开锁,开锁指示灯亮。

部分代码展示:

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

470

470

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?