名称:电子密码锁设计Verilog代码Quartus仿真(文末获取)

软件:Quartus

语言:Verilog

代码功能:

I、题目:电子密码锁设计

II、课题任务

用VerilogHDL语言编写程序,设计一个电子密码锁控制电路,当输入正确代码时,输出开锁信号以推动执行机构工作。密码锁控制电路中存储一个可修改的6位代码,当输入的代码等于存储的代码时,开锁。从第一位代码输入后5秒内未将锁打开,则电路自动复位并进入自锁状态,使之无法再打开,并发出持续20秒的报警信号。允许有三次输错的机会,三次输入错误,电路自动复位并进入自锁状态,无法再打开。

III、具体设计内容:

1、设计任务

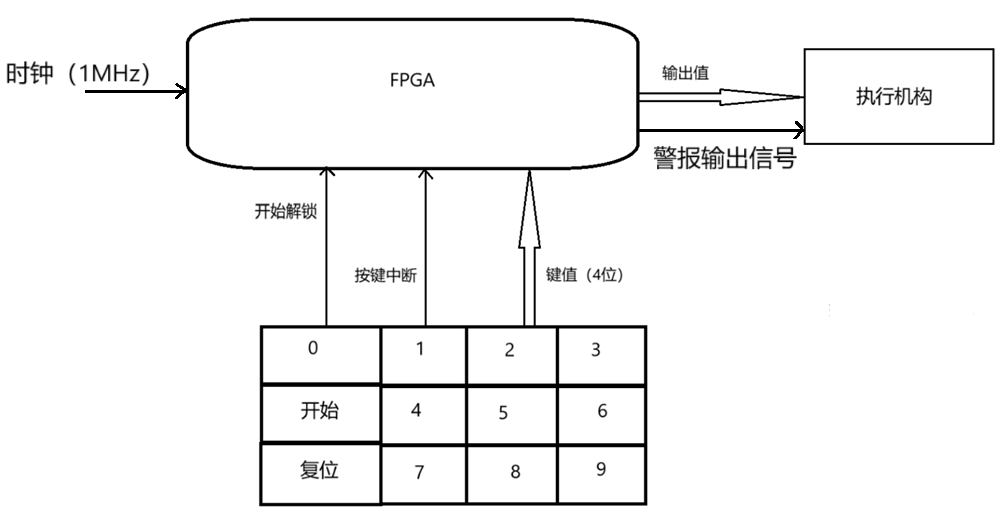

密码锁整体结构如图1所示,其中FPGA编程是本课程设计任务,通过按键产生控制信号输入给FPGA芯片,FPGA对按键信号进行处理,并输出信号给执行机构对密码锁进行操作。FPGA的输入时钟频率为1MHz。

图1 密码锁整体系统

开始开锁信号为外部输入信号,当该信号为高电平时,开始输入密码,密码为按键形式,每次按键会先发送一个高脉冲信号,即按键中断信号,然后将该按键对应的数字送出,具体时序如图2所示,FPGA接收到开始开锁信号后开始检测按键中断信号,如果按键中断有上跳沿跳变,便读取4位键值数据,然后与存储的代码匹配,如果匹配成功则输出4位二进制数0001,如果匹配不成功,需要重新输入,则输出二进制数0010,如果要复位自锁输出0011,同时将警报输出信号置高电平,高电平持续20秒时间再置成低电平,不

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

7924

7924

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?