这是一个比较玄学的问题,末尾写了比较玄学的解决方法…

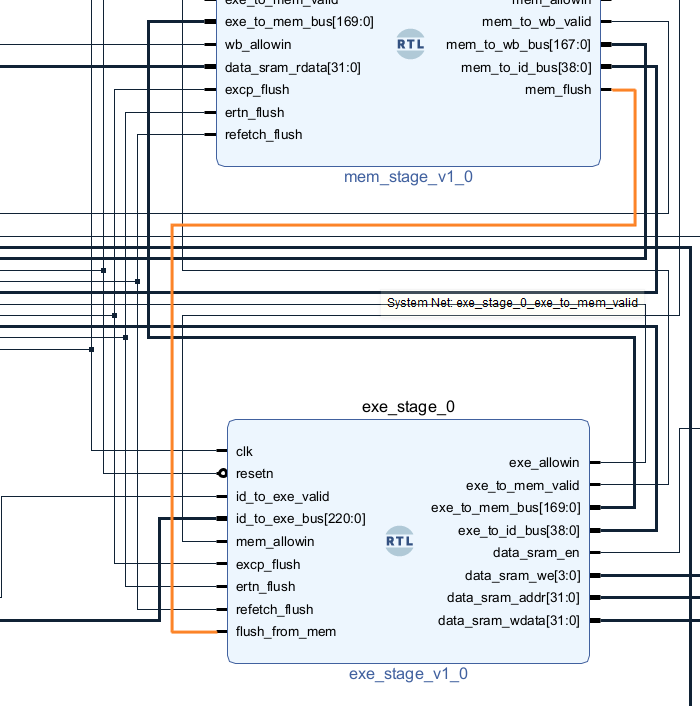

起先,博主两个模块中在中新添加了一对端口,并在顶层的block_design文件中正常将二者连接:

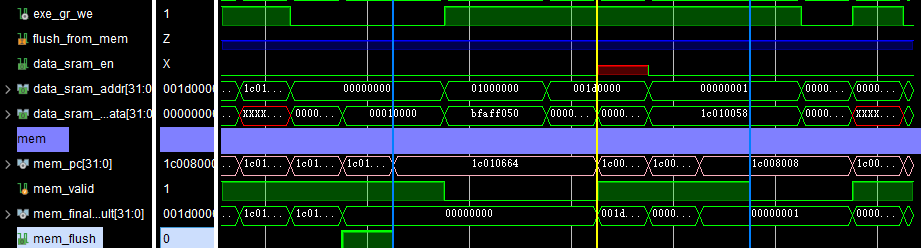

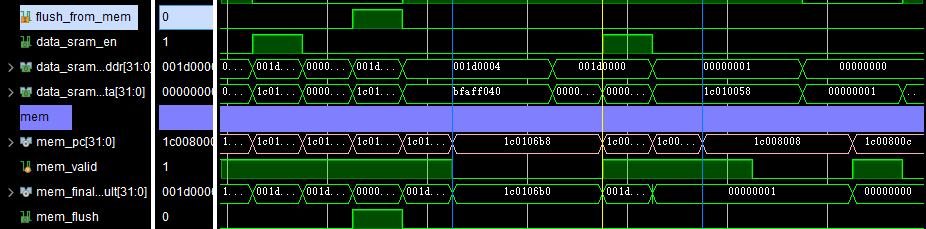

但是,在仿真时发现,位于mem_stage的输出端口mem_flush正常输出,但位于exe_stage的flush_from_mem端口始终为ZZZ的高阻态

在检查过顶层block_design生成的代码,确认无误后,博主做出了以下尝试:(未果)

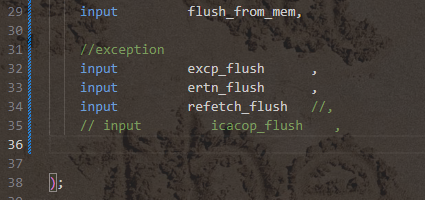

最终,解决的办法是:将出现ZZZ的新增的端口声明的位置由原本的最后一个,向前提前了一些,如下图:

调整前:

调整后:

就解决了…

3588

3588

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?