时序收敛(一)

前言

第1章 时序收敛

1.1 时序收敛的标准

1.1.1 检查约束

时序收敛 ≠ 只要 WNS≥0,前提是约束必须“完整 + 合理”。

发现违例时,第一步永远先“验约束”,再“查原因”。

| 检查维度 | 推荐 Tcl / 操作 | 关键输出/解读 | 备注 |

|---|---|---|---|

| 1. 约束完整性 | check_timing -name myCheck | 报告分三列: ① TimingCheck(条目) ② Count(次数) ③ WorstSeverity(严重度) | 必查条目: • no_clock • loops / latch_loops • constant_clock |

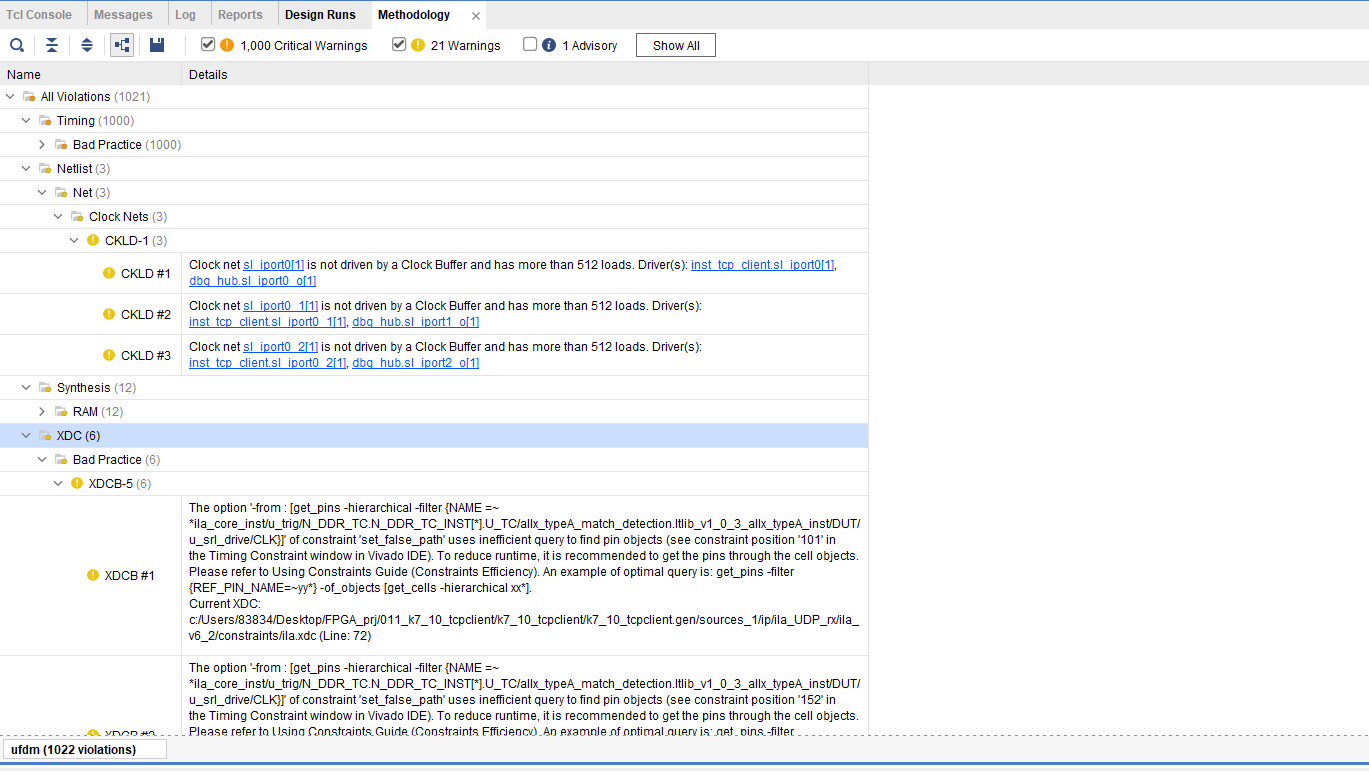

| 2. 约束规范性 | report_methodology -name myUfdm | UFDM 报告 TIMING/XDC 条目 | 重点看 BadPractice |

| 3. 例外约束有效性 | report_exceptions -name myExcept | 列出 false_path / mcp / max_delay 是否生效、被覆盖 | 优先级冲突一目了然 |

| 4. 时钟网络遗漏 | report_clock_networks -name myClkNet | 未约束时钟会显示“Unconstrained” | 可在综合后、实现后反复执行 |

| 5. 建立/保持裕量 | report_timing_summary | WNS/TNS、WHS/THS、WPWS/TPWS | 收敛标准: • WNS ≥ 0 且 TNS = 0 • WHS ≥ 0 且 THS = 0 • WPWS ≥ 0 且 TPWS = 0 |

得到的 UFDM(UltraFast Design Methodology)报告,本质上是一份 “设计合规体检表”。它把 FPGA 工程里所有潜在的设计陋习、约束陋习、器件滥用、工具误用全部扫出来,并按 Severity 分级:

- Critical(必须改,不改可能烧片)

- Warning(强烈建议改,不改大概率时序/功能/可靠性翻车)

- Bad Practice(官方吐槽:虽然综合实现能跑,但代码/约束写得丑、隐患大、移植性差、维护难,属于“能跑却丢脸”系列)

补充:若建立时间需求 < 1 ns(等效 >1 GHz),先确认约束是否写错,再谈收敛。

- loops = 纯组合逻辑自己绕成圈 → 震荡 + 无法算延迟。

- latch_loops = 锁存器 + 组合逻辑绕成圈 → 透明时震荡、锁存时未知。

- 两者都必须打断(插寄存器或改代码),否则功能与时序双失控。

知识点补充(实战 Tips)

-

“先验再查”流程

违例路径 → 双击打开时序报告 → 先看Requirement列是否合理 → 若离谱,先改约束,再动代码。 -

时钟遗漏速查

综合后 DCP →report_clock_networks→ 凡出现 “(0.00 MHz)” 即为无约束时钟 → 立即create_clock/create_generated_clock。 -

例外冲突快速定位

report_exceptions→ 看 Ignored 列 >0 → 用write_xdc -constraints invalid导出被覆盖约束 → 逐条核对优先级。 -

约束优先级口诀

“组 > 假 > 大/小 > 多”

set_clock_groups>set_false_path>set_max/min_delay>set_multicycle_path

同类型约束:越具体(含-through/-pin)优先级越高。 -

裕量“警戒线”

时钟频率 建立 WNS 红线 保持 WHS 红线 ClockSkew 红线 ≥300 MHz –0.5 ns –0.4 ns 500 ps <300 MHz –1.0 ns –0.5 ns 1 ns -

脚本化检查模板

# 一键“体检”脚本 check_timing -name check_$proj report_methodology -name ufdm_$proj report_exceptions -name except_$proj report_clock_networks -name clknet_$proj report_timing_summary -name ts_$proj -

版本差异

• 2018.1 及之前:需手动place_design -fanout_opt降扇出;

• 2018.2 之后:默认自动扇出优化,可用-no_fanout_opt关闭。 -

常见“假违例”场景

• 跨时钟域未设set_clock_groups -async→ 工具按同步 1 周期检查 → 虚报 Setup –5 ns。

• I/O 只写set_input_delay未写set_output_delay→check_timing报 “no_output_delay”。

• 同一端口重复create_clock未加-add→ 后者覆盖前者,导致时钟消失。

牢记:约束错,一切白搭;约束对,再谈 QoR。

时序收敛与约束检查

时序收敛与约束检查

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?