=========================================================================

一、前置简单的知识

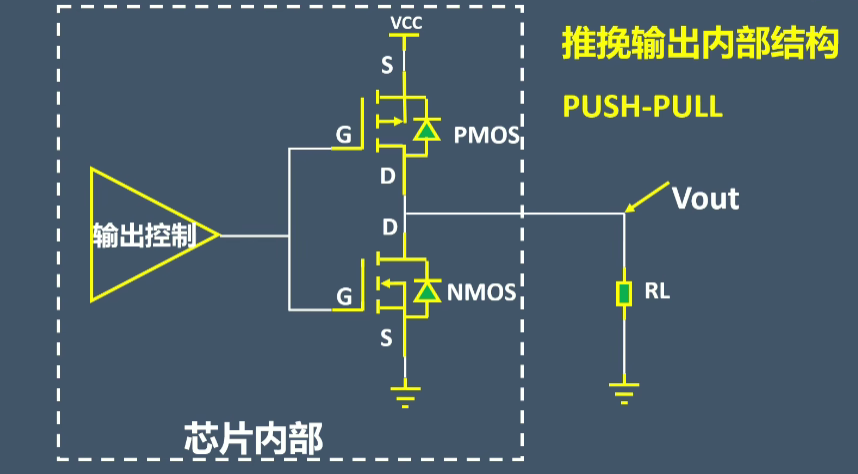

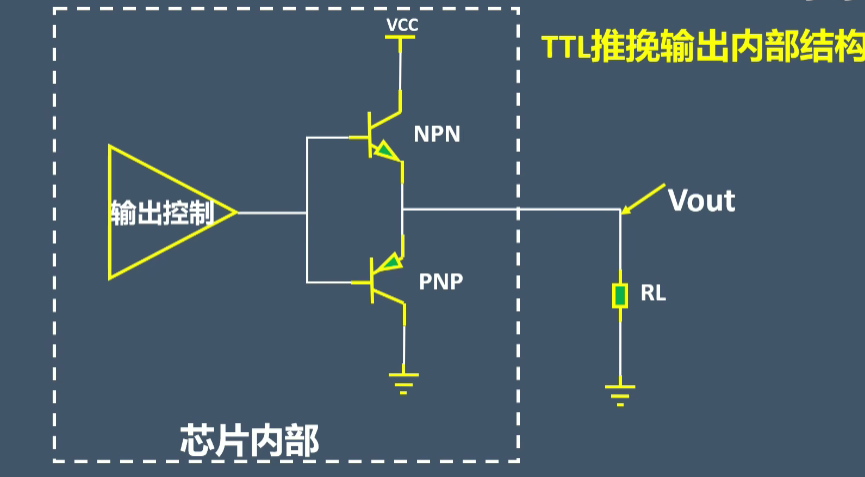

二、推挽输出

1.组成:

N-MOS、P-MOS

2.驱动性:

高低电平都具有驱动能力

3.原理/工作流程

①输出高电平:

单片机通过寄存器控制 P 型 MOS 管导通,N 型 MOS 管截止。

此时,输出引脚直接连接到电源 VCC(如 3.3V 或 5V),形成强上拉,输出高电平。

②输出低电平:

单片机控制 N 型 MOS 管导通,P 型 MOS 管截止。

输出引脚接地(GND),形成强下拉,输出低电平。

4.推挽电路图

5.特性

①双向驱动能力:

既能向负载提供电流(拉电流),也能从负载吸收电流(灌电流),驱动能力强(典型值 20mA),适合直接驱动 LED、继电器等设备。这是推挽电路主动完成的两个功能。

②快速切换:

上下管交替工作,信号上升沿和下降沿均由有源器件驱动,速度快,适用于高速信号传输(如 SPI)。

6.单片机控制

①配置输出模式:

通过寄存器设置 GPIO 为推挽输出模式。例如,

STM32 中使用GPIO_InitStruct.Mode = GPIO_MODE_OUTPUT_PP;

(51单片机好像没遇到过需要配置IO口模式,不了解)

②输出电平控制:

直接操作输出数据寄存器(如 STM32 的 GPIOx_ODR)或位设置 / 清除寄存器(GPIOx_BSRR)。

| IO 口电平 | PMOS 状态 | NMOS 状态 | 输出结果 |

|---|---|---|---|

| 高电平 | 导通 | 截止 | 输出≈VDD(推) |

| 低电平 | 截止 | 导通 | 输出≈GND(拉) |

=========================================================================

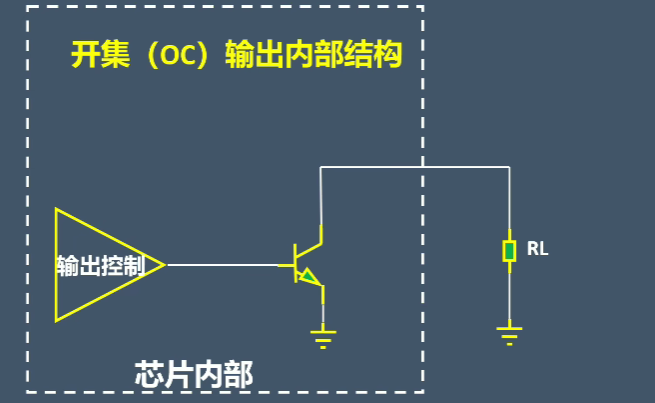

三、开漏输出

1.组成:

N-MOS

2.驱动性:

仅低电平具有驱动能力。高电平不具备驱动能力。

3.原理/工作流程

①说明:

开漏输出仅包含一个 N 型 MOS 管,无法主动输出高电平,需依赖外部上拉电阻实现输出高电平。

②输出低电平:

单片机控制 N 型 MOS 管导通,输出引脚接地,形成低电平。

③输出高电平:

单片机控制 N 型 MOS 管截止,输出引脚处于高阻态,此时需外部上拉电阻将引脚电压拉高至目标电平(如 VCC_EXT)。

4.开漏电路图

5.特性

推挽输出不具备下述性能。

①线与功能:

多个开漏输出引脚并联时,任一引脚输出低电平会将总线拉低,仅当所有引脚均为高阻态时,总线才被上拉电阻拉高。这一特性支持多设备共享总线(如 I²C、1-Wire)。

②电平兼容性:

通过外接不同电压的上拉电阻(如 5V),可实现跨电压域通信(如 3.3V 单片机驱动 5V 外设),也就是3.3V的开漏输出,只要开漏输出引脚处上拉一个5V电阻,就可以用3.3V驱动5V的模块。

6.单片机控制

①配置输出模式:

设置 GPIO 为开漏输出模式。例如,

STM32 中使用GPIO_InitStruct.Mode = GPIO_MODE_AF_OD,并需使能内部或外部上拉电阻;

(51单片机好像没遇到过需要配置IO口模式,不了解)

②输出电平控制:

写入0时 N 型 MOS 管导通,输出低电平;

写入1时 N 型 MOS 管截止,引脚呈高阻态,需外部上拉电阻实现高电平。

7.开漏输出外部电路要求:必须外接上拉电阻!!!

阻值通常为 1kΩ~10kΩ,需根据负载电流和信号速度选择。阻值过小可能导致 MOS 管过载,阻值过大则会降低驱动能力并延长信号上升时间。

=========================================================================

四、总结

| 对比维度 | 开漏输出(Open-Drain) | 推挽输出(Push-Pull) |

|---|---|---|

| 输出级结构 | 仅含 1 个 NMOS 管(下拉管),PMOS 管永久禁用 | 含 PMOS(上拉管)+ NMOS(下拉管),两者互补工作 |

| 上拉电阻需求 | 必须外接(否则高电平时输出浮空,无法稳定) | 无需外接(PMOS 直接驱动高电平) |

| 高电平驱动 | 依赖外部上拉电阻(如接 VDD),属于 “被动拉高” | PMOS 主动导通,直接将输出拉至 VDD,属于 “主动推高” |

| 驱动能力 | 仅支持灌电流(低电平时),高电平驱动能力由上拉电阻决定(电阻越大,能力越弱) | 支持拉电流(高电平,PMOS 提供)+ 灌电流(低电平,NMOS 提供),双向驱动能力强 |

| 电平灵活性 | 可通过外接不同电压的上拉电阻实现电平转换(如 3.3V IO 口接 5V 上拉,输出 5V 高电平) | 高电平固定为 IO 口的电源电压(如 VDD=3.3V,高电平≈3.3V),无法灵活转换 |

| 线与功能 | 支持(多设备输出端并联,只要一个输出低电平,总线即为低电平,需共上拉) | 不支持(多设备输出端并联可能导致电源短路,如 A 设备 PMOS 导通输出高,B 设备 NMOS 导通输出低) |

| 信号速度 | 慢(高电平上升时间由上拉电阻和负载电容决定,电阻越大、电容越大,速度越慢) | 快(无外部电阻,上升 / 下降时间仅由晶体管开关速度决定,适合高频信号) |

| 静态功耗 | 高电平时仅上拉电阻有静态电流(电流小),低电平时 NMOS 导通电流集中在负载 | 高 / 低电平时均有一个晶体管导通,静态功耗略高于开漏(但动态功耗更低) |

1. 开漏输出:灵活适配多设备协同

- 核心特性:依赖上拉、支持线与、电平可转换。

- 典型应用:

- 多设备共享总线(如 I²C、SMBus):利用线与特性实现 “一主多从” 通信,避免信号冲突。

- 电平转换场景(如 3.3V MCU 驱动 5V 传感器):通过外接 5V 上拉电阻,使 3.3V IO 口输出 5V 高电平。

- 漏极开路门电路(如 OC 门):需多门并联控制同一负载时,避免电源短路。

2. 推挽输出:高效驱动高速 / 大负载

- 核心特性:无需外接元件、双向强驱动、高速响应。

- 典型应用:

- 高速同步通信(如 SPI、USB、UART):快速的上升 / 下降时间满足高频信号传输需求(如 SPI 时钟可达几十 MHz)。

- 直接驱动负载(如 LED、继电器、电机):拉 / 灌电流能力强,可直接为负载提供足够电流(如 STM32 推挽输出灌电流可达 20mA)。

- 单端信号输出(如 GPIO 控制开关):无需复杂外围电路,简化硬件设计。

=========================================================================

五、进阶理解MOS管(暂无)

除非你熟练了开漏输出和推挽输出的工作原理,以及对深层原理感兴趣,不然不推荐看。

(连接待更新)

=========================================================================

1601

1601

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?