1.源码来源vivado xilinx官方实例

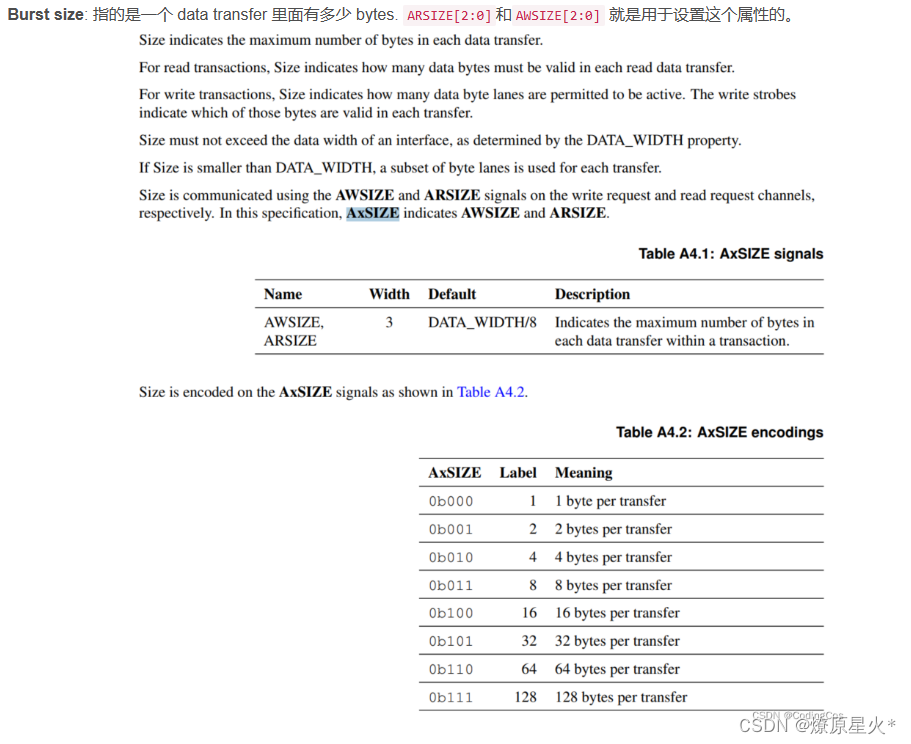

2.[2:0]M_AXI_ARSIZE:指的是一个 data transfer 里面有多少 Bytes——这里我抓出来是4B(即010)——2^2=4B代表你想往axi总线的搬移数据的位宽(32bit)。

3.

Burst length: ARLEN[7:0]和AWLEN[7:0] 突发传输长度是指在一次突发传输中所进行的传输(data transfer)次数,在传输完初始地址后,进行的数据传输次数就是突发传输长度。在 AXI4 中:

- INCR 类型最大支持长度为 256=FF(1111 1111)+1;——根据实际一次突发的地址偏移量(即数据量来计算)计算公式如下:——burst_size_bytes=(Burst length+1)*往axi总线的搬移数据的位宽 ——eg:一次突发是64B=4(SIZE)*16(act_len)——但表示是(0000_1111)即是15.

4.

burst_size_bytes:一次突发的数据量大小(即数据量的偏移地址)eg:4kB,512B,64B(可以通过地址偏移量抓出来看)=C_M_AXI_BURST_LEN(一般取16,32,64,128)*C_M_AXI_DATA_WIDTH/8计算得出

5.

C_M_TARGET_SLAVE_BASE_ADD:——表示突发地址的基地址:eg:0X90000000,AXI协议会自动根据计算得出每一次突发的axi地址偏移量。

mig和XDMA都是full接口。lite接口(专门用于xilinx官方的代码用于软核访问寄存器的)只能和软核的M_AXI_DP的AXI Interconnect相连接

8.axi总线的数据一般通过fifo缓存后给axi突发使用

8.w_flag(状态机的触发起始信号)一般通过当fifo读的数据个数*位宽大于设定的一次突发的数据量时就拉高w_flag信号

9.软核通过正点原子实现代码实现dma的传输。

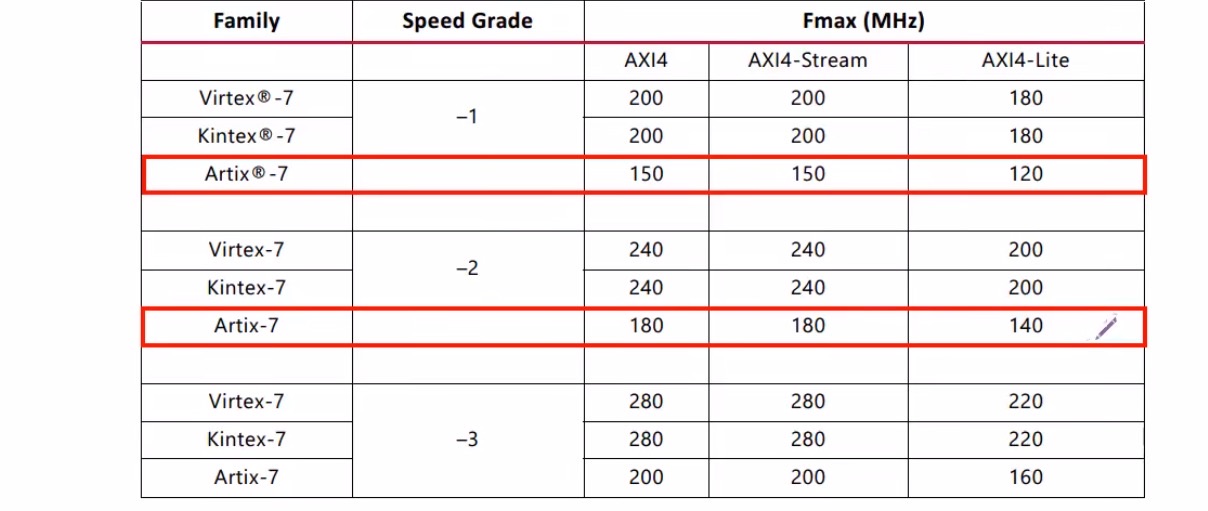

10:各款fpga所支持的axi接口的时钟频率

11: axi_full与axi_stream互相转换需要用到axidatamover ip

本文详细解释了VivadoXilinx中AXI总线的数据传输特性,包括M_AXI_ARSIZE的字节数量、Burstlength的突发传输长度、burst_size_bytes的突发数据量、C_M_TARGET_SLAVE_BASE_ADD的基地址以及MIG和XDMA接口的区别。此外,还介绍了FIFO在AXI突发传输中的作用和w_flag状态信号的触发机制。

本文详细解释了VivadoXilinx中AXI总线的数据传输特性,包括M_AXI_ARSIZE的字节数量、Burstlength的突发传输长度、burst_size_bytes的突发数据量、C_M_TARGET_SLAVE_BASE_ADD的基地址以及MIG和XDMA接口的区别。此外,还介绍了FIFO在AXI突发传输中的作用和w_flag状态信号的触发机制。

1492

1492

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?