FPGA高级设计(一):速度结构设计

最新推荐文章于 2024-12-09 14:07:48 发布

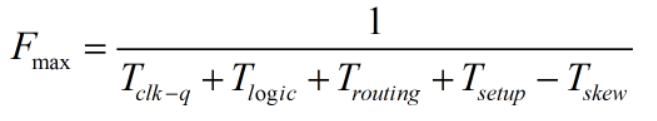

本文探讨了在高速结构设计中如何平衡流量与时滞。通过增加流水线结构可以提升处理数据的速度,但可能增加时滞;而减少时滞则可能需要去除流水线寄存器。满足时序设计的关键包括采用并行结构、添加寄存器层次、展平逻辑结构和寄存器平衡等策略。这些方法旨在确保关键路径的延时小于时钟周期,从而实现高效运算。

本文探讨了在高速结构设计中如何平衡流量与时滞。通过增加流水线结构可以提升处理数据的速度,但可能增加时滞;而减少时滞则可能需要去除流水线寄存器。满足时序设计的关键包括采用并行结构、添加寄存器层次、展平逻辑结构和寄存器平衡等策略。这些方法旨在确保关键路径的延时小于时钟周期,从而实现高效运算。

2683

2683

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?