一、计算/设计过程

说明:本实验是验证性实验,计算预测验证结果。是设计性实验一定要从系统指标计算出元件参数过程,越详细越好。用公式输入法完成相关公式内容,不得贴手写图片。(注意:从抽象公式直接得出结果,不得分,页数可根据内容调整)

1、1位半加器

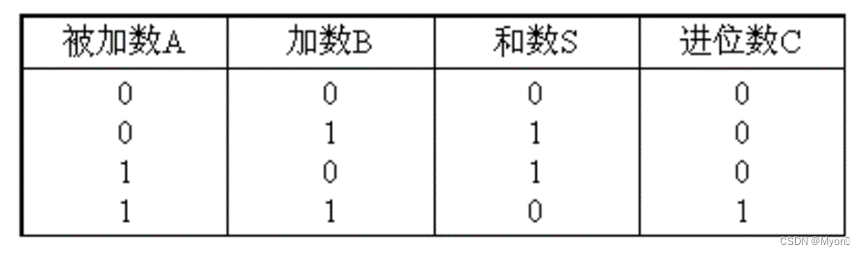

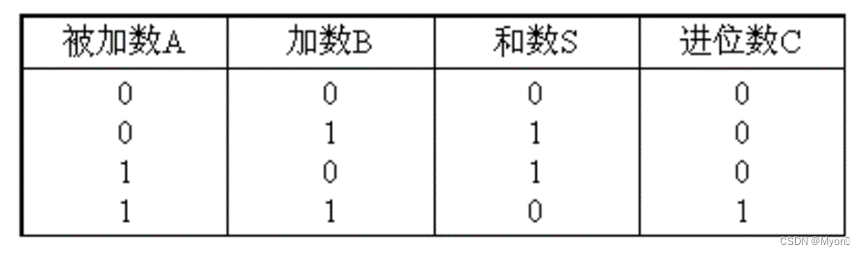

真值表:

逻辑方程:

S=`AB+A`B

C=AB

2、1位全加器

这篇预习报告详细介绍了西南科技大学数字电子技术实验的内容,包括1位半加器、1位全加器、三变量多数表决器、1位二进制数比较器和四变量多数表决器的设计。通过真值表和逻辑方程阐述了各组件的工作原理,并展示了使用FPGA进行逻辑电路实现的预实验准备,包括原理仿真和工程仿真的截图。

这篇预习报告详细介绍了西南科技大学数字电子技术实验的内容,包括1位半加器、1位全加器、三变量多数表决器、1位二进制数比较器和四变量多数表决器的设计。通过真值表和逻辑方程阐述了各组件的工作原理,并展示了使用FPGA进行逻辑电路实现的预实验准备,包括原理仿真和工程仿真的截图。

一、计算/设计过程

说明:本实验是验证性实验,计算预测验证结果。是设计性实验一定要从系统指标计算出元件参数过程,越详细越好。用公式输入法完成相关公式内容,不得贴手写图片。(注意:从抽象公式直接得出结果,不得分,页数可根据内容调整)

1、1位半加器

真值表:

逻辑方程:

S=`AB+A`B

C=AB

2、1位全加器

2494

2494

1万+

1万+

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?