题目描述

无向连通图 G 有 n 个点,n-1 条边。点从1到 n 依次编号,编号为 i 的点的权值为 W_i,每条边的长度均为 1。图上两点 (u, v) 的距离定义为 u 点到 v 点的最短距离。对于图 G 上的点对 (u, v),若它们的距离为 2,则它们之间会产生Wv ×Wu的联合权值。

请问图 G 上所有可产生联合权值的有序点对中,联合权值最大的是多少?所有联合权值之和是多少?

输入输出格式

输入格式:

第一行包含 1 个整数 n。

接下来 n-1 行,每行包含 2 个用空格隔开的正整数 u,v,表示编号为 u 和编号为 v 的点之间有边相连。

最后 1 行,包含 n 个正整数,每两个正整数之间用一个空格隔开,其中第 i 个整数表示图 G 上编号为 i 的点的权值为 W_i 。

输出格式:

输出共 1行,包含 2 个整数,之间用一个空格隔开,依次为图 G 上联合权值的最大值和所有联合权值之和。由于所有联合权值之和可能很大,输出它时要对10007取余。

输入输出样例

输入样例#1:

5

1 2

2 3

3 4

4 5

1 5 2 3 10

输出样例#1:

20 74

说明

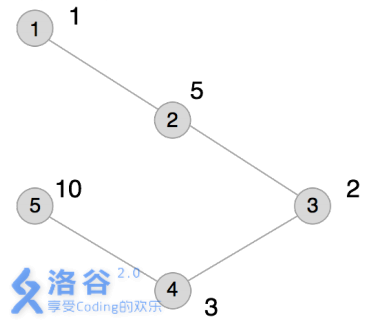

本例输入的图如上所示,距离为2 的有序点对有(1,3) 、( 2,4)、(3,1) 、 (3,5)、(4,2) (5,3)。

其联合权值分别为2 、15、2 、20、15、20。其中最大的是20,总和为74。

【数据说明】

对于30%的数据,1<n≤100;

对于60%的数据,1<n≤2000;

对于100%的数据,1<n≤200000,0<Wi ≤10000。

保证一定存在可产生联合权值的有序点对。

#include<bits/stdc++.h>

using namespace std;

const int maxn = 2e5 + 10;

const int mod = 10007;

vector<int>a[maxn];

long long b[maxn];

long long sum[maxn];

bool cmp(int x,int y)

{

return b[x] < b[y];

}

int main()

{

int n;

scanf("%d",&n);

for(int i = 1; i < n; i++)

{

int x,y;

scanf("%d%d",&x,&y);

a[x].push_back(y);

a[y].push_back(x);

}

for(int i = 1; i <= n; i++)scanf("%lld",&b[i]);

long long maxx = 0;

for(int i = 1; i <= n; i++)

{

for(int j = 0; j < a[i].size(); j++)sum[i] += b[a[i][j]];

sort(a[i].begin(),a[i].end(),cmp);

long long sum_1 = 1;

int x = a[i].size();

if(x >= 2)sum_1 = b[a[i][x - 1]] * b[a[i][x - 2]];

maxx = max(maxx,sum_1);

}

long long ans = 0;

for(int i = 1; i <= n; i++)

{

long long sum_1 = 0;

for(int j = 0; j < a[i].size(); j++)

{

int x = a[i][j];

sum_1 = (sum_1 + b[x] * (sum[i] - b[x])) % mod;

}

ans = (ans + sum_1) % mod;

}

printf("%lld %lld\n",maxx,ans);

return 0;

}

本文探讨了在一个无向连通图中计算有序点对之间的联合权值问题,包括求解最大联合权值及所有联合权值之和的方法。通过遍历图结构,利用排序和动态计算策略实现了高效的解决方案。

本文探讨了在一个无向连通图中计算有序点对之间的联合权值问题,包括求解最大联合权值及所有联合权值之和的方法。通过遍历图结构,利用排序和动态计算策略实现了高效的解决方案。

670

670

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?