无极缩放是指平滑的调整图像的尺寸,电脑或者手机中对图片进行放大或者缩小就是使用了无极缩放算法对图片进行处理。图像的无极缩放需要通过插值算法来实现,常见的插值算法有最近邻插值、双线性插值和双三次插值。最近邻插值实现起来最简单,但是会导致图像边缘处出现锯齿,双三次插值最复杂,插值之后的图像效果也是最好的。

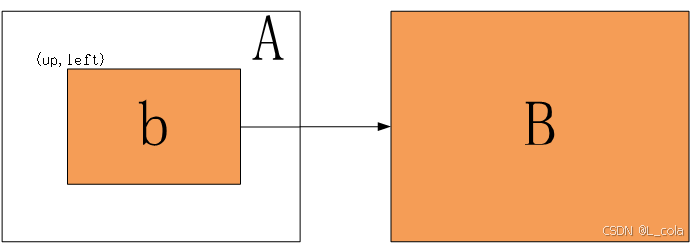

本文通过FPGA实现对图像A中心一块区域b进行放大,放大之后得到图像B,图像B的尺寸与原图像A大小一致。

下面首先介绍图像缩放的原理。

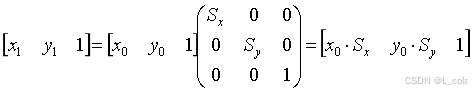

假设图像x轴方向的缩放比率为Sx,y轴方向的缩放比率为Sy,相应的变换表达式为:

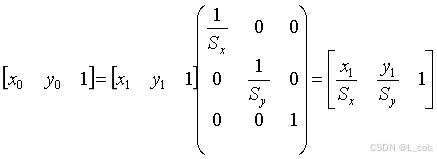

其逆运算如下:

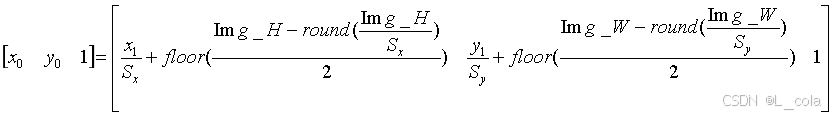

因此可以推出图像中心区域放大的计算公式为:

其中,Img_H为图像行数,Img_W为图像列数。

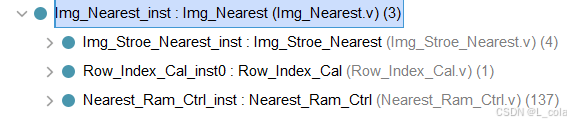

FPGA的优势在于可以对图像进行流水处理,从而实现对算法加速。程序一共分为3个模块,第一个模块根据计算公式首先完成每一行内插值像素的处理,第二个模块计算图像中心区域左上角起始坐标位置(up,left),第三个模块根据计算公式完成图像的缓存以及对应行图像的提取。

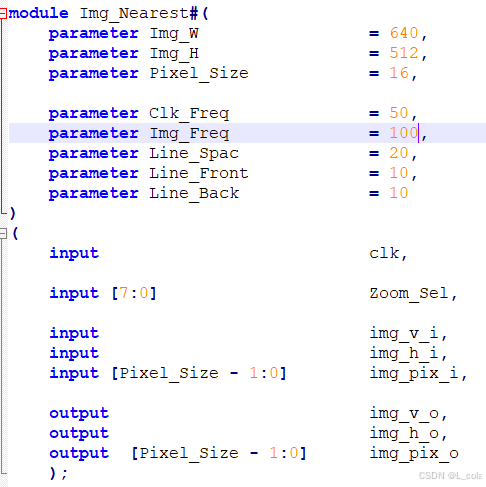

程序的接口如下图所示。

|

信号名 |

信号含义 |

|

Img_W |

图像宽 |

|

Img_H |

图像高 |

|

Pixel_Size |

像素位宽 |

|

Clk_Freq |

像素时钟频率 |

|

Img_Freq |

图像帧频 |

|

Line_Spac |

行消隐 |

|

Line_Front |

行前肩 |

|

Line_Back |

行后肩 |

|

clk |

像素时钟 |

|

Zoom_Sel |

放大倍数,支持1.1~32倍无极放大,1.1倍放大对应Zoom_Sel为11,以此类推 |

|

img_v_i |

输入图像场同步信号 |

|

img_h_i |

输入图像行有效信号 |

|

img_pix_i |

输入图像数据 |

|

img_v_o |

输出图像场同步信号 |

|

img_h_o |

输出图像行同步信号 |

|

img_pix_o |

输出图像数据 |

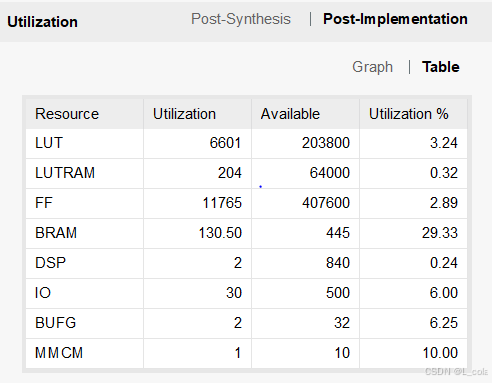

对于大小为640×512的图像,在K7-325T中资源消耗情况如下所示。

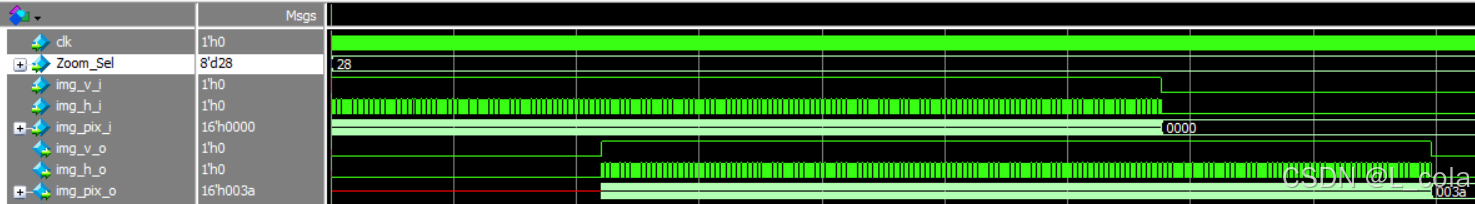

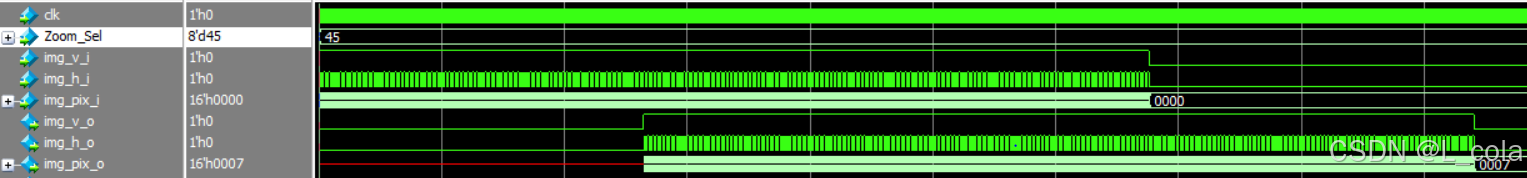

放大2.8倍的FPGA仿真时序图如下图所示。

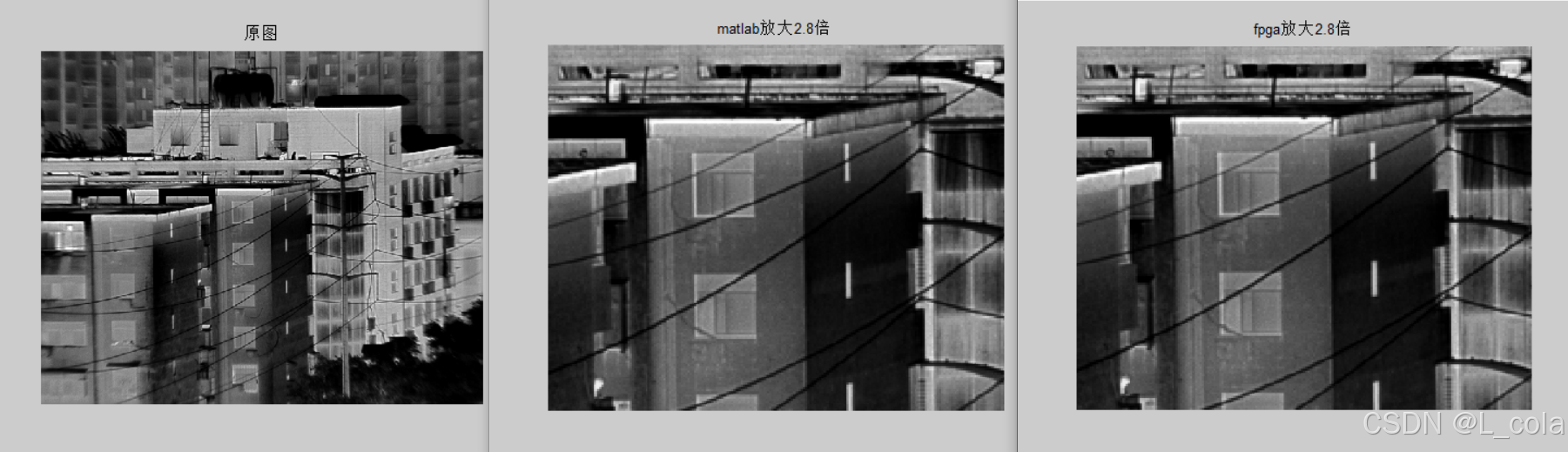

下图是放大2.8倍,原图、matlab放大效果图以及fpga放大效果图对比如下所示。

放大4.5倍的FPGA仿真时序图如下图所示。放大倍数越大,处理完的图像输出延时越大,但是均能保证当帧实时处理。

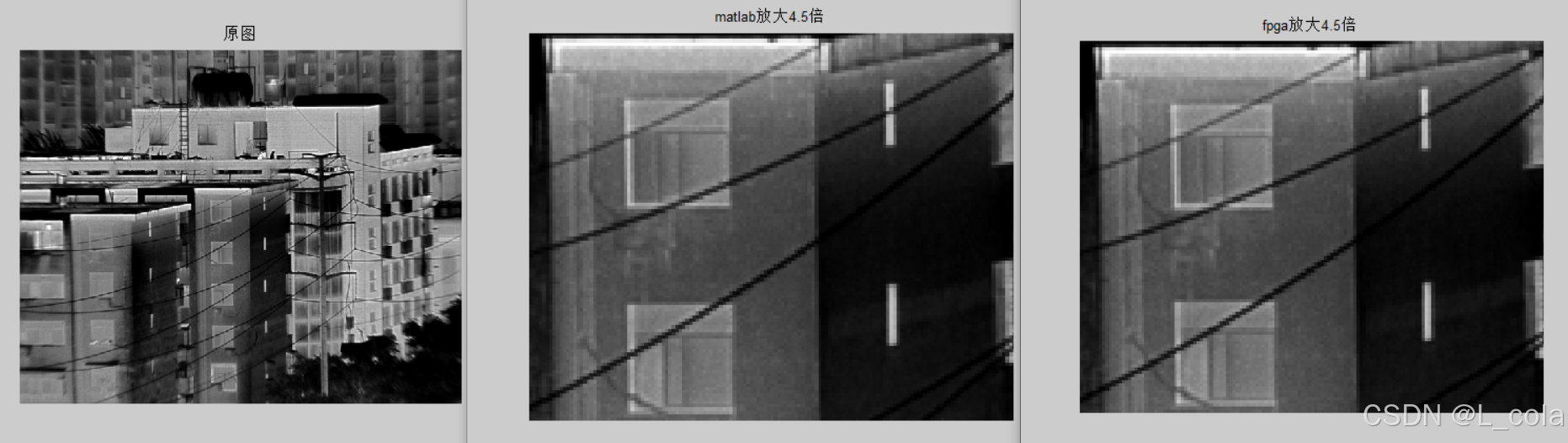

下图是放大4.5倍,原图、matlab放大效果图和fpga放大效果图。

下一章继续介绍,在FPGA中用双线性插值实现无极放大。

1585

1585

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?