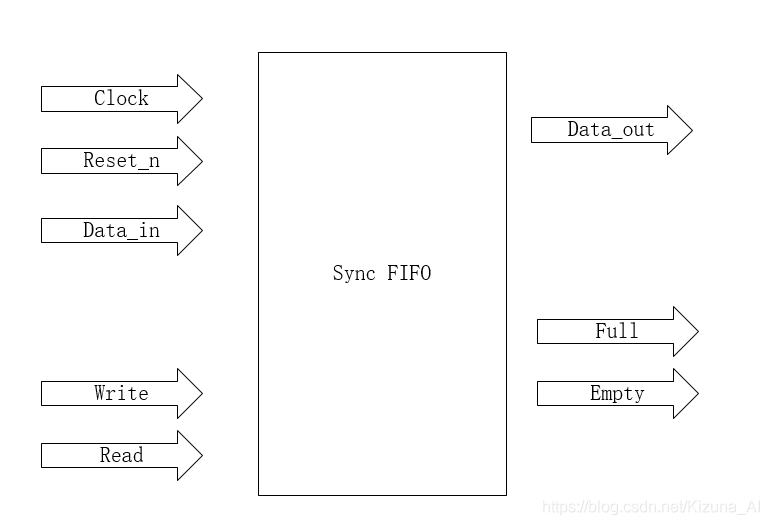

fifo的输入输出端口如上图所示。

本次设计fifo输入输出32位,深度为8,读写信号由上游发送,空满信号由fifo产生。

设计要点:

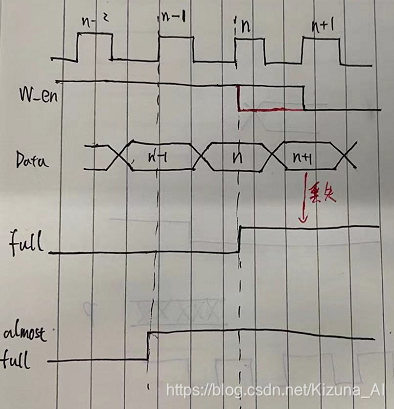

1.在实际应用中,write信号和read信号由上游模块给出,有可能存在fifo满了,write信号还没有拉低的情况;或者说上游节点write信号不拉低,只是说收到了full信号后当前数据不发生变化,这就需要考虑到full信号拉高的时候的时序问题,如果没处理好就可能会丢失掉最后一个数据,就如下图所示。

假设fifo深度为n,如果使用时序逻辑,full信号在第n个时钟上升沿拉高,但要下一个时钟上升沿才能检测到,然后write信号才能拉低。此时的第n+1个数据已经发送出去了,fifo又满了,无法写入,就会造成数据丢失。此处可以用almost_full解决这个问题,在fifo快满的时候提示上游节点别发送新数据。本设计没使用almost_full信号,使用了组合逻辑:用full信号取反&w_en信号,用这个条件来控制fifo是否继续写入。此时write信号拉低与否就跟我fifo是否写入没有太大关系了:write信号就算拉高我也不一定写,write信号拉低我一定不写。组合结果就如上图红笔所示,写使能信号在full信号拉低后自己马上拉低,上游节点可以通过这个信号来判断是否继续发送

本文介绍了简单FIFO的设计要点及其实现细节,包括输入输出端口定义、空满信号处理、读写逻辑控制等,并提供了RTL代码示例。

本文介绍了简单FIFO的设计要点及其实现细节,包括输入输出端口定义、空满信号处理、读写逻辑控制等,并提供了RTL代码示例。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2887

2887

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?