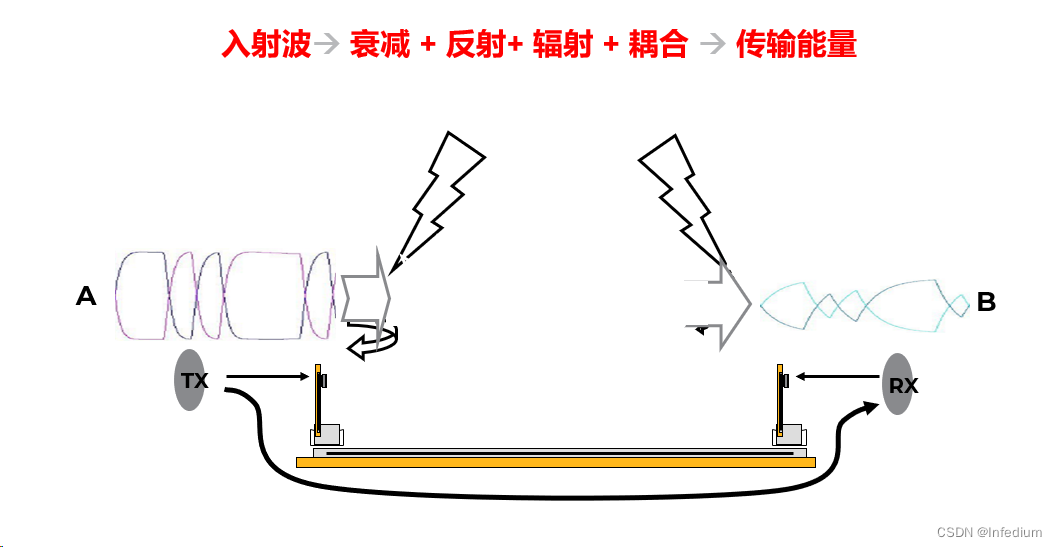

信号完整性概念

信号设计核心问题

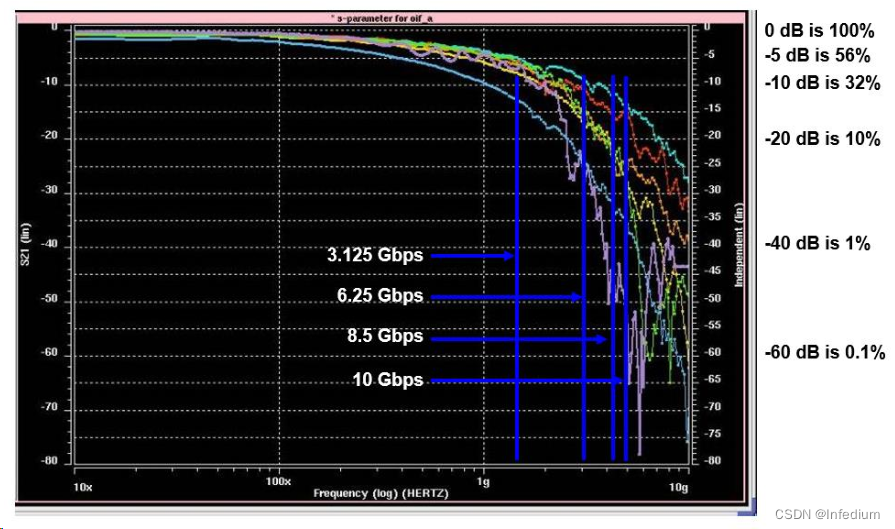

损耗

阻抗

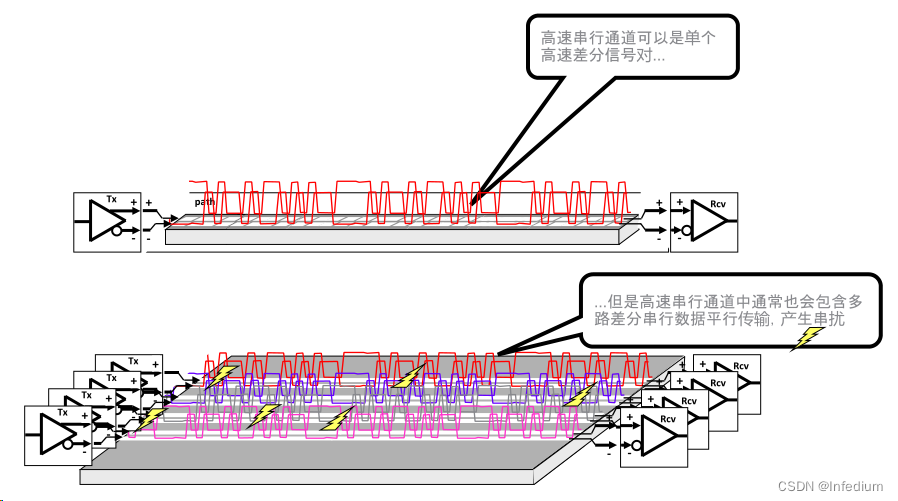

串扰

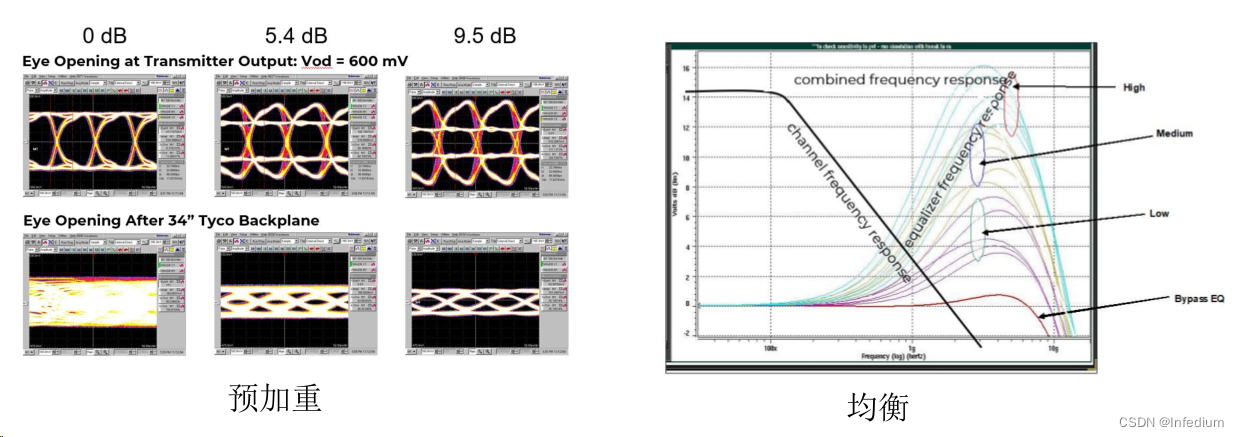

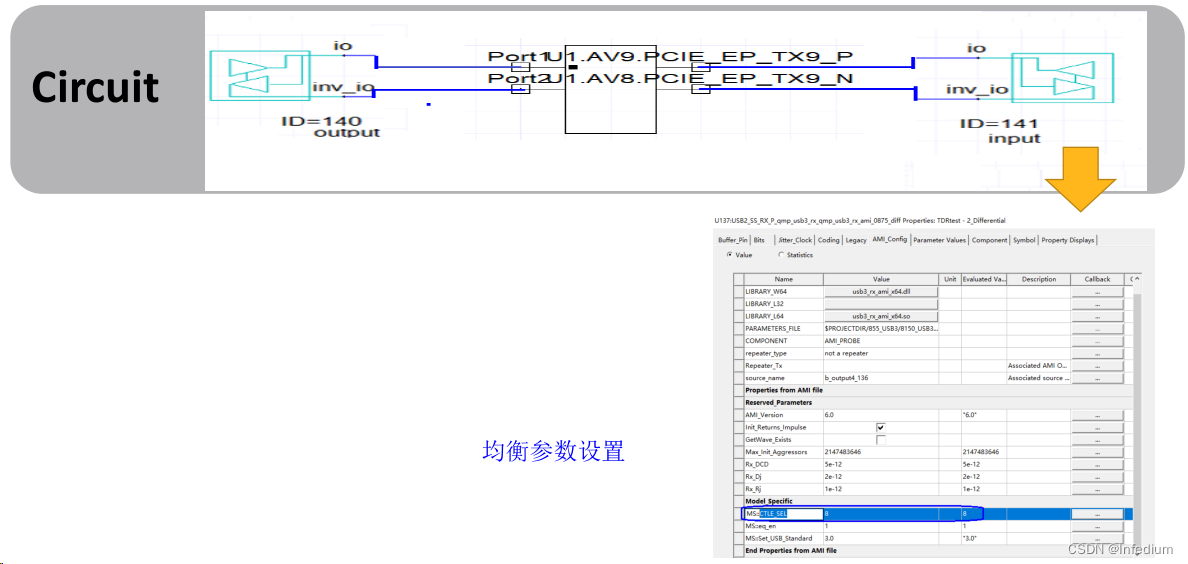

均衡器

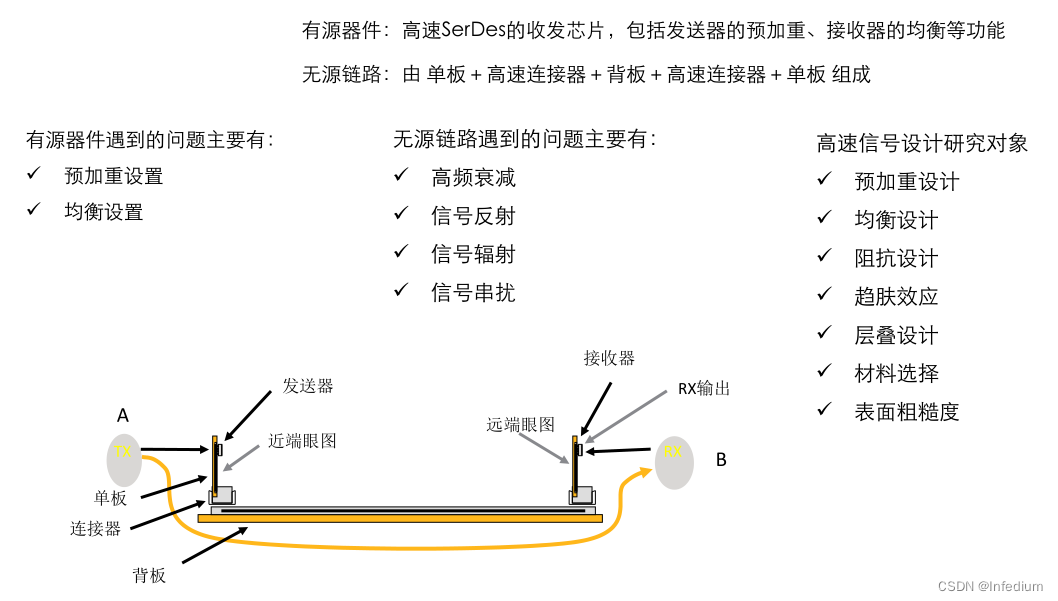

设计中的挑战

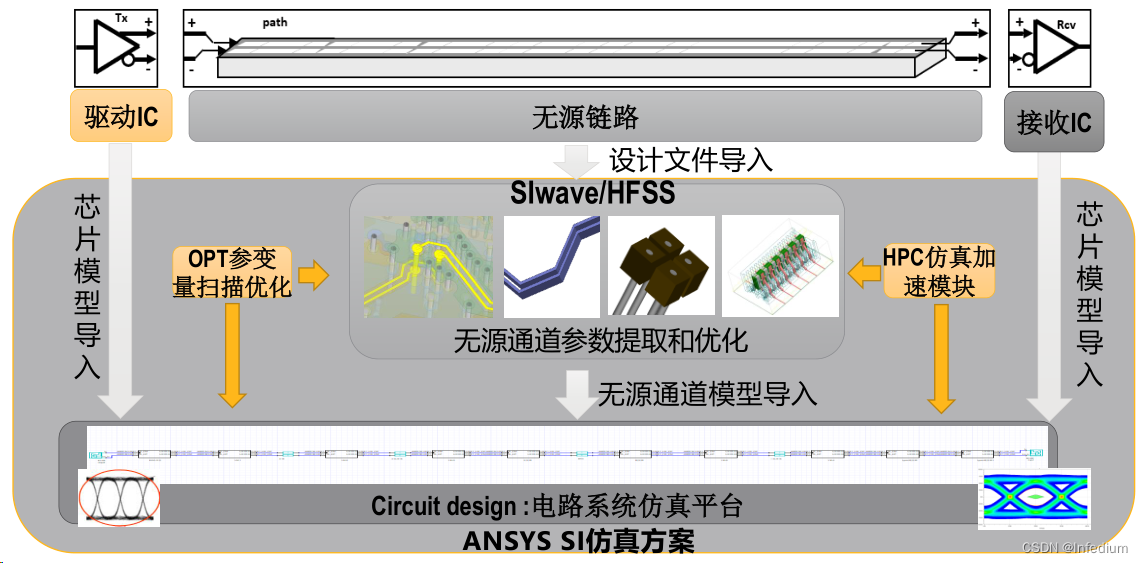

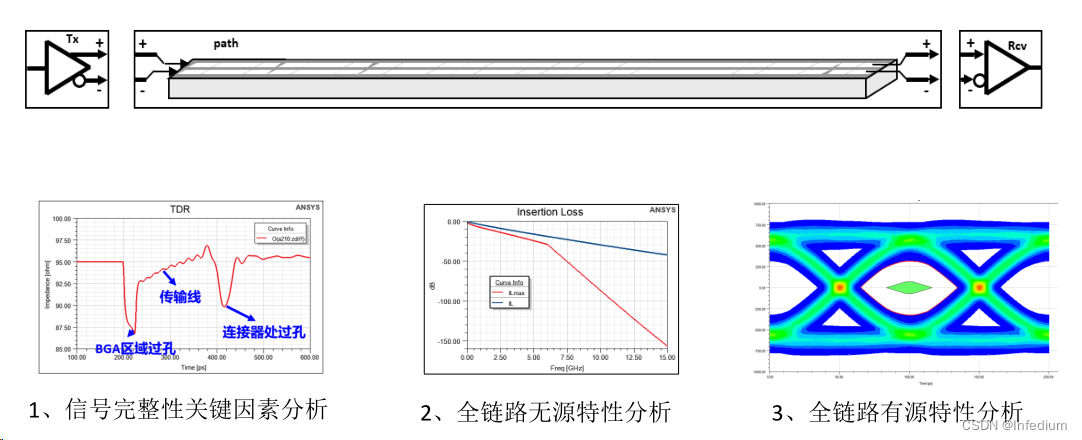

Ansys信号完整性方案

信号完整性分析的基本流程

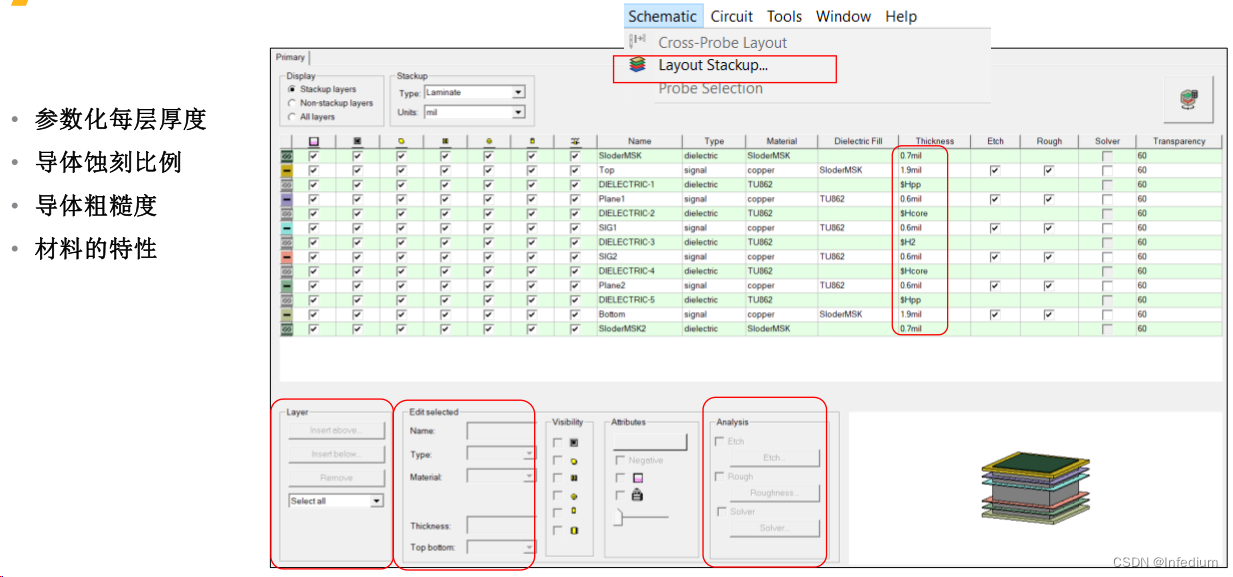

层叠设计

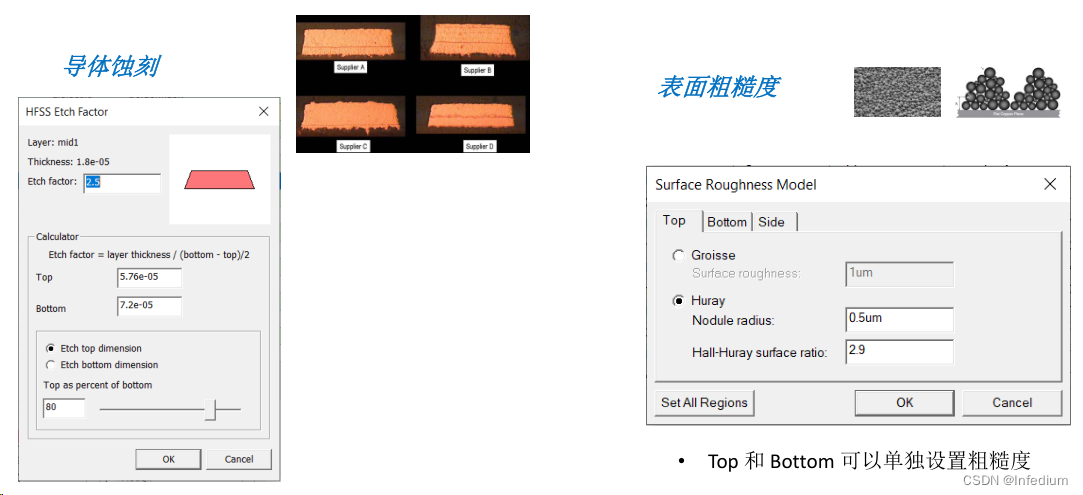

导体蚀刻&粗糙度

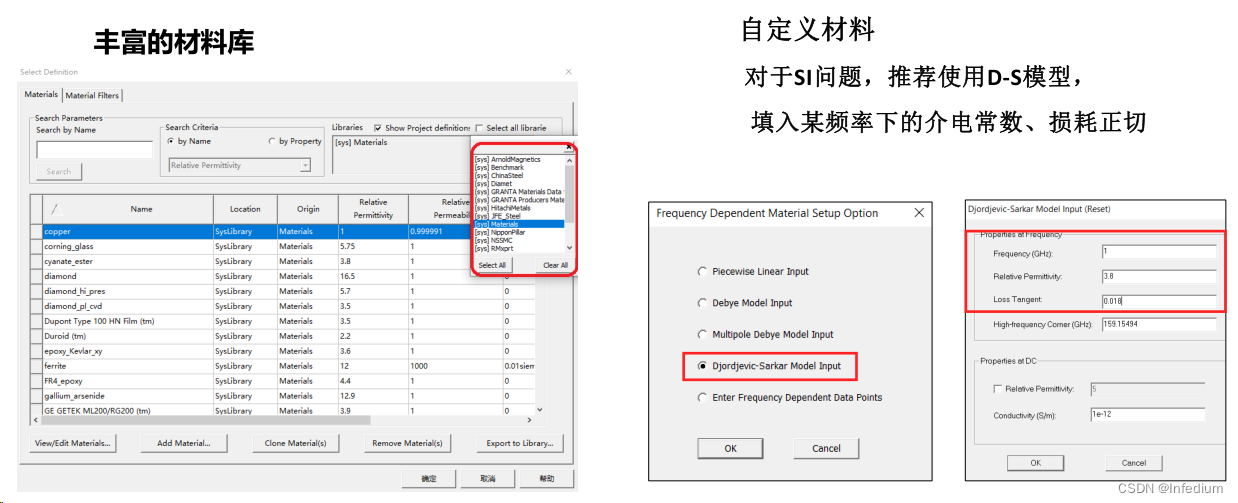

材料设计

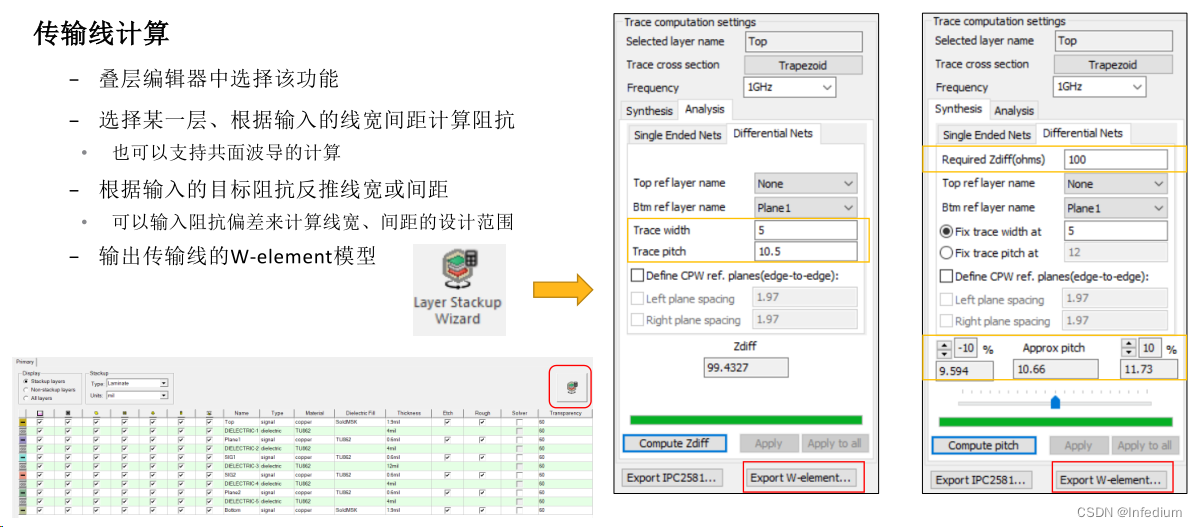

传输线设计

阻抗

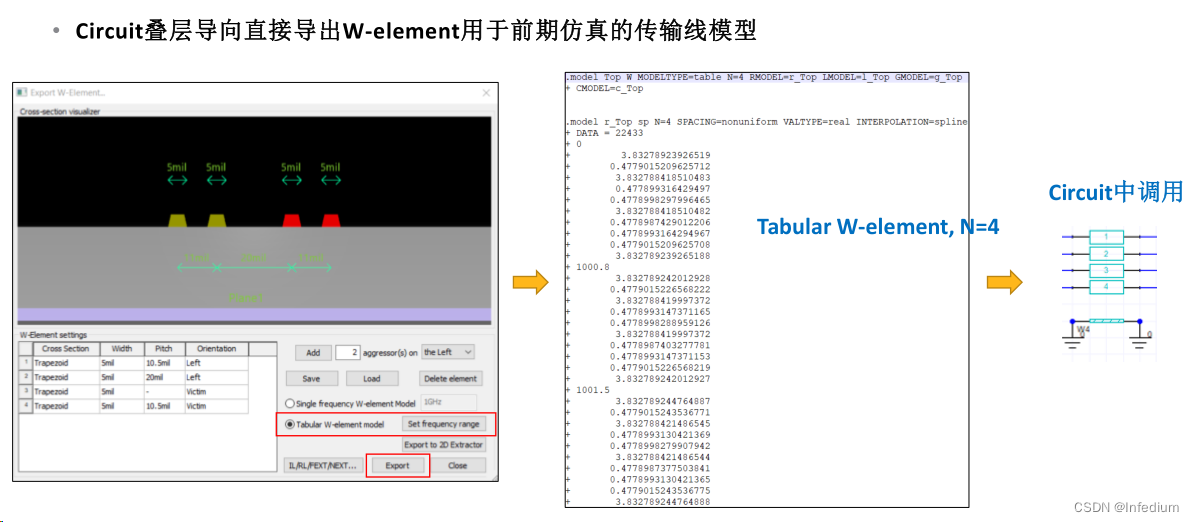

W model

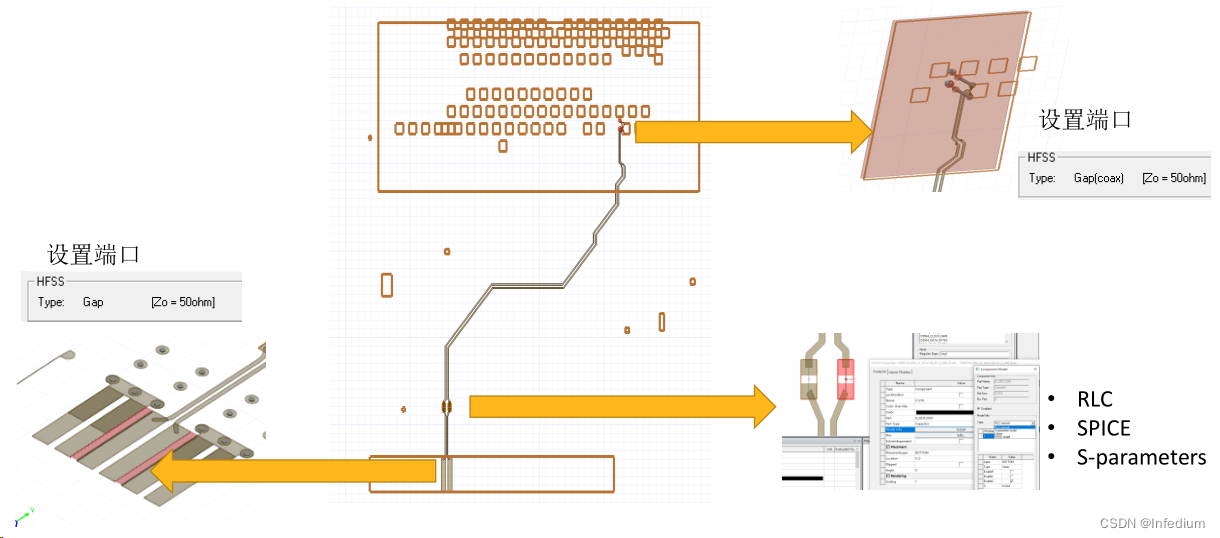

过孔建模与优化

信号线整个通道参数提取

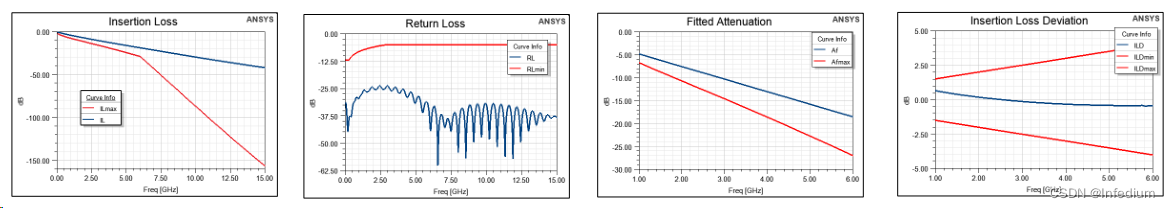

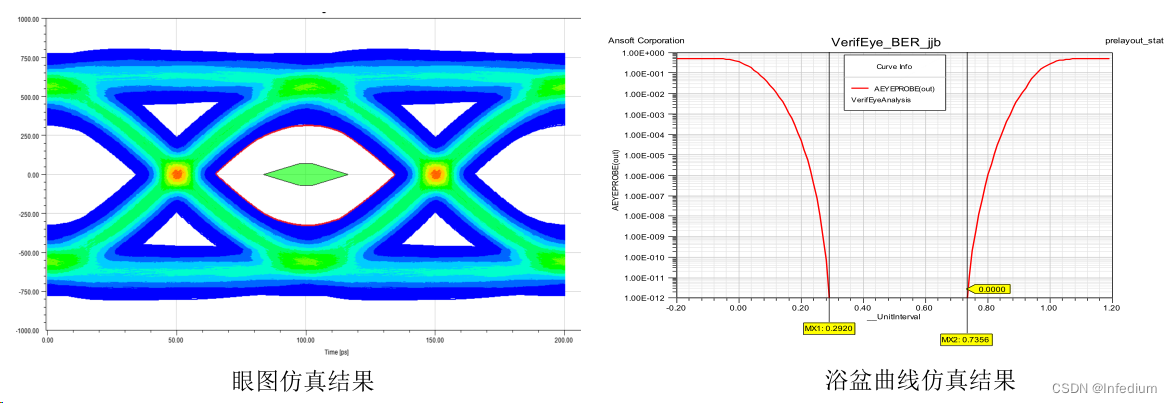

无源链路规范要求及分析(10G-BASE-KR为例)

规范IEEE 802.3 2015 Section5中Annex 69B Interconnect characteristics定义了背板架构的无源链路设计要求:

• IL (Insertion Loss)

• RL (Return Loss)

• ILD (Insertion Loss Deviation)

• ICR (Insertion Loss to Crosstalk Ratio)

无源链路的相应的曲线,必须满足在设计指标之内。

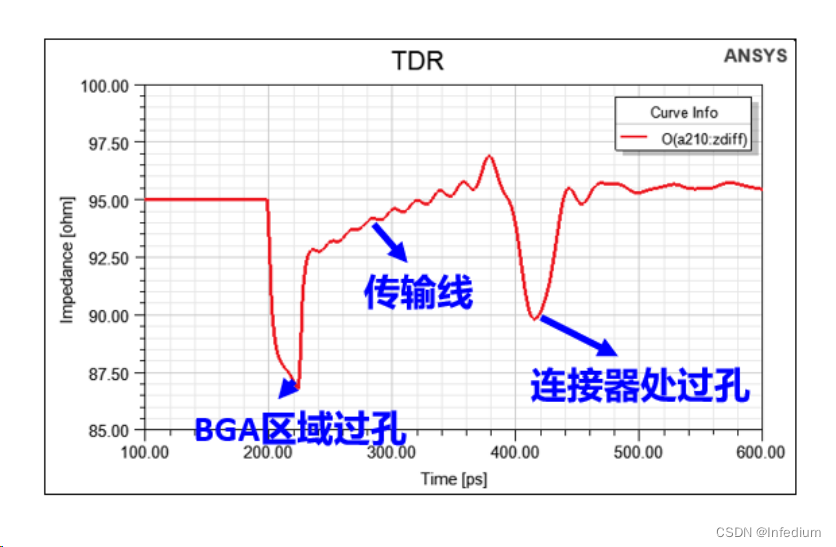

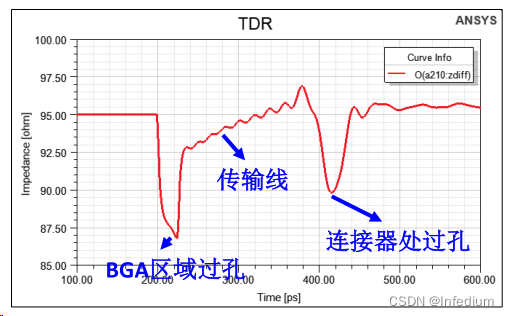

无源链路TDR分析

• TDR用于观察无源链路的阻抗变化,可以快速定位无源链路中需要优化的位置

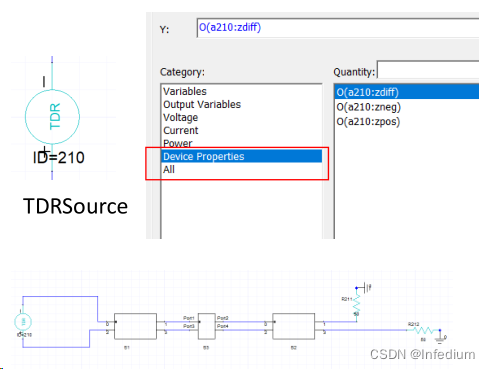

• 在Circuit 中进行TDR分析非常方便,内置TDR Source,无需手动编辑公式或插入函数

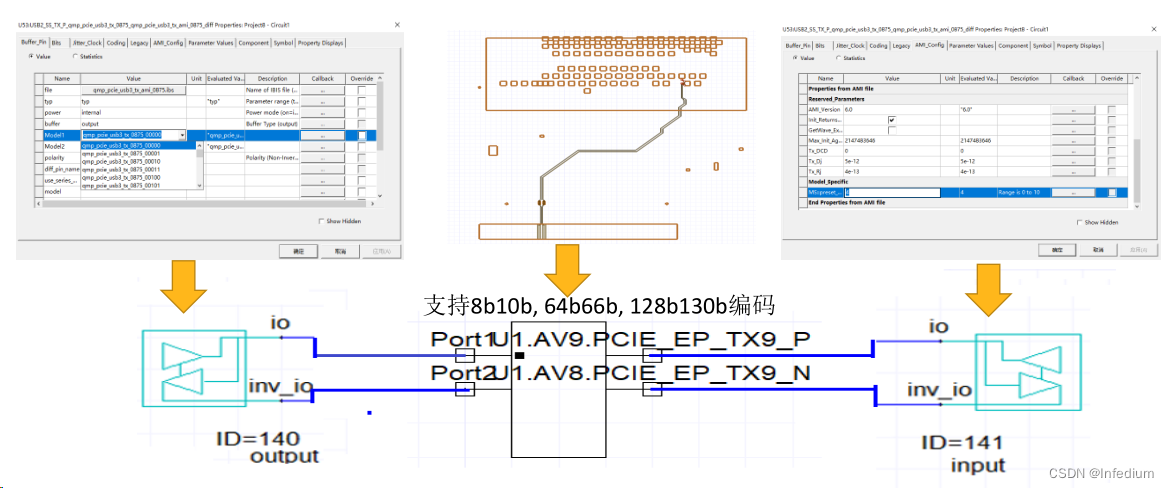

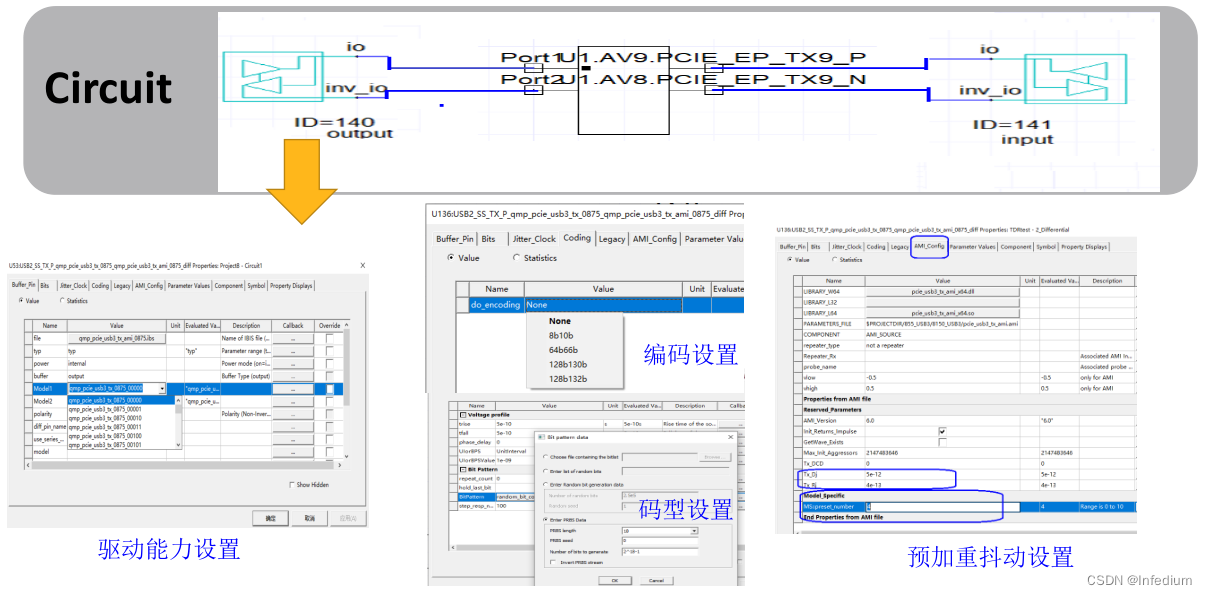

搭建系统电路图

求解参数设置

查看结果

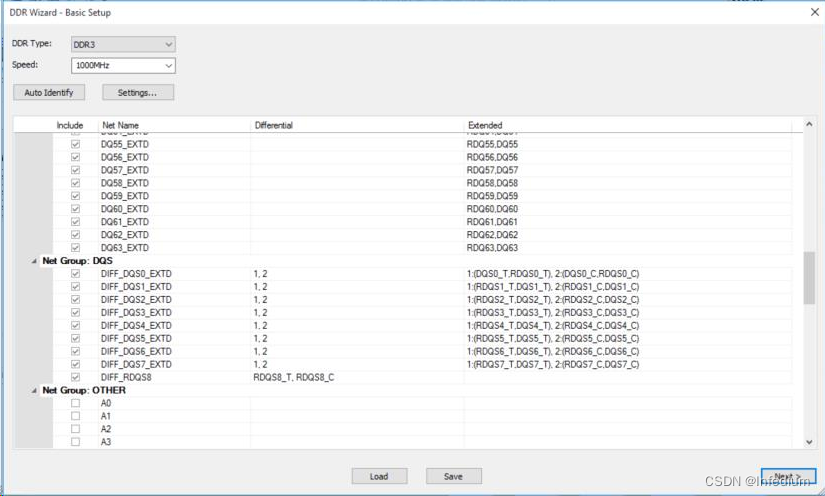

DDRwizard仿真工具介绍

DDR仿真分析工作向导

‐ 基于网络名称自动识别信号网络:DQ, DQS, CLK and ADDR lines

‐ 可通过改变延迟使data, strobe and clock 等信号同步

‐ 支持读写模式分析设置

‐ 支持IBIS corner (fast/slow/typical) 分析设置

信号完整性设计:关键要素、挑战与仿真工具应用

信号完整性设计:关键要素、挑战与仿真工具应用

本文探讨了信号完整性设计的关键概念,包括阻抗匹配、串扰控制和无源链路特性。Ansys解决方案在信号完整性分析中发挥作用,涵盖了从损耗、TDR分析到DDR仿真工具如DDRwizard的使用。重点介绍了无源链路规范和TDR在设计中的应用,以及DDR仿真工作向导的功能。

本文探讨了信号完整性设计的关键概念,包括阻抗匹配、串扰控制和无源链路特性。Ansys解决方案在信号完整性分析中发挥作用,涵盖了从损耗、TDR分析到DDR仿真工具如DDRwizard的使用。重点介绍了无源链路规范和TDR在设计中的应用,以及DDR仿真工作向导的功能。

1175

1175

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?