ZYNQ7020 GMAC1 EMIO裸机功能调试

ZYNQ嵌入式系统开发流程

上图中step1~step4为硬件设计部分主要在vivado工具中完成,step5为软件设计在sdk工具中完成,step6为最后的板子调试在开发板上验证功能。

1:创建Vivado工程

打开 Vivado,进入 Vivado界面后,点击下图红框中的Create Project创建vivado工程。

然后在弹出的创建Vivado工程向导界面,点击“ Next ”。 如下图所示

进入工程命名界面。设置工程名为“ zynq_gmac1_emio”,工程路径可使用任意路径,注意工程名和路径只能由英文字母、数字和下划线组成 不能包含中文、空格以及特殊字符!

确认已经 勾选“ Create project subdirectory””,点击“ Next 如下图所示

设置工程类型。此处我们选择RTL Project。本次不需

要添加源文件和约束文件,所以勾选Do not specify sources at this time。勾选之后会省略后面添加源文件和约束文件的步骤,点击“ Next”直接跳到器件选型界面。

领航者zynq7020开发板核心板的具体型号为:xc7z020clg400-2,如下图

完成vivado工程的创建,如下:

2:创建Process System

在弹出的界面中进行如下操作

添加完成后如下图

配置DDR型号为MT41J256M16RE-125

根据开发板原理图配置UART引脚以及GMAC,SD,QSPI的引脚并且启动EMIO,选择SD和QSPI的引脚是为了后续程序固化以及Linux调试使用,启用EMIO是因为PL测的PHY芯片的复位引脚接在BANK35上的EMIO上。

如下图:

根据原理图配置bank0和bank1的电压

配置QSPI引脚

配置UART引脚:

配置SD引脚:

配置GMAC0引脚:

配置GMAC1引脚:

配置GPIO包含MIO和EMIO

配置PL侧的时钟如下:

保存完如下图所示:

可以看到GMAC1在使用EMIO的时候默认是GMII接口而实际的硬件电路中EMIO的PHY使用的是RGMII接口,所以需要一个GMII转RGMII的接口IP,xilinx官方提供了这样的一个IP可以直接添加使用如下图添加GMII转RGMII的IP:

添加完成后如下:

双击配置GMII To RGMII如下图:

添加反相器用于复位GMII To RGMII;

双击配置反相器:

接下来手动连线:

设置模块自动化:

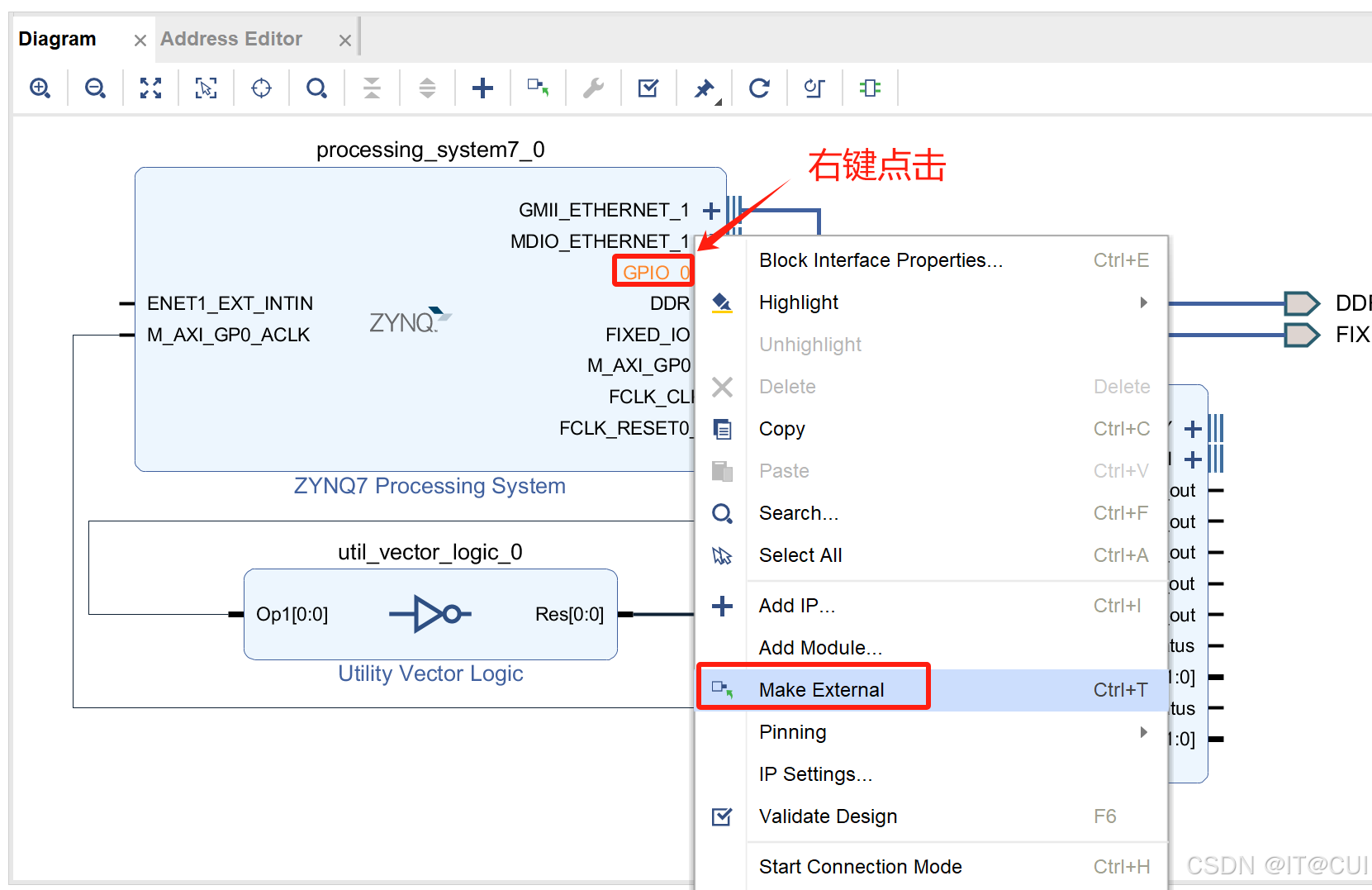

引出EMIO引脚以及MDIO和RGMII引脚如下:

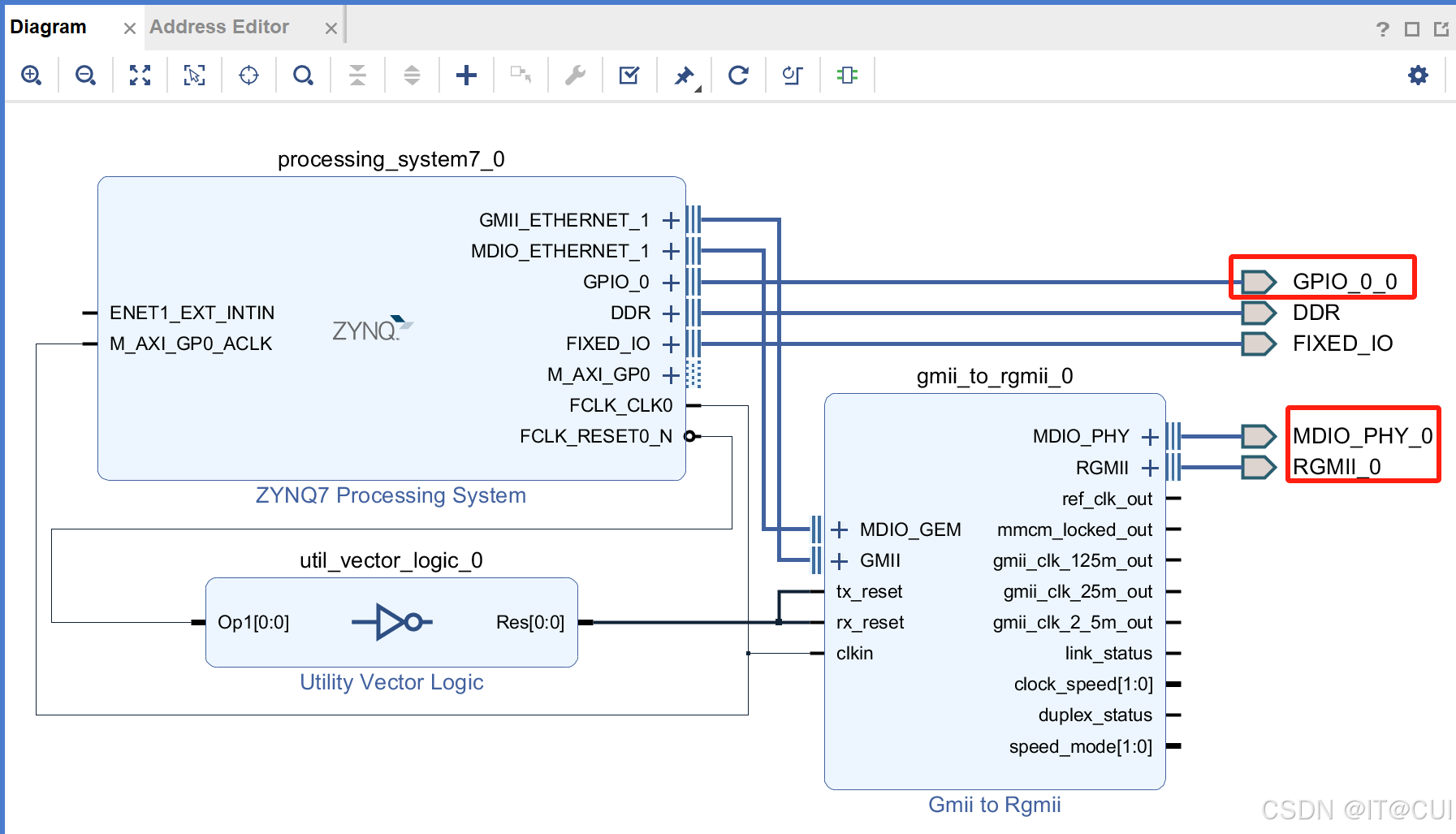

同理依次引出MDIO和RGMII接口如下图:

校验硬件设计如下:

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2489

2489

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?