用Quartus编写一个一位全加器,然后使用Modelsim仿真。

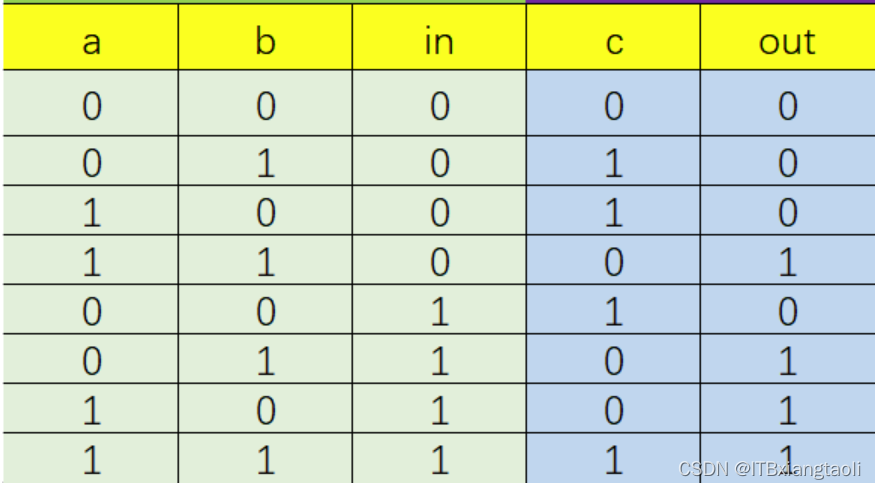

真值表如下:

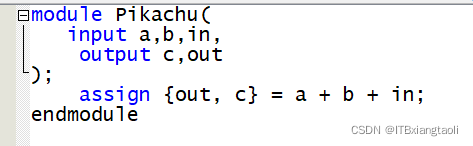

Verilog代码

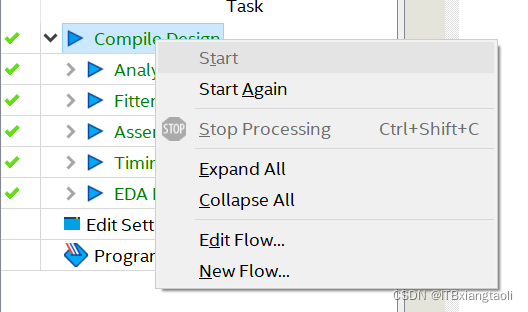

然后点击start

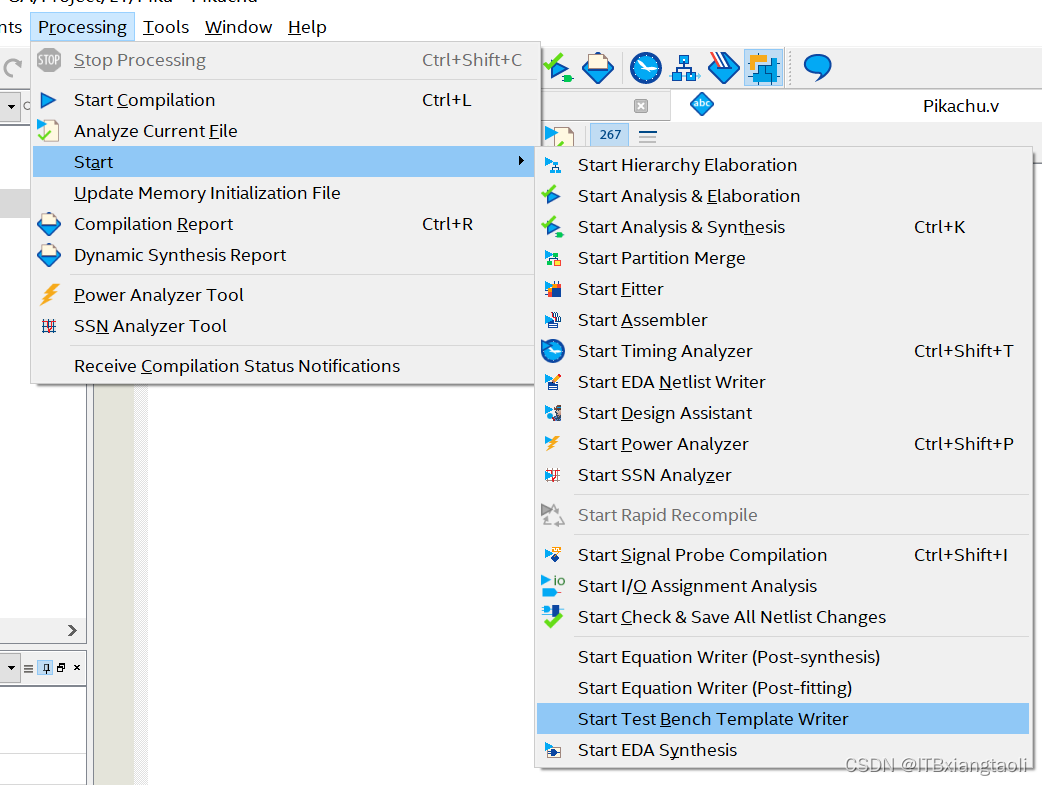

然后选择processing---start---start test bench template writer

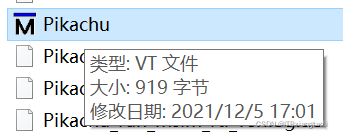

编译好后,会在本项目文件夹中生成一个modelsim文件夹,里面有一个vt文件,就是quartus根据verilog代码自动生成的用于modelsim仿真的testbench文件,双击打开。

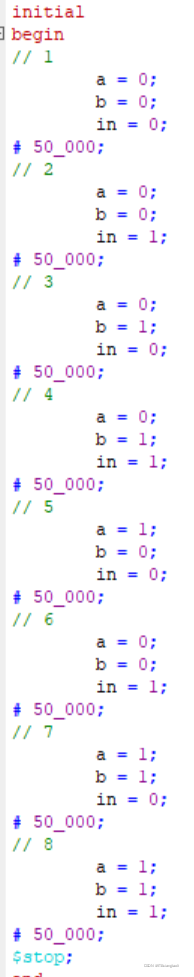

里面已经根据先前的verilog自动例化好了,可以直接在里面编写输入信号。a b in都与真值表中的一致,依次间隔50000ps,也就是50ns。

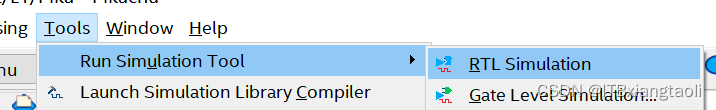

然后点击Tools---Run Simulation Tool---RTL Simulation即可进行仿真。

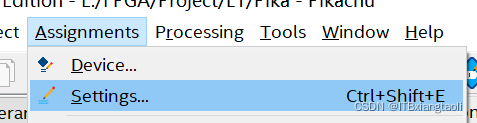

但目前仿真没有结果,还需要在Quartus中对testbench文件进行设置。

但目前仿真没有结果,还需要在Quartus中对testbench文件进行设置。

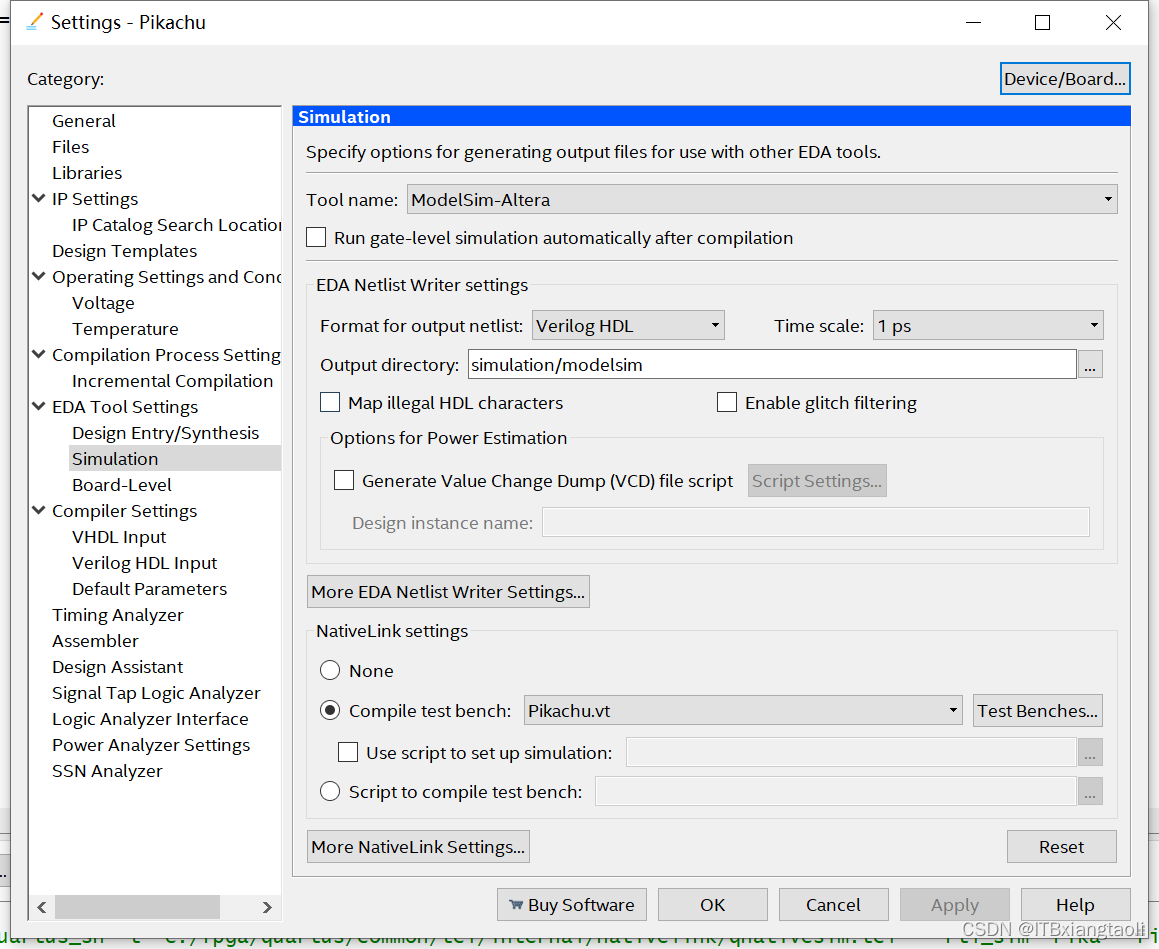

Tool name就选择自己安装的仿真软件,我安装的是Modelsim-Altera。

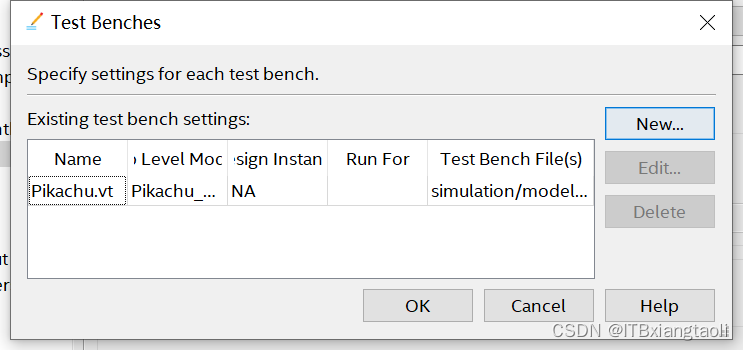

点击Test Benches,点击New

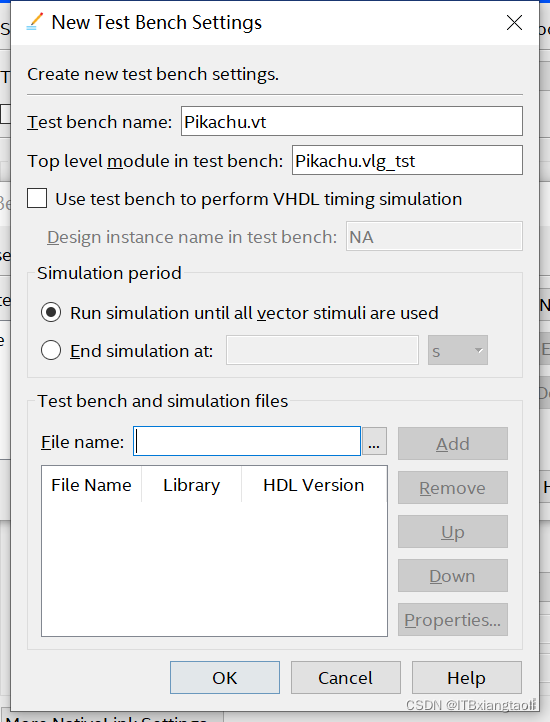

Name就是项目名.vt,Pikachu_vlg_tst就是vt文件中的头名。

![]()

File name中就选择vt文件,然后Add,然后一路ok。

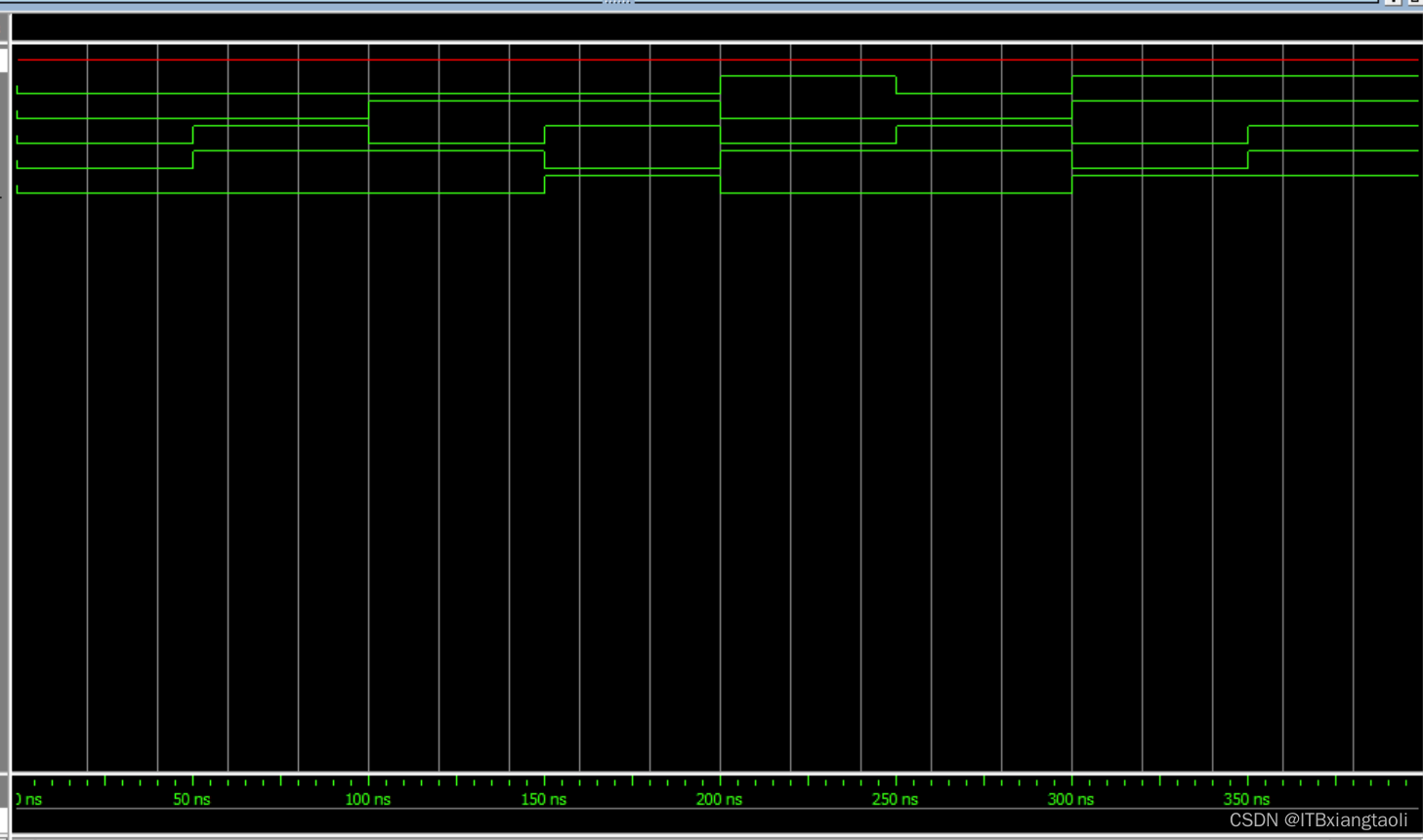

这些都设置正确后,再次编译,得到正确结果。若视低电平为0,高电平为1,则每50ns中的信号高低与真值表中每列的0和1完全对应。

该博客介绍了如何使用Quartus软件编写一个一位全加器的Verilog代码,并通过Modelsim进行仿真。首先,根据真值表编写Verilog代码,然后在Quartus中配置并启动testbench模板生成器。接着,编译项目并在生成的modelsim文件夹中找到仿真testbench文件,根据真值表设置输入信号。最后,通过选择Tools—RunSimulationTool—RTLSimulation运行仿真。在仿真无结果的情况下,需要在Quartus中设置TestBenches,指定Modelsim为仿真工具并配置testbench文件,完成设置后重新编译即可获得与真值表对应的仿真结果。

该博客介绍了如何使用Quartus软件编写一个一位全加器的Verilog代码,并通过Modelsim进行仿真。首先,根据真值表编写Verilog代码,然后在Quartus中配置并启动testbench模板生成器。接着,编译项目并在生成的modelsim文件夹中找到仿真testbench文件,根据真值表设置输入信号。最后,通过选择Tools—RunSimulationTool—RTLSimulation运行仿真。在仿真无结果的情况下,需要在Quartus中设置TestBenches,指定Modelsim为仿真工具并配置testbench文件,完成设置后重新编译即可获得与真值表对应的仿真结果。

380

380

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?