若要实现分N频占空比非50%的奇数分频器,只需要计数到(N-1)/2时取反输出,计数到N-1时再次取反输出即可。

若要实现占空比为50%的奇数分频器,核心问题是如何处理半个周期,考虑到一个周期内clk的上升沿和下降沿正好相差半个周期,所以分别利用上升沿和下降沿得到两个占空比非50%的奇数分频器,这两个奇数分频器的上升沿、下降沿都相差半个周期,因此再将这两个占空比非50%的奇数分频器相或,就能实现占空比为50%的奇数分频器

占空比非50%奇数分频器Verilog代码

//5分频、占空比3:2的奇数分频器

module Riven(

clk,

rst,

clko

);

input clk;

input rst;

parameter N = 5;

output reg clko = 0;

reg [3:0] cnt = 0;

always @(posedge clk or negedge rst) begin

if(!rst) begin

//cnt <= 0;

clko <= 0;

end

else if(cnt == (N-1)/2) begin

clko <= ~clko;

cnt <= cnt + 1;

end

else if(cnt == N-1) begin

cnt <= 0;

clko <= ~clko;

end

else begin

cnt <= cnt + 1;

end

end

endmodule

Modelsim输入代码,只写了关键的一部分。

initial

begin

clk = 0;

forever

#25clk = ~clk;

$display("Running testbench");

end

initial

begin

rst = 0;

#1000;

rst = 1;

#1000;

rst = 0;

#1000;

rst = 1;

#1000;

$stop;

end

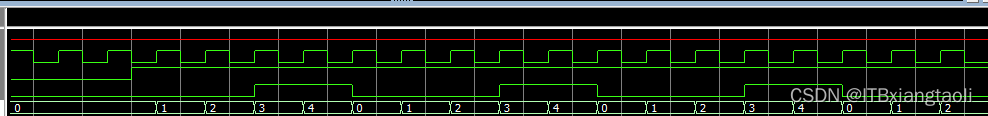

Modelsim仿真结果

占空比50%的技术分频器Verilog代码

//5分频、占空比50%的奇数分频器

module Fiora(

clk,

rst,

clko1,

clko2,

clko

);

input clk;

input rst;

parameter N = 5;

output reg clko1 = 0;

output reg clko2 = 0;

output reg clko = 0;

reg [3:0] cnt1 = 0;

reg [3:0] cnt2 = 0;

always @(posedge clk or negedge rst) begin

if(!rst) begin

cnt1 <= 0;

clko1 <= 0;

end

else if(cnt1 == (N-1)/2) begin

clko1 <= 1;

cnt1 <= cnt1 + 1;

end

else if(cnt1 == N-1) begin

cnt1 <= 0;

clko1 <= 0;

end

else begin

cnt1 <= cnt1 + 1;

end

end

always @(negedge clk or negedge rst) begin

if(!rst) begin

cnt2 <= 0;

clko2 <= 0;

end

else if(cnt2 == (N-1)/2) begin

clko2 <= 1;

cnt2 <= cnt2 + 1;

end

else if(cnt2 == N-1) begin

cnt2 <= 0;

clko2 <= 0;

end

else begin

cnt2 <= cnt2 + 1;

end

end

always@(*)begin clko = clko1|clko2;end

endmodule

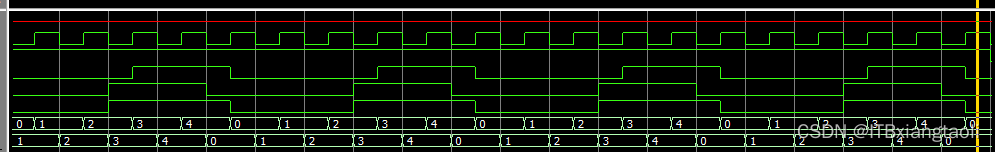

Modelsim仿真结果

本文介绍了如何设计占空比非50%和50%的奇数分频器。对于占空比非50%的奇数分频器,通过在计数到(N-1)/2和N-1时取反输出来实现。而50%占空比的奇数分频器则是结合上升沿和下降沿的两个非50%占空比分频器,通过逻辑或操作达到平衡。提供了Verilog代码示例并进行了Modelsim仿真验证。

本文介绍了如何设计占空比非50%和50%的奇数分频器。对于占空比非50%的奇数分频器,通过在计数到(N-1)/2和N-1时取反输出来实现。而50%占空比的奇数分频器则是结合上升沿和下降沿的两个非50%占空比分频器,通过逻辑或操作达到平衡。提供了Verilog代码示例并进行了Modelsim仿真验证。

1049

1049

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?