关注、星标公众号,精彩内容每日送达

来源:网络素材

您是否担心 RTL 设计中的延迟?

您的设计是否有效并经过优化?

AMD Vitis HLS 可帮助您解决这些问题。

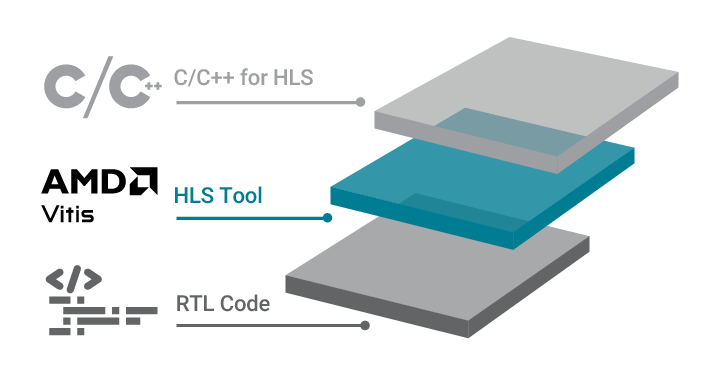

通过 Vitis HLS,您可将 C/C++ 函数综合到 RTL 中,从而轻松创建复杂设计算法。

AMD Vitis™ HLS 工具允许用户通过将 C/C++ 函数综合成 RTL,轻松创建复杂的 FPGA 算法。Vitis HLS 工具与 Vivado™ Design Suite(用于综合、布置和布线)及 Vitis™ 统一软件平台(用于所有异构系统设计和应用)高度集成。

使用 Vitis HLS 流程,用户可针对 C 代码应用指令,创建专门用于所需实现方案的 RTL。

不仅可从 C 语言源代码创建多个设计架构,而且还可启用用于高质量 Correct-by-Construction RTL 的路径。

C 语言仿真可用于验证设计,支持比基于 RTL 的传统仿真更快的迭代。

Vitis HLS 工具具有一系列丰富的分析及调试工具,其可促进设计优化。

全新推出的Vitis HLS资源,具有以下特点:

较之传统的 RTL,Vitis HLS 可实现更快的设计验证和更高效的迭代

通过 Vitis HLS,开发者可使用 C/C++ 代码中的自动 pragma 推理、流水线循环和函数等高级功能来满足系统性能要求

点击阅读原文即刻下载和查看更多关于Vitis HLS的资源

AMDVitisHLS工具提供了一种将C/C++代码综合为RTL的方法,简化复杂FPGA算法的创建。通过C语言仿真和自动优化功能,如pragma推理和流水线循环,实现快速设计验证和高效迭代。VitisHLS与VivadoDesignSuite和Vitis统一软件平台集成,支持全面的异构系统设计。

AMDVitisHLS工具提供了一种将C/C++代码综合为RTL的方法,简化复杂FPGA算法的创建。通过C语言仿真和自动优化功能,如pragma推理和流水线循环,实现快速设计验证和高效迭代。VitisHLS与VivadoDesignSuite和Vitis统一软件平台集成,支持全面的异构系统设计。

67

67

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?