写在前面的话

边沿检测,就是检查某个信号的跳变沿,分为上升沿检测和下降沿检测。

思路很简单,就是先对信号延迟一拍,再用组合逻辑对原信号和延迟信号判断。

那为什么要做边沿检测呢?

在数字电路中,不同模块之间常常需要通信和数据传输,这里会有标志信号,而标志信号的开始、长度和结束时间点是一个比较关键的问题,这里就要做边沿检测,通过边沿检测获取标志信号。

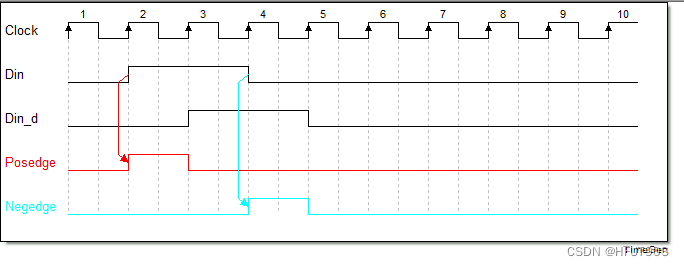

先看图:

有图可以得到:

(1)上升沿检测,pos = Din && (~Din_d) ;

(2)下降沿检测,neg = (~Din) && Din_d ;

直接记图就行,手撕代码的时候对照图写就行。

注意:

(1)最近的笔试题变得鸡贼了,不是让你直接写边沿检测或者画示意图。

(2)有的笔试题会先给你一堆波形图,让你在里面写出某几个信号的关系。

(3)这里是单bit边沿检测,涉及到多bit边沿检测时,有的鸡贼题目直接给的是二进制总线信号。

(4)一定要保持敏感,只要涉及两个信号是延迟一拍,优先考虑是不是边沿检测。

Verilog示例

// -----------------------------------------------------------------------------

// Copyright (c) 2014-2022 All rights reserved

// -----------------------------------------------------------------------------

// Author : HFUT904 1320343336@qq.com

// File : edge_detect.v

// Create : 2022-11-04 16:36:13

// Revise : 2022-11-04 16:36:13

// Editor : HFUT Integrated Circuit Design & Research Center

// Verdion: v1.0

// Description: 单bit 边沿检测

// -----------------------------------------------------------------------------

module edge_detect ( //单bit边缘检测

input clk ,

input rst_n ,

input key_in ,

output pos_edge ,

output neg_edge ,

output data_edge

);

reg [1:0] data_r;

always@(posedge clk or negedge rst_n) begin

if (!rst_n) begin

data_r[0] <= 0;

data_r[1] <= 0;

end

else begin

data_r[0] <= key_in;

data_r[1] <= data_r[0];

end

end

assign pos_edge = data_r[0] & ~data_r[1]; //检测上升沿

assign neg_edge = ~data_r[0] & data_r[1]; //检测下降沿

assign data_edge = pos_edge | neg_edge; //双边缘检测

endmodule

总结

没啥重要的,记好图就行。

本文介绍数字电路中的边沿检测原理及其重要性,并给出使用Verilog语言实现单bit边沿检测的具体示例代码。

本文介绍数字电路中的边沿检测原理及其重要性,并给出使用Verilog语言实现单bit边沿检测的具体示例代码。

1114

1114

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?