数字IC经典电路(5)—glitch_free_clock_switch(无毛刺时钟切换电路)

前言

数字电路中,无毛刺时钟切换电路(glitch-free clock switching circuit)是在多时钟域设计和高速数字电路中保时钟信号在切换时不会引入不必要的毛刺(glitch),从而避免不稳定的操作或错误的信号传输。

毛刺(Glitch)是指在信号切换过程中的瞬时不稳定性而产生的短暂且不期望的脉冲或信号波动。毛刺通常会在信号的过渡阶段(例如从低电平到高电平,或从高电平到低电平)产生,并且其持续时间非常短,组合逻辑会不可避免的产生毛刺,而由于组合逻辑后通常会存在Latch/DFF用于滤波,因此属于组合逻辑电路对于毛刺的容忍度相对较高,毛刺虽然会影响输出,但只要不在输入变化时发生,它通常不会导致系统整体故障。

先进工艺制程中,毛刺(glitch)的宽度通常与多种因素相关,特别是与晶体管开关速度、信号传播延迟、寄生效应、电源噪声等紧密相关。随着工艺节点的缩小,毛刺的宽度和特性会发生变化,通常受以下几个方面的影响:

1. 晶体管开关速度

在先进的工艺制程(如7nm、5nm及更小节点)中,晶体管的开关速度显著提高。更小的晶体管能够更快地响应输入信号的变化,导致信号的过渡更加迅速。理论上,随着开关速度的增加,毛刺的持续时间可能会更短(宽度更窄)。但同时,先进工艺节点中的寄生电容和寄生电感会变得更复杂,可能会导致毛刺的幅度增加,即便其宽度较窄。

较小的制程节点:开关速度更快,毛刺宽度通常较小,可能达到皮秒级别(ps)。

较大的制程节点:开关速度较慢,毛刺可能持续更长时间(纳秒级别)。

2. 寄生效应

在先进的工艺中,寄生电容和寄生电感的影响变得更加显著。随着晶体管尺寸减小,寄生效应(尤其是寄生电容)会对信号的过渡产生较大的影响,导致毛刺的产生更加复杂。寄生效应可能会导致信号在切换过程中出现不稳定,导致宽度较长的毛刺。因此,即使在较小的工艺节点中,寄生效应仍然是一个不能忽视的因素,可能会在某些情况下拉长毛刺的宽度。

3. 信号传播延迟与毛刺宽度

信号在电路中的传播延迟会直接影响毛刺的宽度。在更小的制程节点中,虽然晶体管的速度较快,但由于寄生电容和电感的增加,信号在电路中传播的速率可能不均匀,导致某些路径上的信号较慢,产生时序误差,从而引发较长时间的毛刺。此外,设计中的时钟树、时序优化等因素也会影响毛刺的持续时间。

较小的工艺节点:虽然晶体管开关速度更快,但寄生效应增加,传播延迟差异可能导致毛刺持续时间的增加。

较大的工艺节点:传播延迟差异可能较小,但信号的过渡速度较慢,毛刺可能持续时间更长。

4. 电源噪声的影响

在先进制程中,电源噪声的影响变得更加重要。较低的电源电压和更小的晶体管尺寸使得电源噪声对电路的影响更为显著,尤其是在高速操作时。电源噪声可能导致电路在切换过程中的不稳定性,产生毛刺。通常,电源噪声会影响毛刺的幅度,但也可能引起毛刺的宽度增加。

5. 工艺不一致性

由于先进工艺制程中晶体管和其他组件的尺寸越来越小,制造过程中产生的偏差也可能影响毛刺的宽度。即便在同一款芯片的不同部分,工艺上的微小差异也可能导致不同的信号响应速度,从而影响毛刺的持续时间。

项目简介

项目列举了常用的几种经典以及改进后的可综合glitch_free_clock_switch 模块,并基于VCS完成功能/gate/post(40nm)仿真验证。

项目难度:⭐

项目推荐度:⭐⭐⭐

项目推荐天数:1~2天

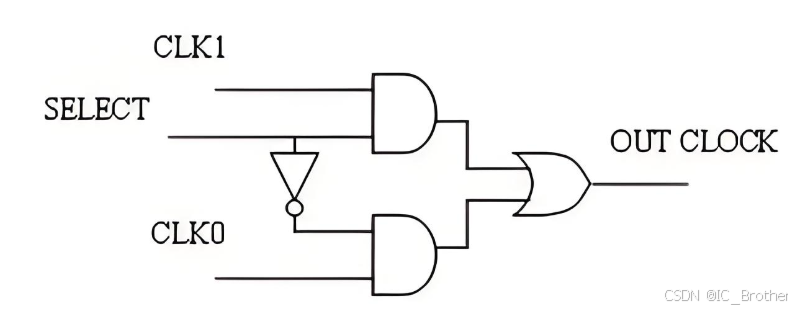

1)CLK_Switch0

Figure 1 采用了一种普通的Mux作为时钟切换单元,当SELECT信号处于CLK1和CLK0跳变沿时,非常容易产生Glitch。

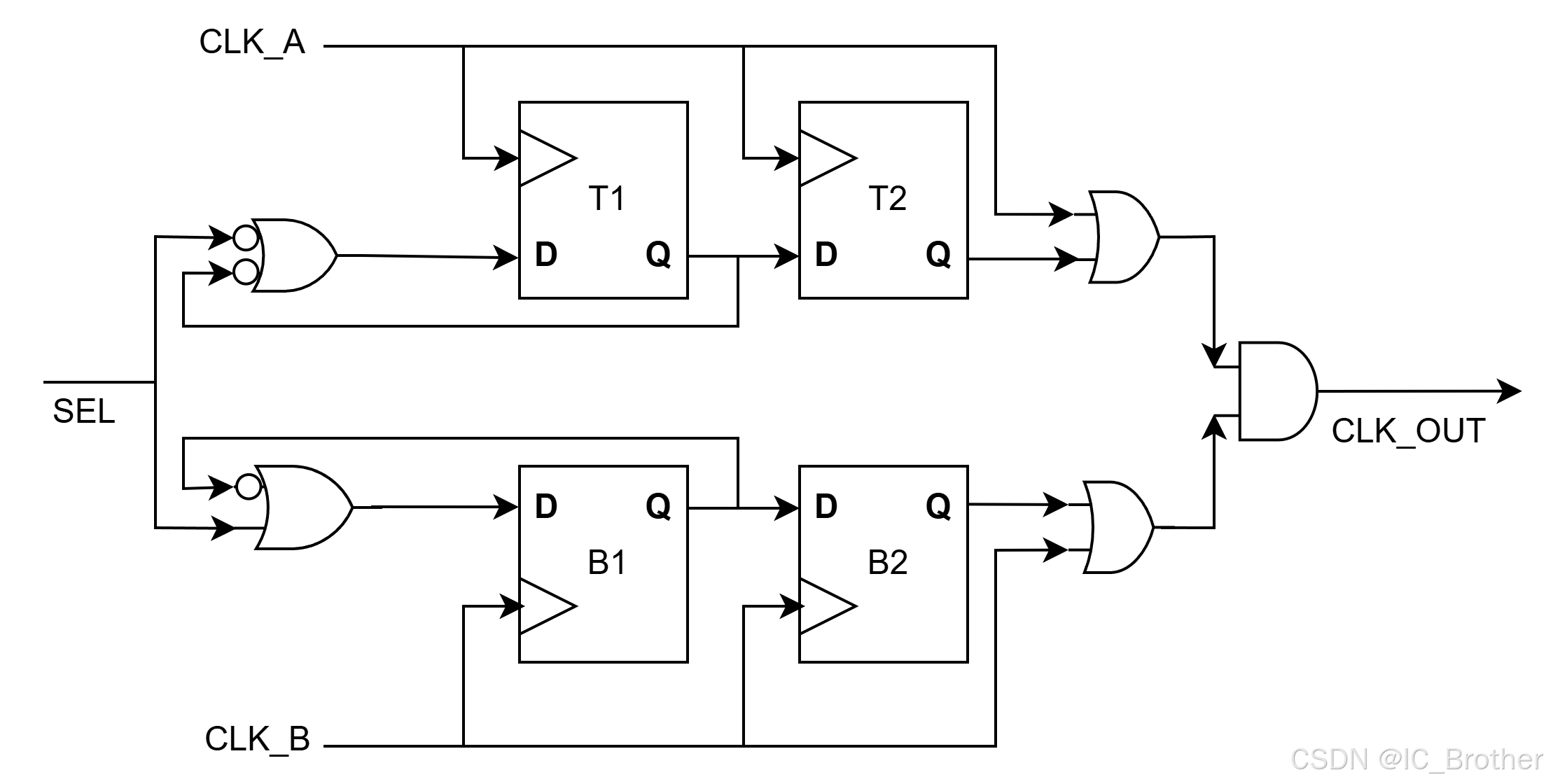

2)CLK_Switch1

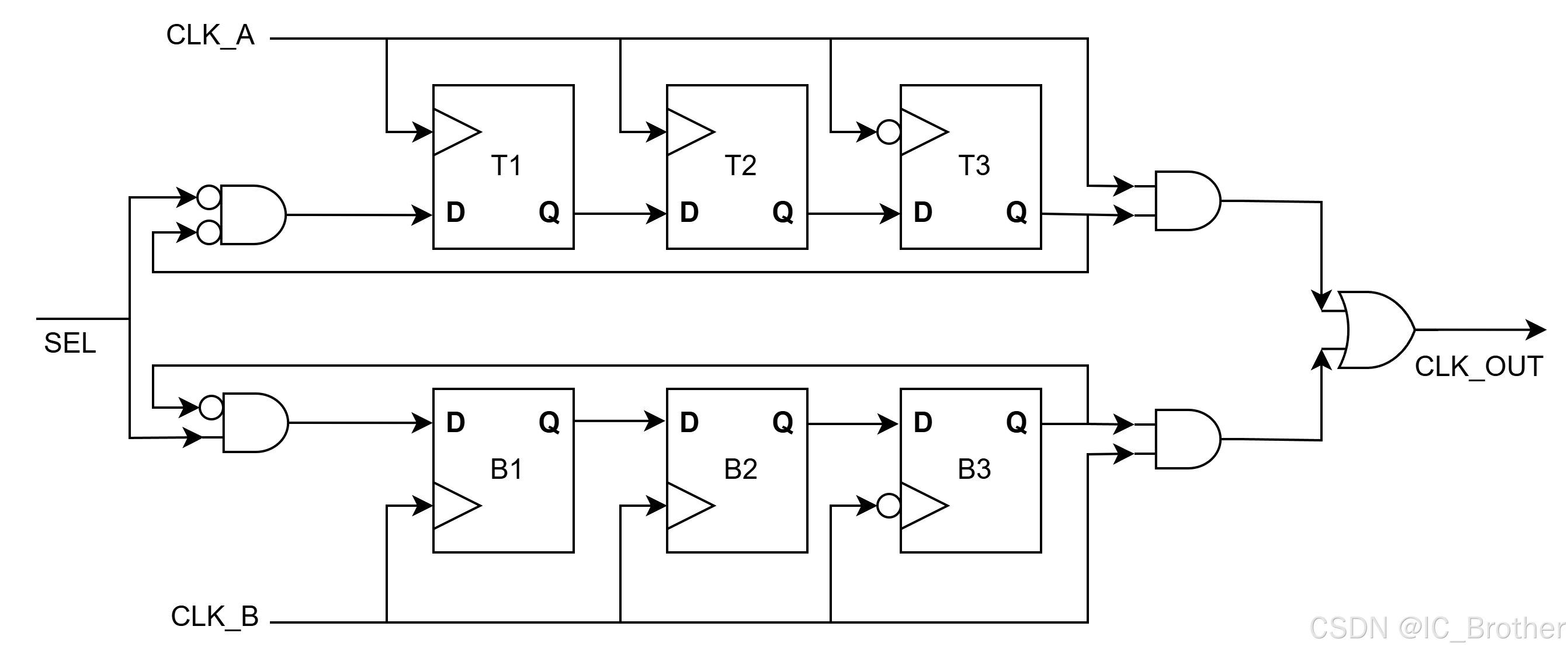

Figure 2是一种传统风格的glitch_free_clock_switch, 门控信号的产生过程如下,由外部切换信号和内部控制信号共同产生时钟切换控制信号,并经过两级电平信号同步器,再以时钟下降沿采样后,gating 时钟,得到无毛刺的输出时钟,并经过逻辑门输出,由于SEL信号同时钟信号CLK_A/CLK_B为异步关系,因此,在无毛刺 clock mux中最好使用双同步器而不是单DFF。

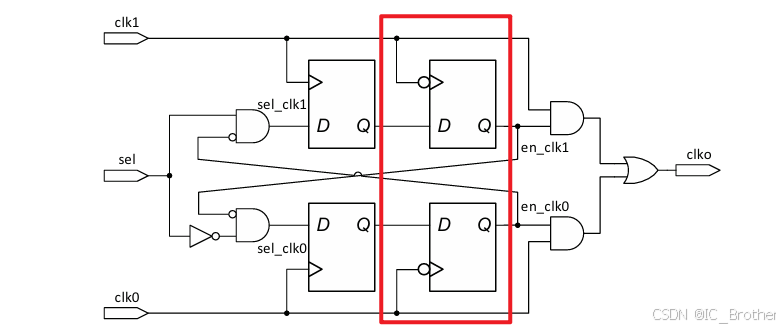

Figure 3是基于传统风格的glitch_free_clock_switch, 减少一级DFF,用于提升切换速度。门控信号的产生过程如下,由外部切换信号和内部控制信号共同产生时钟切换控制信号,并经过两级电平信号同步器,再以时钟下降沿采样后,gating 时钟,得到无毛刺的输出时钟,并经过逻辑门输出,由于SEL信号同时钟信号CLK_A/CLK_B为异步关系,因此,在无毛刺 clock mux中最好使用双同步器而不是单DFF。

这两种电路的其目的是处理不相关(即完全异步)的时钟。该解决方案基本上由两个交叉耦合的触发器链(作为双触发器同步器)和一些逻辑组成。时钟与使能信号相结合,最终产生输出时钟。输出时钟。

交叉耦合可防止两个时钟同时启用,而利用双触发器同步器可防止产生毛刺和亚稳态。

3)CLK_Switch2/3

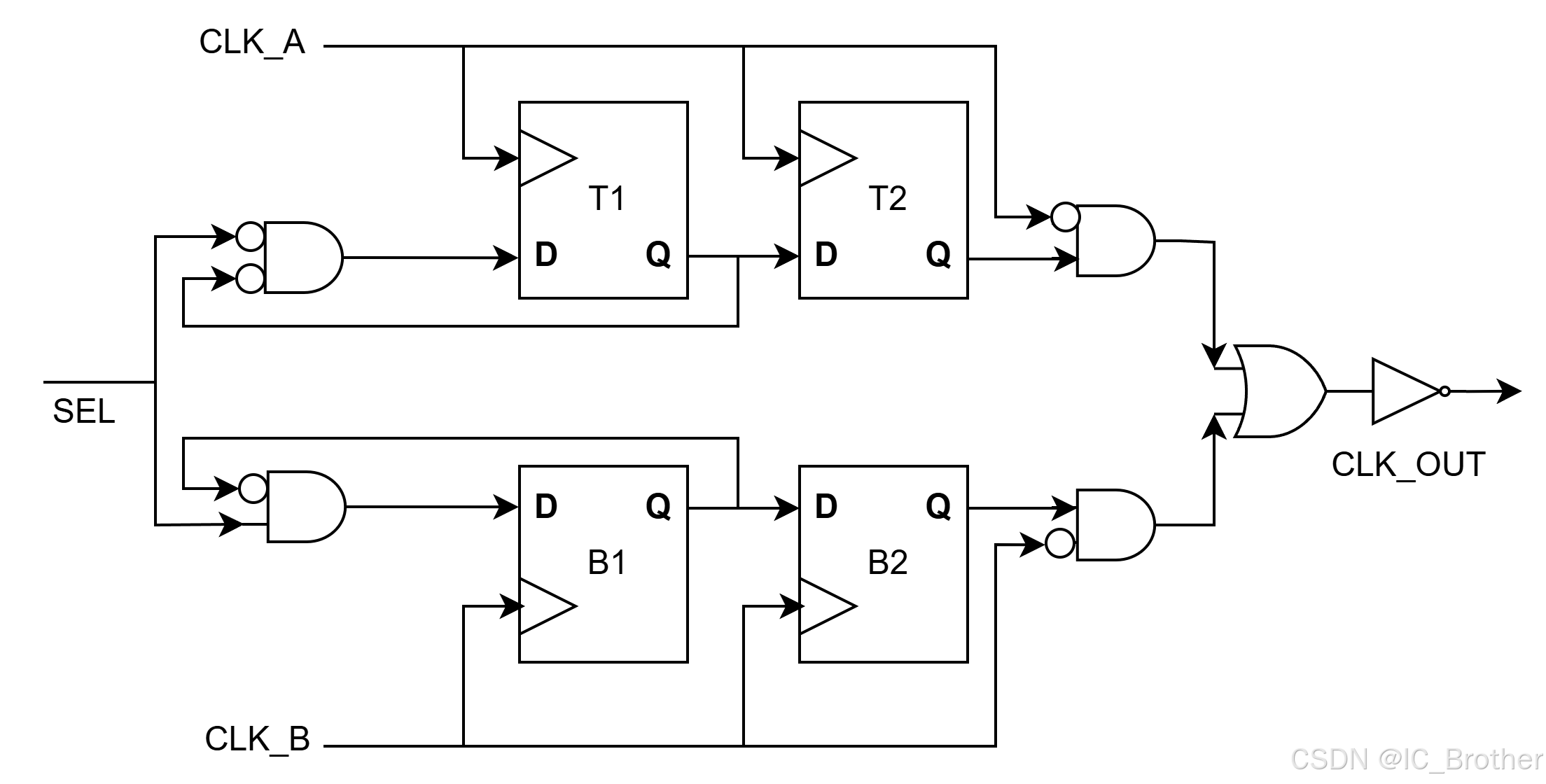

基于传统结构的glitch_free_clock_switch电路结构,可以继续拓展出以下两个glitch_free_clock_switch, 首先均采用上升沿触发的DFF,用以适用于占空比变化的时钟域切换,上述混合使用上升沿和下降沿的电路中,需要时钟占空比达到50%,而在实际芯片工作中,随着PVT等因素的不同,占空比无法精确保证,Figure 4和Figure 5展示的glitch_free_clock_switch均采用相同触发沿的DFF,避免了clock jitter对于clk switch的影响,提高适用范围。

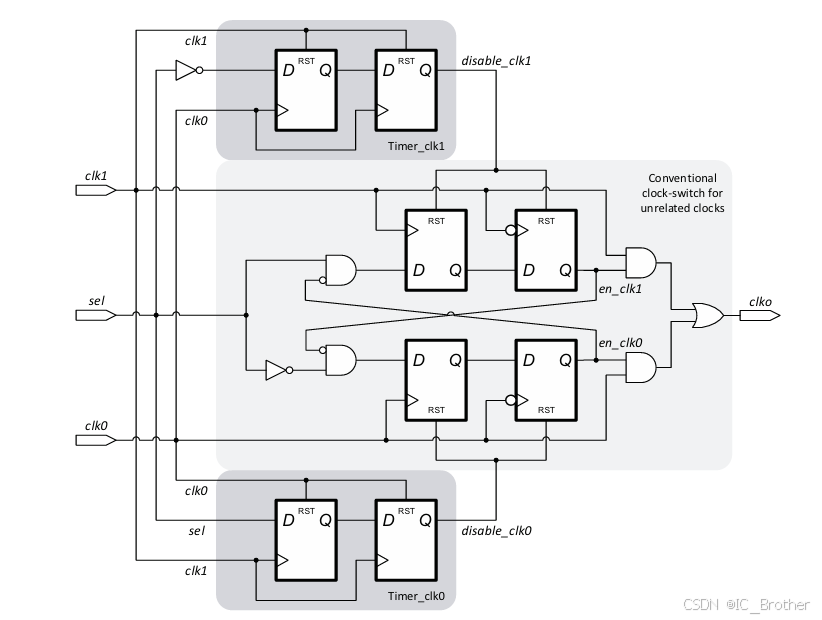

4)New_CLK_Switch0

一种新型的glitch_free_clock_switch 结构如Figure 6所示,为每个时钟源添加了一个定时器,用于观察时钟信号的活动情况,并指示相应时钟是否处于非活动状态。定时器只对当前未被输入 sel 选择的时钟激活。因此,如果下一个时钟源 clk1 被选中,定时器 Timer_clk0 将被激活,反之亦然。最后,每个定时器都会产生一个禁用信号(disable_clk0/1),一旦检测到超时,该信号就会被确认。

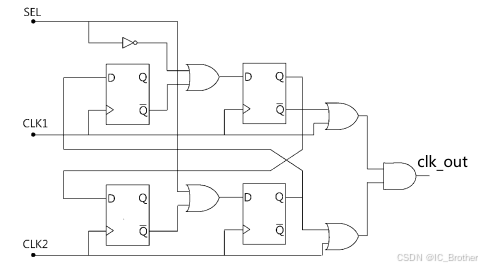

5)New_CLK_Switch1

另一种改进型的glitch_free_clock_switch 结构如Figure 7所示,该结构将时钟使能逻辑插入到同步器中,在选择源时钟时,通过消除源时钟变化时的时钟glicth,可以提供稳定的时钟源。该种结构的优势在于可以通过分组集成,利于将多路时钟信号切换到指定输出。

仿真结果

1)仿真环境需求

-

测试平台包括VCS/DC/Verdi;

-

仿真包含功能仿真/pre,门级仿真/gate以及DC综合后SDF反标仿真/post;

2)仿真波形

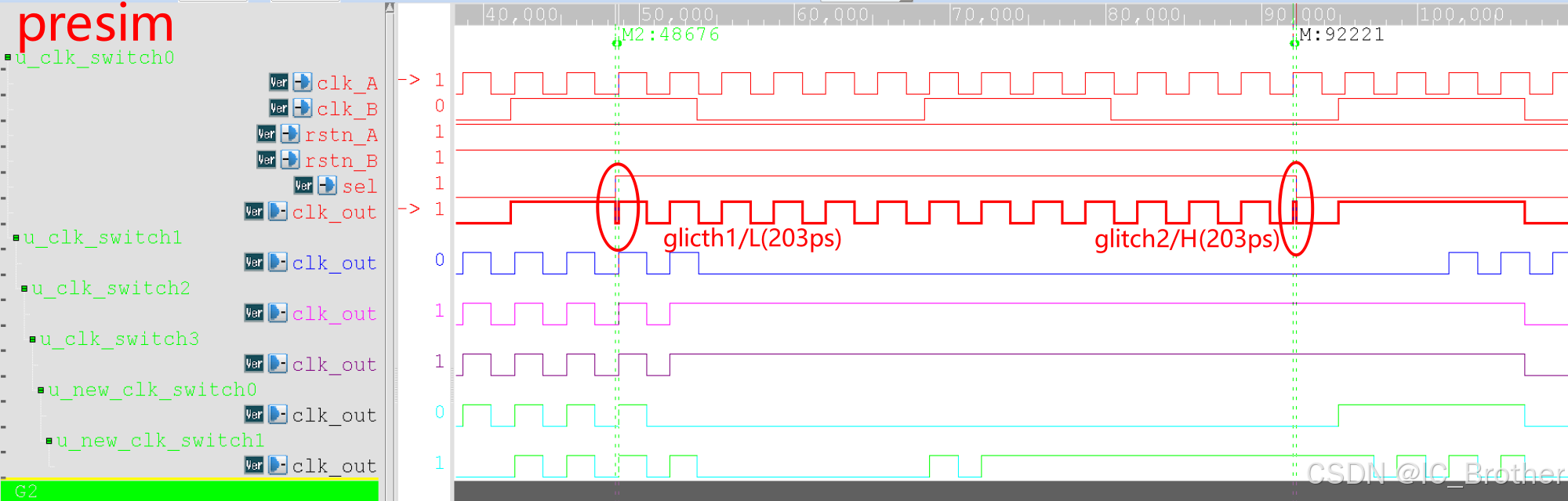

项目采用40nm工艺库,完成了包括前仿真/pre,门级仿真/gate以及DC综合后仿/post,完成上述几种clock_free_clock_switch的功能及时序验证,并输出面积/功耗等对比数据。参考时钟的设计频率和占空比描述如下:

glitch_free_clock switch Design Spec:

==========================================

clk_A : Period 3334ps /Duty Cycle: 45%

clk_B : Period 26581ps /Duty Cycle: 55%

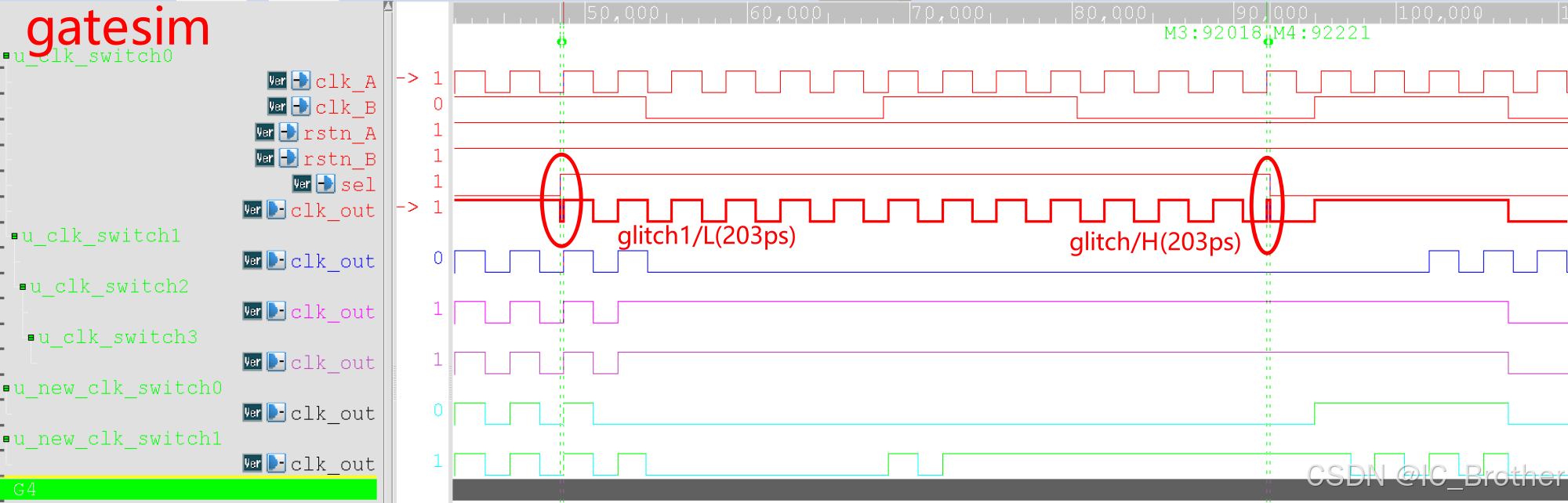

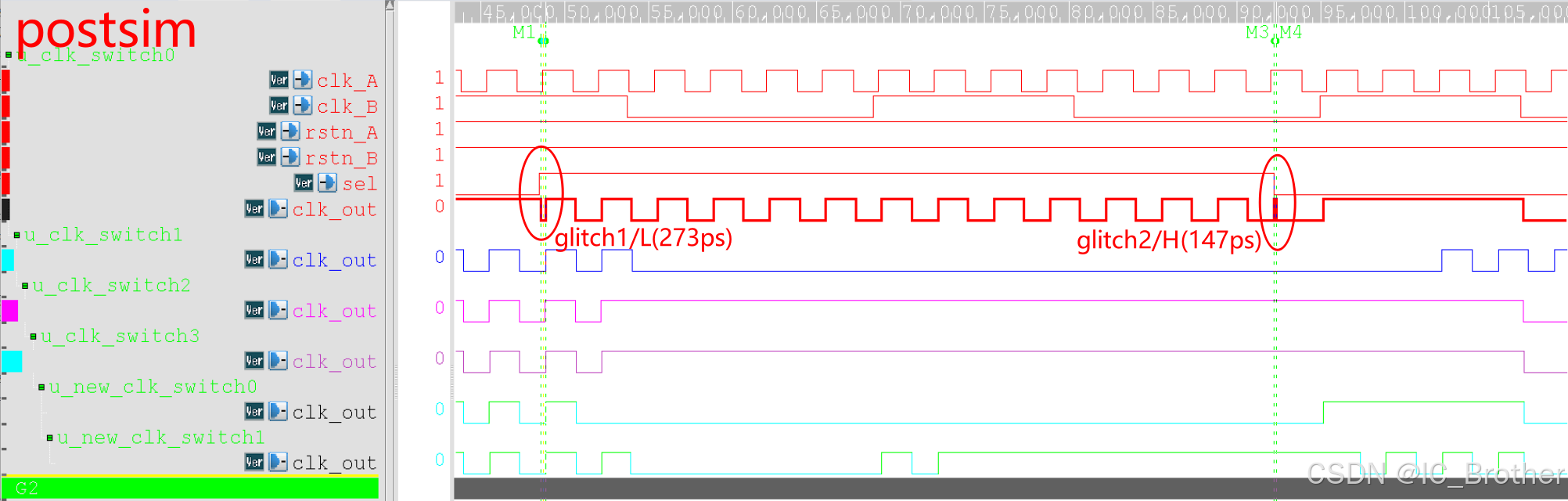

项目前仿真/pre,门级仿真/gate以及DC综合后仿/post的波形图如下所示:(Figure 8~10)

值得注意的是,在合适的testbench setting时,即使是在前仿阶段,都能很明显的发现只采用普通MUX会产生glitch,而在后仿阶段,由于门级延迟会受PVT的影响,glitch则会展现出不均一性,即glitch的宽度会随之变化,这无疑会造成系统的不稳定性。

3)仿真结果

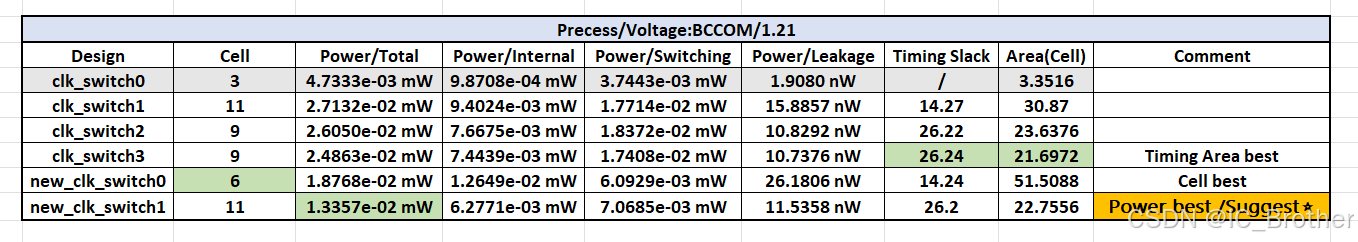

对上述glitch_free_clock_switch采用相同的DC综合条件,对比面积/Cell/Timing/Power报告,汇总数据如下:

- 其中,CLK_Switch3面积和Timing 裕量最优,New_CLK_Switch0 Cell数最优;

- 而综合面积/功耗/Timing等参数,当前New_CLK_Switch1的结构最为推荐,该结构将传统的使能逻辑插入到同步链中,有效节省功耗的同时,尽可能的留下裕量;

总结

项目学习目的:

(1)熟练掌握glitch_free_clock_switch的基本结构及原理;

(2)学习时钟切换相关基本原理;

(3)熟悉 Verilog HDL仿真以及相关流程工具;

参考资料

[1] S. Zeidler, O. Schrape, A. Breitenreiter and M. Krstić, “A Glitch-free Clock Multiplexer for Non-Continuously Running Clocks,” 2020 23rd Euromicro Conference on Digital System Design (DSD), Kranj, Slovenia, 2020, pp. 11-15, doi: 10.1109/DSD51259.2020.00013.

[2] H. Wang et al., “A configurable fault-tolerant glitch-free clock switching circuit,” 2013 IEEE 56th International Midwest Symposium on Circuits and Systems (MWSCAS), Columbus, OH, USA, 2013, pp. 537-540, doi: 10.1109/MWSCAS.2013.6674704.

[3] Jovanovi, Borisav and Milunka Damnjanovi. “Glitch Free Clock Switching Techniques in Modern Microcontrollers.” (2014).

[4] https://www.eetimes.com/techniques-to-make-clock-switching-glitch-free/

——glitch_free_clock_switch的实现(无毛刺时钟切换电路简介及Verilog实现)&spm=1001.2101.3001.5002&articleId=144461039&d=1&t=3&u=196fd3ea0eb1409f9556fa4281da666c)

7048

7048

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?