本文用来总结在学习过程中碰到的APB总线问题,针对APB总线的IP模块进行了一部分的学习总结

以下内容不一定正确,若有意见欢迎评论讨论。

CoreAPB3

功能:

-

总线接口:CoreAPB3提供了与APB总线进行通信的接口,使得处理器可以通过APB总线对各种外设进行配置和数据交互。

-

外设连接:它作为外设IP核与处理器之间的桥梁,允许将多个外设模块(如UART、GPIO、SPI等)连接到处理器,实现系统级的功能集成。

-

数据传输控制:负责管理和控制数据在处理器与外设之间的传输,包括数据的读写操作、地址译码等,确保数据的正确传输和处理。

-

时钟和复位管理:对连接到APB总线的外设进行时钟和复位信号的管理,保证外设在正确的时钟域和复位状态下工作。

作用:

-

作为总线接口IP核:在基于FPGA的系统中,CoreAPB3可以作为一个关键的总线接口IP核,方便地将各种外设IP核集成到系统中,实现与处理器的高效通信。

-

提高系统集成度:通过使用CoreAPB3,可以将多个外设模块连接到同一个APB总线上,从而提高系统的集成度和资源利用率,减少硬件设计的复杂度。

-

简化系统设计:它提供了一种标准化的接口方式,使得外设模块的设计和集成更加简单和规范,降低了系统设计的难度和开发周期。

-

便于系统扩展和维护:由于CoreAPB3遵循APB总线协议,当需要添加新的外设或对现有外设进行升级时,只需按照APB协议进行相应的配置和修改,而无需对整个系统进行大规模的改动,提高了系统的可扩展性和可维护性。

应用场景:

-

FPGA开发:在FPGA项目中,当需要将多个外设与处理器连接时,CoreAPB3可以作为一个高效的总线接口解决方案,实现系统的快速搭建和功能集成。

-

嵌入式系统:在嵌入式系统设计中,CoreAPB3可用于连接微控制器(MCU)或微处理器(MPU)与各种外设,如传感器、存储器、通信模块等,构建完整的嵌入式应用系统。

-

SoC设计:在系统级芯片(SoC)的设计中,CoreAPB3可以作为内部总线的一部分,用于连接处理器核心与片上外设,实现片上系统的高效通信和资源管理

基本原理:

APB(Advanced Peripheral Bus)总线是一种用于连接和管理微控制器或系统芯片(SoC)中的低速外设的简单总线协议。CPU和外设之间通过APB总线进行交互的过程可以分为以下几个阶段:

1. 地址阶段(Address Phase)

-

主设备发起请求:CPU(作为APB主设备)首先确定要访问的外设(从设备)以及具体的寄存器地址。这个地址是通过APB总线的地址总线(PADDR)传输的。

-

选择从设备:APB总线上的所有从设备都会接收到这个地址信号,但只有地址匹配的从设备会被选中。选中的从设备通过片选信号(PSEL)被激活。

-

设置控制信号:CPU还会通过控制信号(如PWRITE)表明是读操作还是写操作。

2. 数据阶段(Data Phase)

-

写操作:

-

如果是写操作,CPU将数据放在数据总线(PDATA)上,并通过PWRITE信号指示这是一个写操作。

-

被选中的从设备在接收到数据后,会将其存储到指定的寄存器中。

-

从设备通过PROT信号确认接收到了数据。

-

-

读操作:

-

如果是读操作,CPU通过PWRITE信号指示这是一个读操作。

-

被选中的从设备将指定寄存器中的数据放到数据总线(PDATA)上。

-

CPU从数据总线上读取数据,并通过PROT信号确认接收到了数据。

-

3. 确认阶段(Transfer Termination)

-

传输完成:当数据传输完成后,从设备会通过PREADY信号通知CPU数据已经准备好(对于读操作)或者已经接收到数据(对于写操作)。

-

释放总线:CPU在确认传输完成后,会释放总线,以便其他设备可以使用总线进行通信。

示例过程

假设CPU要读取一个连接到APB总线上的UART外设的接收缓冲寄存器中的数据:

-

地址阶段:CPU将UART外设的接收缓冲寄存器的地址放在地址总线上,并通过PSEL信号选中UART外设,同时设置PWRITE信号为读操作。

-

数据阶段:UART外设将接收缓冲寄存器中的数据放到数据总线上,CPU从数据总线上读取数据。

-

确认阶段:UART外设通过PREADY信号通知CPU数据已准备好,CPU确认接收后释放总线。

整个过程确保了CPU能够高效、准确地与外设进行通信,完成数据的读写操作。

如何使用:

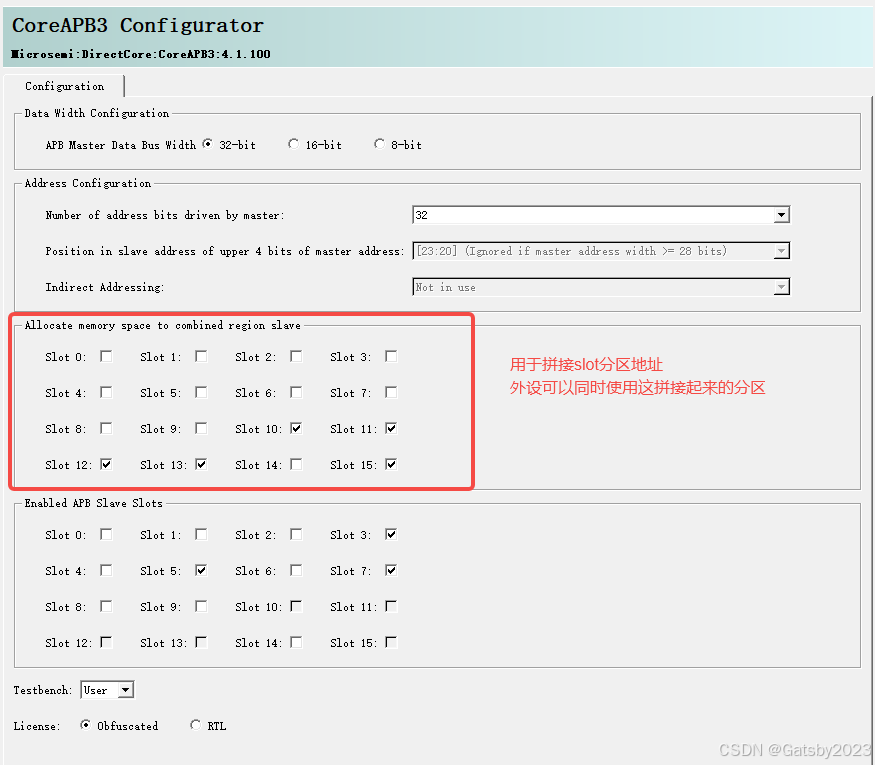

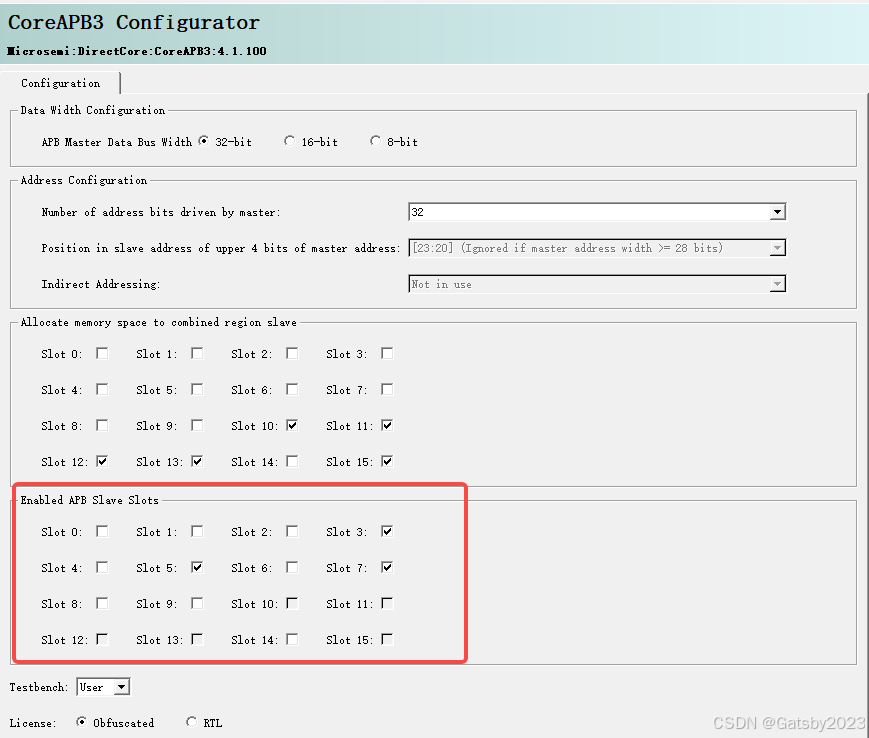

1. 首先介绍配置内容:

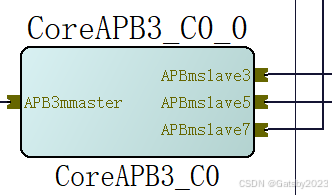

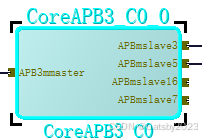

2. 若我们把slot combine在一起,设置完之后会以slot16的形式呈现出来

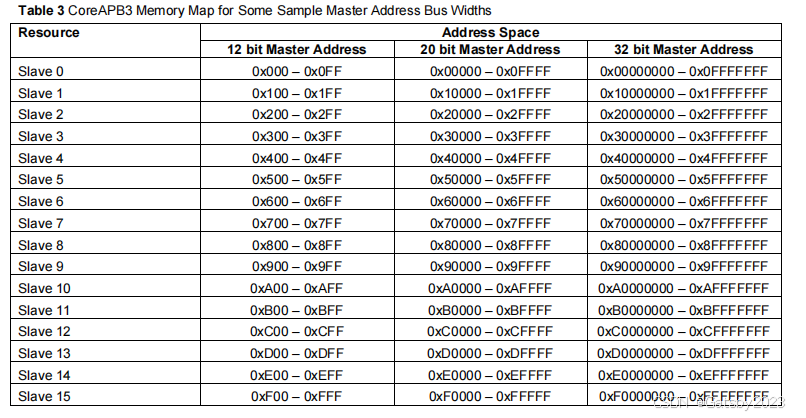

3. 每个slot的地址是什么呢?如何使用并使用这几个分区呢?

当我们需要使用3,5, 7 的slot的时候。我们就在上图进行勾选,然后在MCU的代码体现这些地址,这样我们的APB SLAVE才能和master正式连接在一起。

具体slot地址如下:

代码示例:

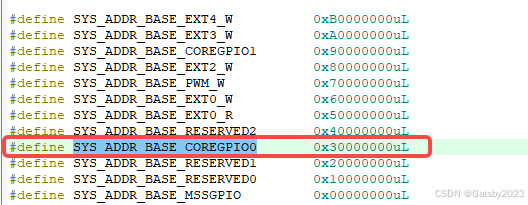

比如slot3 就是以下的基地址,我们的

我们设定这个基地址为CoreGPIO

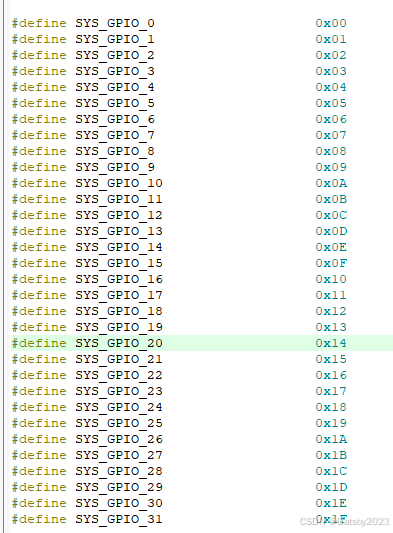

因此我们外设偏移量为:

eg:

![]()

总结:

APB就是连接外设和MCU的桥梁,我们通过APB 总线可以实现外设,FPGA模块和MCU的通信连接,当我们需要读写寄存器的时候通过APB就可以简单轻松的访问外设。

2085

2085

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?