目录

1. 实验目的:

标准情况下,zynq芯片使用的过成中,默认只会使用一个cpu。我们这个实验的过程中,就是要同时调用这两个核进行信息交互,在完成不带中断的交互之后,我们会增加软中断和硬中断,进行相应的中断信息发送测试。CPU0 和 CPU1 中独立跑不同的应用程序,发挥双核的非对称性架构的优势和性能。也为了学习ZYNQ如何在JTAG下载之外,使用flash或者sd卡加载程序。

2. 实验原理介绍:

2.1 什么是AMP?

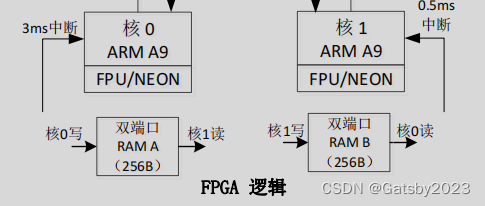

2.2 实验的功能框图:

3. 实验流程:

3.1 无中断的连续通信(1)

3.2 软中断通信(2)

3.3 硬中断通信(3)

3.4 AXI_LITE双口ram的建立(4)

4. 实验过程

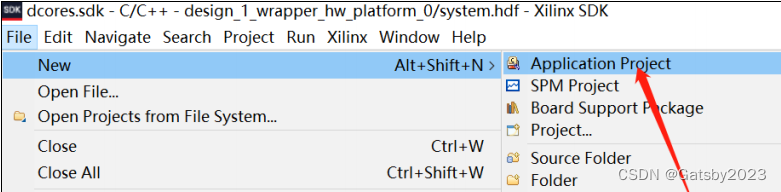

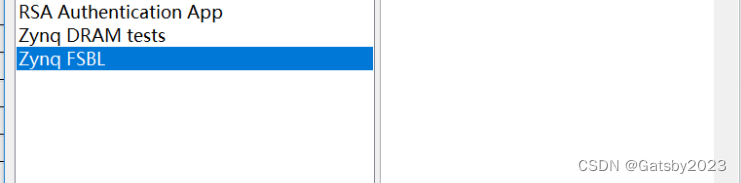

4.1 创建amp环境及CPU的FSBL

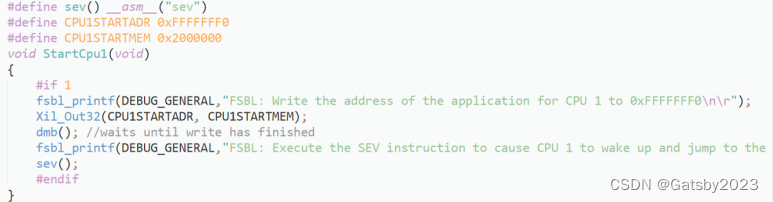

这段代码定义了一个名为 sev 的宏。在这个宏的定义中,使用了内联汇编 __asm__("sev"),这表示在这个宏被调用时,将执行 ARM 处理器的 SEV 汇编指令。

SEV 指令是 ARM 处理器的一条指令,用于发送事件。在多处理器系统中,SEV 指令通常用于唤醒其他处理器或核心,告知它们有事件需要处理。

Xil_Out32() 是用于在Xilinx的软件开发工具中进行寄存器写入的函数。具体来说,Xil_Out32() 是用于写入32位无符号整数(32位数据)到指定地址的函数。这里面的意义其实就是在告诉Cpu他对应的应用程序在ddr的哪段内存里面。

这个函数常用于裸机编程、嵌入式系统中,特别是在使用Xilinx的FPGA和SoC开发工具时。通过使用这个函数,可以直接向特定地址的寄存器写入数据,用于配置硬件、控制外设等。

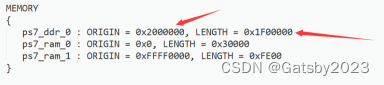

这个工程中我们这端启动程序的起始地址再0x2000000,我们把这个地址写入CPU的起始地址中。

在 ARM 架构中,dmb() 指令用于实现数据同步的内存屏障。dmb 是 "Data Memory Barrier" 的缩写,它确保在 dmb 指令之前的内存访问操作完成后,再执行 dmb 之后的内存访问操作。具体而言,dmb()

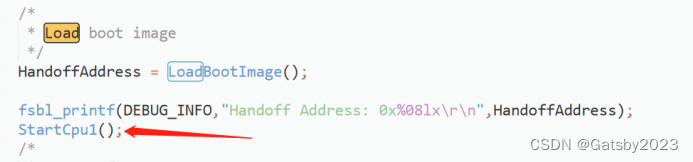

完成以上的内容之后,我们在镜像位置加入如图的代码:

4.2 创建CPU0的app应用程序

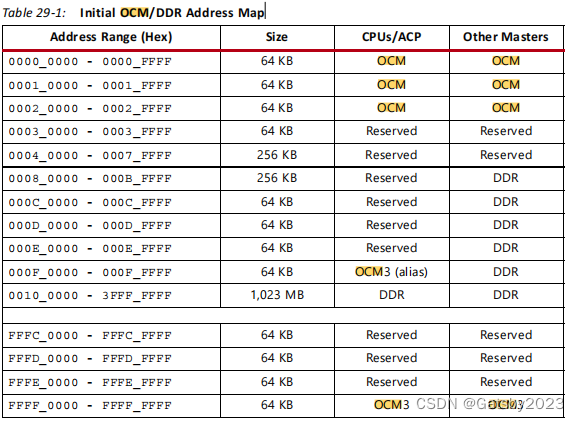

在UG585文档中,我们可以看到OCM = on chip memory片上内容,不需要任何总线的高速内存

我们在本次实验中使用OCM3,我们在此处设立了特定的共享变量

COMM_VAL (*(volatile unsigned long *)) (0xFFFF_0000))

之后修改app工程中的main函数,代码如下:

#include <stdio.h>

#include "platform.h"

#include "xil_printf.h"

#define COMM_VAL (*(volatile unsigned long *)(0xFFFF0000))

int main()

{

COMM_VAL=0;

//Disable cache on OCM

Xil_SetTlbAttributes(0xFFFF0000,0x14de2);

while(1){

print("Hello World cpu0 \n\r");

COMM_VAL =1;

while(COMM_VAL == 1){

}

}

return 0;

}我们在执行的过程中,修改共享变量的值,并且让CPU1因为数值的修改卡死在while循环中,我们后续要在CPU2中也对这个共享数值进行修改,让CPU0走出这个死循环。

一般来说,我们的ZYNQ芯片上,我们通常把一些常用的重要的变量存在OCM中,我们把一app应用程序存在DDR中,因此针对这个问题,我们需要对每个cpu使用的ddr地址进行一定的分配。

4.3 创建CPU1的app应用程序

创建的过程同上,但是代码发生改变,我们还需要注意的是,ddr的地址也要和CPU0定义的地址有所区分。

代码:

这里看代码可以看见我们在循环对共享变量进行变更,来实现arm核之间的非堆成操作,还有一部分的信息交互。

#include <stdio.h>

#include "platform.h"

#include "xil_printf.h"

#define COMM_VAL (*(volatile unsigned long *)(0xFFFF0000))

int main()

{

//Disable cache on OCM

Xil_SetTlbAttributes(0xFFFF0000,0x14de2);

while(1){

while(COMM_VAL == 0){

}

print("Hello World cpu1 \n\r");

sleep(2);

COMM_VAL=0;

}

return 0;

}ddr地址改为:

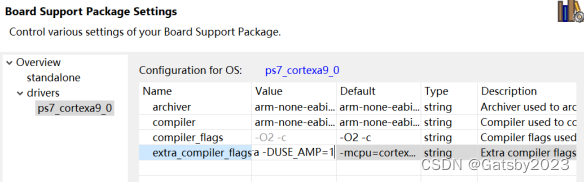

4.4 设置CPU1的模式为AMP非对称模式

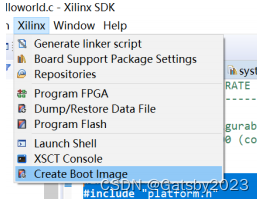

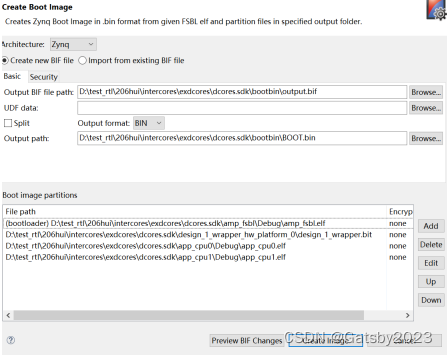

4.5 生成boot.bin文件

按照以下步骤:

1. 在我们的工程目录新建一个bootbin文件夹方便储存

2. 生成boot image

3. 之后添加 我们的amp_fsbl文件 , vivado生成的block design内的bitstream文件

以及我们的cpu0和cpu1的文件。这样 FSBL 会连续加载 CPU0 和 CPU1 的代码到 DDR 中,按照 lscript.ld 约 束进行地址空间划分。

4. 之后sd卡放到办卡上,选择sd卡启动的方式,就可以看到我们的两个应用程序启动了。

本文介绍了在ZYNQ芯片中,通过非对称多进程(AMP)模式实现两个CPU间的无中断、软中断和硬中断通信,以及使用FSBL和BOOT.bin进行应用程序加载的实验过程。实验涉及创建AMP环境、配置RAM、内存屏障和OCM的使用,旨在展示双核处理器的性能优化和中断管理技术。

本文介绍了在ZYNQ芯片中,通过非对称多进程(AMP)模式实现两个CPU间的无中断、软中断和硬中断通信,以及使用FSBL和BOOT.bin进行应用程序加载的实验过程。实验涉及创建AMP环境、配置RAM、内存屏障和OCM的使用,旨在展示双核处理器的性能优化和中断管理技术。

4921

4921

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?