第三篇:FPGA实现关键技术与优化

聚焦高速时序、资源复用与信号完整性

1. 时序收敛关键策略

1.1 源同步时序约束

tcl

# Vivado XDC约束示例

create_generated_clock -name spi_sck -source [get_pins clk_gen/CLKOUT] \

-divide_by 1 [get_ports sck]

# 建立时间约束

set_input_delay -clock spi_sck -max 2.0 [get_ports miso]

set_output_delay -clock spi_sck -max 1.5 [get_ports mosi]

# 多周期路径声明

set_multicycle_path 2 -setup -from [get_clocks sys_clk] -to [get_clocks spi_sck]

set_multicycle_path 1 -hold -to [get_clocks spi_sck]

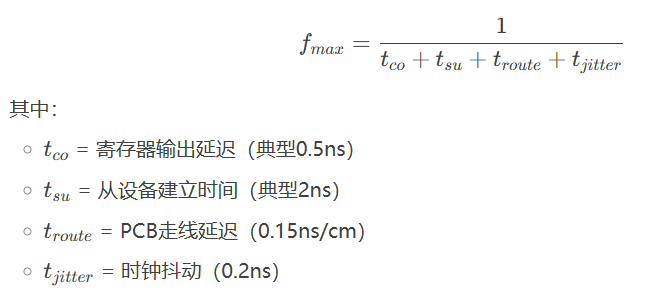

关键参数计算 :

- 最大SCK频率公式 :

1.2 IDDR/ODDR原语应用

verilog

// Xilinx 7系列实现双倍数据率

ODDR #(

.DDR_CLK_EDGE("OPPOSITE_EDGE")

) ODDR_mosi (

.Q(mosi), // 输出到引脚

.C(sck_90), // 90度相移时钟

.CE(1'b1),

.D1(tx_data_even), // 上升沿数据

.D2(tx_data_odd), // 下降沿数据

.R(1'b0),

.S(1'b0)

);

IDDR #(

.DDR_CLK_EDGE("OPPOSITE_EDGE")

) IDDR_miso (

.Q1(rx_data_even), // 上升沿采样

.Q2(rx_data_odd), // 下降沿采样

.C(sck),

.CE(1'b1),

.D(miso), // 输入引脚

.R(1'b0),

.S(1'b0)

);

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1141

1141

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?