一、引言

在数字电路的世界中,组合逻辑电路作为重要的基础组成部分,在现代电子系统里扮演着关键角色。从计算机的运算器、控制器,到日常生活中的数字仪表、通信设备等,都离不开组合逻辑电路的支持。本报告旨在深入探讨组合逻辑电路的基本概念、分析与设计方法、典型电路及其应用,帮助读者全面理解和掌握组合逻辑电路相关知识。

二、组合逻辑电路基本概念

2.1 定义与特点

组合逻辑电路是由门电路组合而成的数字电路,其特点是在任何时刻,电路的输出状态仅取决于当时的输入状态,而与电路过去的状态无关。也就是说,组合逻辑电路不存在记忆功能,它对输入信号进行即时处理并输出结果。例如,简单的加法器电路,输入两个二进制数,立即输出它们相加的结果 。

2.2 逻辑门基础

逻辑门是构建组合逻辑电路的基本单元,常见的逻辑门包括与门、或门、非门、与非门、或非门、异或门等。以与门为例,其逻辑功能为只有当所有输入都为高电平时,输出才为高电平,逻辑表达式为

Y=A⋅B

;或门则是只要有一个或多个输入为高电平,输出就为高电平,逻辑表达式为

Y=A+B

;非门实现逻辑取反功能,

Y=A

。这些逻辑门通过不同的组合方式,可以实现各种复杂的逻辑功能。

三、组合逻辑电路分析方法

3.1 分析步骤

- 确定输入输出变量:明确电路的输入信号和需要实现的输出功能,确定输入输出变量并进行命名。

- 写出逻辑表达式:根据电路中逻辑门的连接关系,从输入到输出逐步推导,写出输出变量关于输入变量的逻辑表达式。例如,对于一个由与门和或门组成的电路,先根据与门的逻辑关系写出中间变量的表达式,再结合或门得出最终输出表达式。

- 化简逻辑表达式:利用逻辑代数的基本公式和定理,如摩根定律、分配律、吸收律等,对逻辑表达式进行化简,以得到最简形式。最简表达式可以减少电路中逻辑门的数量,降低电路成本,提高电路可靠性。例如,对表达式

Y=AB+AB

,根据分配律可化简为Y=A(B+B)=A

。

- 列出真值表:根据输入变量的所有可能取值组合,代入化简后的逻辑表达式,计算出相应的输出值,列出真值表。真值表能够直观地展示电路输入与输出之间的逻辑关系 。

- 分析逻辑功能:通过观察真值表,总结电路实现的逻辑功能,判断其是否满足设计要求。

3.2 示例分析

假设有一个组合逻辑电路,由两个与门、一个或门组成,输入变量为

A

、

B

、

C

,输出变量为

Y

。其连接关系为:

A

和

B

连接到一个与门,

B

和

C

连接到另一个与门,两个与门的输出连接到或门。

首先,根据电路连接写出逻辑表达式:

Y=AB+BC

。

然后,利用逻辑代数公式化简,该表达式已是最简形式。

接着,列出真值表:

当输入变量

A

、

B

、

C

取值组合分别为:

-

A=0,B=0,C=0

时,Y=0

;

-

A=0,B=0,C=1

时,Y=0

;

-

A=0,B=1,C=0

时,Y=0

;

-

A=0,B=1,C=1

时,Y=1

;

-

A=1,B=0,C=0

时,Y=0

;

-

A=1,B=0,C=1

时,Y=0

;

-

A=1,B=1,C=0

时,Y=1

;

-

A=1,B=1,C=1

时,Y=1

。

最后,分析上述取值组合可知,该电路实现的逻辑功能为:当

A

和

B

同时为 1,或者

B

和

C

同时为 1 时,输出

Y

为 1,否则

Y

为 0 。

四、组合逻辑电路设计方法

4.1 设计步骤

- 逻辑抽象:根据实际问题的要求,确定输入输出变量,并对它们的逻辑状态进行赋值,明确输入与输出之间的逻辑关系。例如,设计一个判断两个数大小的电路,输入为两个数对应的二进制信号,输出为表示大小关系的信号(如大于、小于、等于)。

- 列真值表:根据输入输出变量的逻辑关系,列出所有可能的输入取值组合及其对应的输出值,形成真值表。

- 写逻辑表达式:根据真值表,利用最小项表达式或最大项表达式的方法,写出输出变量关于输入变量的逻辑表达式。最小项表达式是将真值表中输出为 1 的最小项相加,最大项表达式是将输出为 0 的最大项相乘。

- 化简逻辑表达式:运用逻辑代数的化简方法,对逻辑表达式进行化简,得到最简形式,以简化电路结构。

- 画逻辑电路图:根据化简后的逻辑表达式,选择合适的逻辑门,画出实现该逻辑功能的组合逻辑电路图。

4.2 示例设计

设计一个三人表决器电路,三人分别用

A

、

B

、

C

表示,同意为 1,不同意为 0,当有两人或两人以上同意时,表决通过,输出

Y

为 1,否则

Y

为 0 。

- 逻辑抽象:输入变量为

A

、B

、C

,输出变量为Y

,同意对应逻辑 1,不同意对应逻辑 0,表决通过Y

为 1,未通过Y

为 0 。

- 列真值表:

|

A

|

B

|

C

|

Y

|

|----|----|----|----|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

- 写逻辑表达式:由真值表可得最小项表达式

Y=ABC+ABC+ABC+ABC

。

- 化简逻辑表达式:

LaTex error

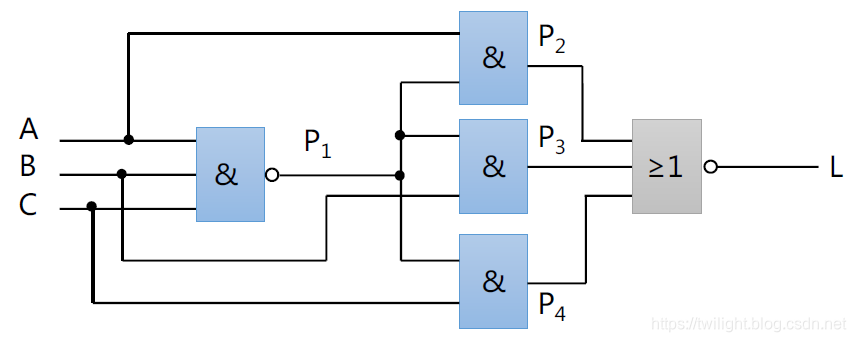

- 画逻辑电路图:根据化简后的表达式

Y=AB+AC+BC

,使用三个与门和一个或门即可画出三人表决器的逻辑电路图。

五、典型组合逻辑电路

5.1 编码器

编码器是将特定意义的信息(如数字、字母、符号等)转换为二进制代码的组合逻辑电路。常见的编码器有二进制编码器和优先编码器。以 3 位二进制编码器为例,它有 8 个输入信号(

I0−I7

),3 个输出信号(

Y2

、

Y1

、

Y0

),其功能是将 8 个输入中的某一个有效信号转换为对应的 3 位二进制代码。优先编码器则在多个输入信号同时有效时,优先对优先级高的信号进行编码。

5.2 译码器

译码器是编码器的逆过程,它将二进制代码翻译成特定的信息或控制信号。常见的译码器有二进制译码器、二 - 十进制译码器和显示译码器。二进制译码器将

n

位二进制代码转换为

2n

个输出信号;二 - 十进制译码器将 4 位二进制代码(BCD 码)转换为 10 个输出信号,对应十进制的 0 - 9;显示译码器则用于驱动数码管,将二进制代码转换为数码管显示所需的控制信号,实现数字的显示。

5.3 加法器

加法器是实现二进制数加法运算的组合逻辑电路,分为半加器和全加器。半加器只能实现两个 1 位二进制数的相加,不考虑来自低位的进位;全加器则可以实现两个 1 位二进制数相加,并考虑来自低位的进位。多个全加器级联可以构成多位加法器,实现多位数的加法运算,在计算机的运算器中起着关键作用 。

5.4 数据选择器

数据选择器是从多个输入数据中选择一个作为输出的组合逻辑电路,也称为多路选择器。它有多个数据输入端、地址输入端和一个数据输出端,通过地址输入信号来选择相应的数据输入信号输出。例如,4 选 1 数据选择器有 4 个数据输入端(

D0−D3

)、2 个地址输入端(

A1

、

A0

)和 1 个输出端(

Y

),根据

A1

、

A0

的取值组合,选择

D0−D3

中的一个数据输出。

六、组合逻辑电路实验

6.1 实验目的

通过实际操作,加深对组合逻辑电路基本概念、分析与设计方法的理解,掌握逻辑门、典型组合逻辑电路的使用方法,提高动手能力和解决实际问题的能力。

6.2 实验器材

数字实验箱、74 系列集成逻辑门芯片(如 74LS00 与非门、74LS02 或非门、74LS04 非门等)、74 系列典型组合逻辑电路芯片(如 74LS138 译码器、74LS153 数据选择器等)、导线、万用表等。

6.3 实验内容与步骤

- 逻辑门功能测试:将不同的逻辑门芯片插入实验箱,按照芯片引脚图连接输入信号(可通过实验箱的逻辑开关提供),测量输出信号(用实验箱的指示灯或万用表测量),验证逻辑门的逻辑功能,并记录测试结果。

- 组合逻辑电路分析实验:搭建一个给定的组合逻辑电路,如前面示例中的组合逻辑电路,按照组合逻辑电路分析步骤,写出逻辑表达式、化简、列出真值表,并与实验测量结果进行对比,验证分析的正确性。

- 组合逻辑电路设计实验:根据设计要求,如设计一个四人表决器(三人或三人以上同意时表决通过),按照设计步骤完成逻辑抽象、列真值表、写逻辑表达式、化简、画逻辑电路图,并在实验箱上搭建电路,测试电路功能,观察输出是否满足设计要求 。

6.4 实验结果与分析

在逻辑门功能测试中,各逻辑门的输出与理论逻辑功能相符,验证了逻辑门的正确性。在组合逻辑电路分析实验中,通过实验测量得到的真值表与理论分析的真值表一致,说明对电路的分析是正确的。在组合逻辑电路设计实验中,搭建的四人表决器电路能够实现设计要求的逻辑功能,表明设计方法和电路搭建是正确的。但在实验过程中,也发现了一些问题,如电路连接错误导致输出异常,通过仔细检查和重新连接解决了问题,这也提醒我们在实验中要认真、细心 。

七、组合逻辑电路的应用与发展趋势

7.1 应用领域

组合逻辑电路广泛应用于计算机系统、通信系统、自动化控制、仪器仪表等众多领域。在计算机中,运算器中的加法、减法、乘法等运算通过组合逻辑电路实现;在通信系统中,编码器、译码器用于数据的编码和解码,实现信号的传输和处理;在自动化控制系统中,组合逻辑电路用于逻辑判断和控制信号的生成,实现对设备的自动控制;在仪器仪表中,组合逻辑电路用于数据的处理和显示控制 。

7.2 发展趋势

随着电子技术的不断发展,组合逻辑电路也在朝着高速、低功耗、集成化、智能化的方向发展。高速化要求电路能够在更短的时间内完成逻辑运算,以满足现代高速数字系统的需求;低功耗设计对于便携式电子设备至关重要,可以延长设备的电池续航时间;集成化使得更多的逻辑功能能够集成在一个芯片上,减小电路体积,提高可靠性;智能化则是将人工智能等技术与组合逻辑电路相结合,实现更复杂、更智能的逻辑功能 。

八、结论

通过对组合逻辑电路的学习、分析、设计和实验,我们深入理解了组合逻辑电路的基本概念、分析与设计方法,掌握了典型组合逻辑电路的原理和应用。组合逻辑电路作为数字电路的重要组成部分,在现代电子系统中具有不可替代的作用。在实际应用中,我们可以根据具体需求,运用所学知识设计出满足要求的组合逻辑电路。同时,随着电子技术的不断发展,组合逻辑电路也将不断创新和发展,我们需要持续关注其发展动态,不断学习和掌握新的知识和技术,以适应未来电子技术发展的需求 。

1173

1173

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?