管理共享的资源(Shared Resources)

某些LabVIEW FPGA模块应用包含可被FPGA VI中的多个对象(例如,函数或子VI)访问的共享资源。下列为可能的共享资源:

- 数字输出线(Digital output lines

- 模拟数据线(Analog lines

- 寄存器项(Register items

- 存储器项(Memory items

- FIFO

- 握手项(Handshake items

- 中断数据线(The interrupt line

- 局部变量和全局变量(Local and global variables

- 非重入子VI(Non-reentrant subVIs

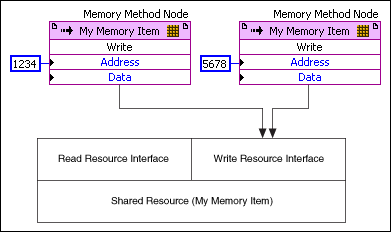

每个共享资源包含一个或多个资源接口(interfaces)。资源接口在对象和共享资源间通信,如下图所示。

在FPGA VI程序框图中2个或多个对象同时请求通过同一个资源接口访问同一个共享资源将产生资源冲突(resource contention)。在上面的示意图中未发生资源冲突,因为对象请求通过两个不同的资源接口访问该共享资源。

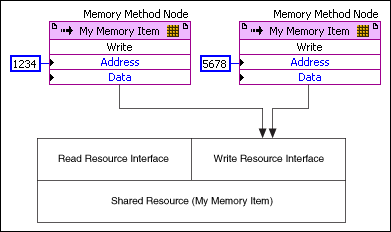

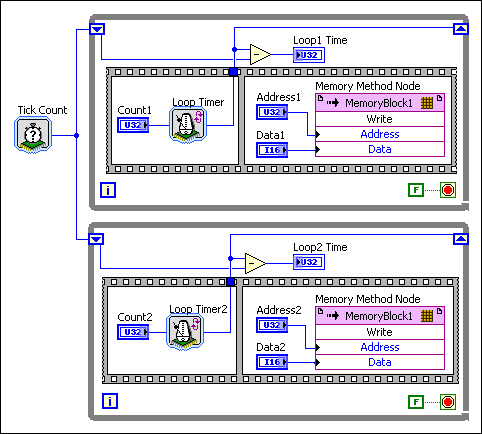

但在下列示意图中,两个存储器方法节点请求通过同一个资源接口访问同一个共享资源(我的存储器项)。如两个存储器方法节点同时请求访问共享资源将产生资源冲突。

通过仲裁(Arbitration)避免资源冲突

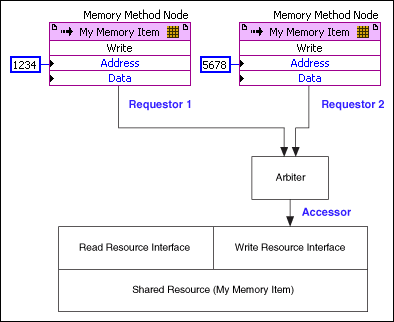

为避免资源冲突,FPGA模块提供了当多个对象同时请求访问资源时的仲裁选项,用于判定可访问资源的对象。用户选择的仲裁选项决定了LabVIEW是否使用仲裁器(arbiter)。可选的仲裁选项随资源变化。

请求方(requestors)是指通过资源接口请求访问资源的对象。仲裁器允许请求方对资源的访问后,该请求方转为访问方(accessor)。如下图所示。

始终仲裁(Always Arbitrate)

即使仅有一个请求方请求访问,带有始终仲裁选项的资源接口也会一直使用仲裁器。始终仲裁仲裁器采用公正的轮询机制,能够确保按顺序访问共享资源。在下一个等待的请求方成为访问方之前,判定器不允许当前请求方再次成为访问方。因此,同步请求方超出一个时将产生抖动。

需要单个请求方通道与多个请求方通道同步时,选择始终仲裁选项。关于同步通道的信息,见启用仲裁的定时FPGA VI。

仅在多个请求时仲裁(Arbitrate if Multiple Requestores Only)

(默认选项)

带有仅在有多个请求方时仲裁选项的资源接口仅在FPGA VI包含不止一个请求方时使用仲裁器。如果资源接口具有多个请求方,即使请求方未同步,LabVIEW也会生成仲裁电路。如果共享资源在整个FPGA VI层次结构中仅包含一个请求方,使用仅在有多个请求方时仲裁仲裁选项可节省FPGA VI的时间和空间。

从不仲裁(Never Arbitrate)

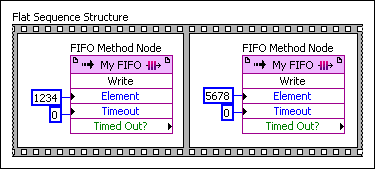

如果您为资源接口选择从不仲裁选项,则LabVIEW不会添加仲裁组件,显著节约了FPGA资源。除了节省资源,从不仲裁选项还使一些FPGA I/O和FIFO函数可在单时钟周期内执行。但对于多个请求方的情况,多个信号将被合并为一个信号,从而导致产生额外的逻辑占用。要使用从不仲裁选项,您必须保证按顺序访问FPGA VI数据流中的资源接口,如下图所示。

更改仲裁选项

修改FPGA I/O项的仲裁选项

Properties>>Category>>Advanced Code Generation

修改FPGA FIFO项的仲裁选项

Properties>>Category>>Interfaces

避免因资源冲突引起的抖动(Jitter)

如循环中的请求方在转换为访问方时由于一个或多个其他请求方引起的资源冲突发生延迟,将会产生抖动且延时随每个循环改变。例如,假设有一个执行以固定频率采样模拟输入信号的定时While循环的应用程序。每次FPGA I/O节点执行时,节点发出模拟输入资源请求后立即成为访问方。如添加一个采样同一个模拟输入资源的While循环,这两个FPGA I/O节点可能同时请求访问模拟输入资源。此时判定器会延时其中一个访问方,并允许另一个请求方成为访问方。由于资源访问不能立即响应发出的请求,所以此延时将引入抖动。

为避免抖动,设计FPGA VI程序框图时应确保:

- 请求方不会在共享资源不可用时访问共享资源。

- 两个请求不会在同一个时钟周期内发生。

在VI的两个独立部分使用共享子VI或通过并行循环访问资源接口时经常产生抖动,如下列程序框图所示。

上面程序框图中的VI包含并行的While循环,两个循环均写入存储器块1(MemoryBlock1)。根据每个循环中剩余代码需要的执行时间,两个存储器方法节点(Memory Method Nodes)可能同时发出访问MemoryBlock1的请求,导致两个循环均产生抖动并产生数据不确定性。在上述范例中,Count1和Count2间隔10~15个时钟滴答时产生抖动。

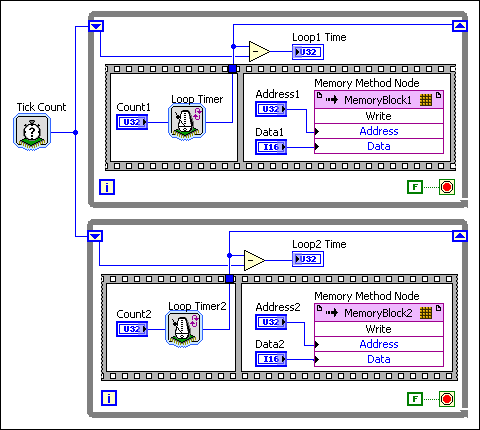

对单个资源的访问方数量越多,产生抖动的可能性越大。但如果能避免同时发出请求,无论潜在的访问方数量多少,判定器的延时均为常量。为避免上述范例中的多个访问方,可创建另一个存储器项(MemoryBlock2)并写入至底层While循环,如下列程序框图所示。

启用仲裁的定时FPGA VI

并非所有的仲裁选项的执行时间都相同。如要同时访问多个同一类型的资源,必须为每个资源选择采用相同执行时间的仲裁选项。

使用FPGA I/O

通过FPGA终端上的输入和输出连接FPGA 终端(FPGA targets)至其他设备。FPGA I/O资源为FPGA终端的固定单元,可用于在系统的不同部分间传递数据。每个FPGA I/O资源均具有特定的类型,例如数字(digital)或模拟(analog)。一个FPGA终端可能具有多个相同或不同类型的I/O资源。

-

Digital I/O:

Digital Input Resources read Digital Output Resources write Digital Input and Output Resources read & write

三态数字I/O资源(tristate digital I/O resources)称为数字输入和输出资源。

通过已配置“设置输出启用”方法的FPGA I/O方法节点(FPGA I/O Method Node configured with the Set Output Enable)改变数据流的方向。连线TRUE值至Enable input,以配置三态I/O (tristate I/O)资源为输出资源。连线FALSE值至Enable input,以配置三态I/O资源为输入资源。(通常默认的方向为输入。)

-

Analog I/O

创建FPGA I/O项

New>>FPGA I/O

配置FPGA I/O项

-

在项目浏览器窗口(Project Explorer Window)配置FPGA I/O项: Properties>>Category>>General

-

配置FPGA I/O Node中的FPGA I/O项: Properties>>Category

使用FPGA I/O节点

新建一个VI或打开一个FPGA终端下已包含FPGA I/O项的已有VI。可在项目浏览器窗口单击FPGA I/O项并拖曳其至程序框图,以创建一个新的配置了该FPGA I/O item的FPGA I/O Node。

在FPGA I/O和FPGA终端上执行操作

FPGA I/O Method Nodes可用于在FPGA I/O项和C系列模块中调用方法或动作。在某些情况下,也可在FPGA终端上调用方法。可用的方法由选定的FPGA终端、FPGA I/O项或C系列模块确定。

创建和配置FPGA I/O Method Node:Add FPGA I/O Method Node -> Select Item -> Select Method

设置和获取FPGA I/O和FPGA终端的属性(Properties)

Add FPGA I/O Property Node -> Select Item -> Property -> Select Property

控制I/O上电状态(I/O Power-On States)

注:如要实现本主题涉及的技术,必须使用带有闪存(flash memory,是一种以电信号记录和读取数据的非易失性存储介质,其中的数据可多次读取或擦除、写入)的FPGA终端。

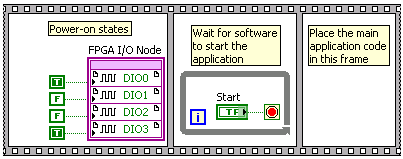

系统上电时,应用可能需要FPGA终端的I/O设置为已知的值。可创建一个FPGA VI并配置FPGA终端,以设置FPGA终端的上电状态。

必须对FPGA VI进行编程,以便程序框图无需依赖主控VI便可设置输出状态。例如,可在顺序结构的第一个帧内放置数字和模拟输出函数。然后将余下的LabVIEW代码放在顺序结构的后续帧内,如以下程序框图中所示。然后配置FPGA VI在其被载入FPGA后立即执行。编译FPGA VI并将其下载至FPGA终端的闪存,然后配置FPGA终端在FPGA终端上电时,自动从闪存载入FPGA VI。FPGA终端上电后,FPGA VI将从闪存载入到FPGA,然后立即开始执行。FPGA VI顺序结构的第一个帧内的输出函数将设置上电输出状态。

创建触发器(Triggers)和计数器(Counters)

FPGA模块包含执行基本I/O的函数。但是,用户可能有需要自定义I/O功能的应用。将FPGA I/O Node作为构件来创建自定义I/O应用(例如,触发器和计数器)。

Trigger

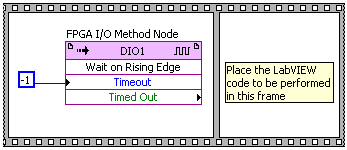

使用FPGA I/O方法节点的等待上升沿(Wait on Rising Edge)方法,可在单个数字输入端等待触发。

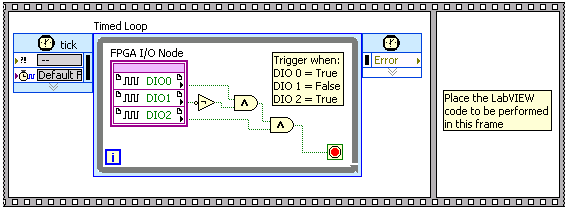

“等待上升沿”方法等待直至数字输入端满足任一用户指定的条件,才会继续。在顺序结构的第一个帧内放置FPGA I/O方法节点,在下一个帧内放置用于该任务的LabVIEW代码,如以下程序框图所示。

FPGA I/O节点可创建更高级的触发事件。例如,仅在多个数字线(multiple digital lines)满足给定条件时执行触发的应用。如下列程序框图所示。

在单周期定时循环(single-cycle Timed Loop)内可放置配置了数字输入资源的FPGA I/O节点,且仅当数字输入满足触发器模式时退出单周期定时循环。在顺序结构的第一个帧内放置单周期定时循环。这个操作与上个范例中对等待上升沿方法的等待操作类似。

使用While循环(While Loop)可以同样的方式执行模拟触发器。在While循环中放置一个配置了模拟输入I/O资源的FPGA I/O节点和比较函数,当模拟输入的值满足可编程条件时触发。

Counter

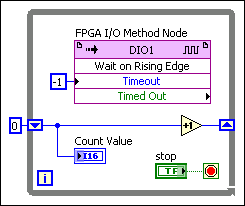

在While循环中使用FPGA I/O方法节点函数可创建简单事件计数器。例如,可使用等待上升沿方法等待数字输入接线端出现上升沿,如以下程序框图所示。

FPGA I/O方法节点检测到边沿后,程序框图的计数器值加1,且将计数器的值存储在While循环的移位寄存器(Shift register)内。使用前面板显示控件(front panel indicator)或局部变量(local variable)可查看计数器的值。

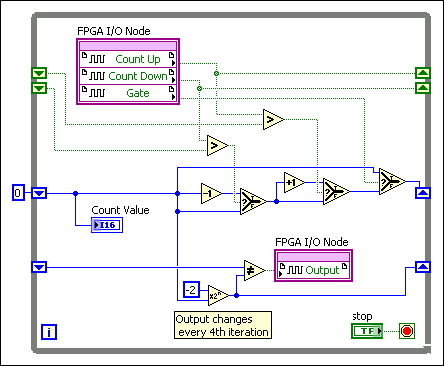

FPGA I/O函数可创建更高级的计数器。例如,应用可能需要带有独立向上计数(count up)、向下计数(count down)及门输入和输出(gate inputs and output)的计数器,如以下程序框图所示。

在上述程序框图中,当Count Up产生上升沿(rising edge)时,计数器的值加1。当Count Down产生上升沿时,计数器的值减1。当Gate为高电平时,Gate将阻止向上计数和向下计数改变计数器的值。Count Up、Count Down和Gate为FPGA终端的指定数字I/O资源名称。计数器的值为4的倍数时输出值无效(asserts)。在LabVIEW代码中可使用简单布尔判定确定计数器为升值计数、减值计数或保持不变。或者使用算术判定确定输出值是否无效。

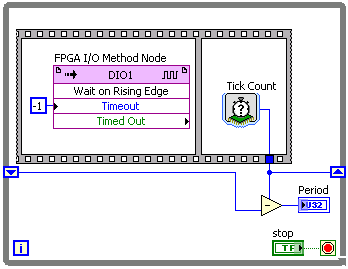

FPGA I/O方法节点可用于测量输入信号的周期,如以下程序框图所示。

使用多个输入通道(Multiple Input Channels)滤波(Filtering)FPGA I/O

使用FPGA数学与分析(FPGA Math & Analysis)选板上的flitering VI滤波FPGA I/O。默认状态下,FPGA filtering VI可使用单输入通道(single input channel)。但可使用filtering VI配置对话框的Number of channels选项,配置用于多输入通道的VI。下列滤波VI支持多个输入通道:

- Butterworth滤波 (Butterworth Filter

- 陷波滤波器 (Notch Filter

- 有理分式重采样 (Rational Resampler

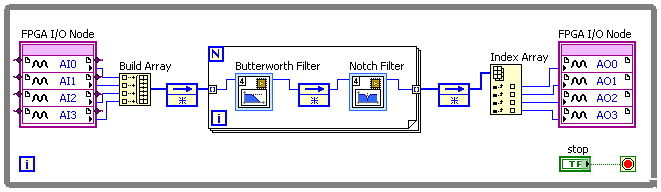

配置用于多个输入通道的FPGA filtering VI时,必须发送每个输入通道至队列中的filter VI。用户可捆绑输入通道至一个数组,并使用For循环确保filtrt VI接收队列中的每个输入通道,如下列程序框图所示。

在上一个程序框图中,4个模拟输入信号通过Butterworth滤波器和一个陷波滤波器。为最大化吞吐量,VI可使用反馈节点(Feedback Nodes)创建一个流水线(pipline)。

4346

4346

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?