FPGA Project组成部分

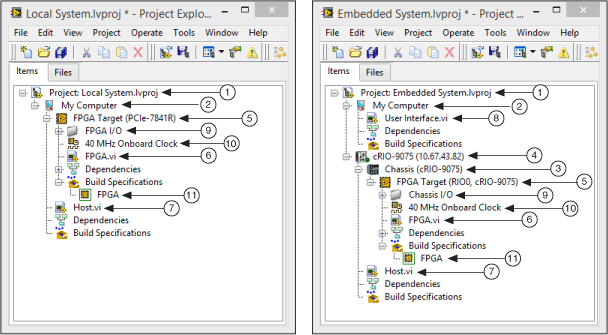

使用项目浏览器窗口(Project Explorer)管理FPGA项目。每个FPGA项目随系统架构的组成部分改变。下图展示了本地系统Local System.lvproj和嵌入式系统Embedded System.lvproj的组成部分。

- LabVIEW Project: LabVIEW项目允许用户在开发计算机上开发应用时,管理VI和终端。LabVIEW项目文件包含对项目中文件的引用、配置信息、部署信息、生成信息等。

- My Computer: 我的电脑(通常称为开发计算机)是开发LabVIEW项目的计算机。开发计算机是指运行支持的Windows平台的计算机,该计算机已安装LabVIEW和LabVIEW FPGA模块。

- RIO Chassis: RIO机箱放置并直接连接FPGA终端的I/O块至可互换的I/O模块,以实现高性能定时、触发和同步。

- Controller: 控制器直接连接RIO机箱,直接或通过网络与开发计算机通信。控制器中包含一个嵌入式处理器,可运行实时操作系统(RTOS)或Windows。

- FPGA Target: FPGA终端是一个可编程芯片,由逻辑块、I/O块和可编程互连资源组成,这些资源用于实现通过LabVIEW FPGA模块设计的数字电路。

- FPGA VI: FPGA VI是加载至FPGA终端并运行的VI。LabVIEW编译工具将FPGA VI转换为电路机制,以重新配置FPGA终端块和互连资源。

- Host VI: 主控VI在控制器上运行,通过编程与FPGA VI通信。可使用主机VI记录数据、控制数据传输的定时及创建将FPGA终端作为组件的系统。

- User Interface VI: 户界面VI在开发计算机上运行,并与主控VI通信。用户界面VI允许用户通过编程,与主控VI的输入控件和显示控件交互。在没有控制器的情况下,用户界面VI将成为主机VI并直接与FPGA VI进行通信。

- I/O: I/O是指FPGA系统的模拟和数字输入/输出。例如,热电偶、RTD、桥传感器、计数器和发生器等。关于支持的I/O的详细信息见指定硬件文档。

- Clock: 时钟通过指定FPGA系统的定时需求,控制FPGA VI的执行频率。如未包含额外的用于控制定时的代码,操作的执行频率由VI数据流确定。多数FPGA终端的默认时钟速率为40 MHz。

- Build Specification: 程序生成规范指定用户编译FPGA VI时,LabVIEW创建哪个选项:仿真导出/编译/源代码发布

在项目浏览器窗口管理FPGA Application

必须为FPGA VI和主控VI创建项目(Project)。

添加FPGA Target至LabVIEW Project

使用FPGA终端创建应用程序前,必须创建一个LabVIEW项目。然后添加FPGA终端至该项目并创建FPGA VI。

通过下列步骤之一添加FPGA终端至项目:(New>>Targets and Devices)

- 在本地用于开发的计算机上添加一个FPGA终端

- 在Real-Time系统中添加一个FPGA终端

- 在远程计算机上添加FPGA终端

创建带有FPGA终端的项目后可执行下列任务:

- 创建FPGA VI

- 添加FPGA I/O

- 添加FPGA clocks

- 添加FPGA register items

- 添加FPGA memory items

- 添加FPGA FIFOs

配置FPGA Targets

通过Properties

添加项(items)至项目浏览器窗口中的FPGA Targets

New>>x

查看比特文件路径(Bitfile Path)

Properties

1865

1865

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?